(54

ЛОГАРИФМИЧЕСКИЙ УСИЛИТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмический преобразователь | 1983 |

|

SU1117660A1 |

| Множительно-делительное устройство | 1987 |

|

SU1543426A1 |

| Вычислительное устройство | 1987 |

|

SU1539798A1 |

| Логарифмический преобразователь | 1979 |

|

SU830421A1 |

| Аналоговое логарифмическое вычислительное устройство | 1982 |

|

SU1095198A1 |

| Четырехквадратное множительно-делительное устройство | 1987 |

|

SU1474686A1 |

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Логарифмический преобразователь | 1986 |

|

SU1363264A1 |

| Логарифмический преобразователь | 1986 |

|

SU1522244A1 |

| Логарифмический преобразователь | 1986 |

|

SU1411784A1 |

t

Изобретение относится к усилительным устройствам с логарифмической амплитудной характеристикой и может быть использовано в аналоговых вычислительных машинах.

Известен логарифмический усилитель , содержащий операционные усилители, логарифмирующие транзистора, масштабные резисторы tl.

Однако это устройство характеризуется сравнительно малой точностью

работы.

Наиболее близким к предлагаемому является логарифмический усилитель, содержащий операционный усилитель, логарифмирующий транзистор и масштабные резисторы, инвертирующий вход операционного усилителя соединен со входом логарифмического усилителя и с коллектором логарифмирующего транзистора, база которого подключена к шине нулевого потенциала, выход операционного усилителя через первый масштабный резистор присоединен к эмиттеру логарифмирующего транзистора, который соединен с первой выходной клеммой логарифмического усилителя, первый вывод второго масштабного резистора соединен с первым выводом третьего масштабного резистора, второй вывод которого подключен к шине нулевого потенциала 2.

Однако недостатком и этого устройства является малая точность работы вследствие падения напряжения на переходе база-эмиттер логарифмирующего транзистора.

Цель изобретения - повышение точности работы.

10

Указанная цель достигается тем, что выход операционного усилителя соединен со вторым выводом второго масштабного резистора, первый вывод которого подключен ко второй выход15ной клемме логарифмического усилителя ..

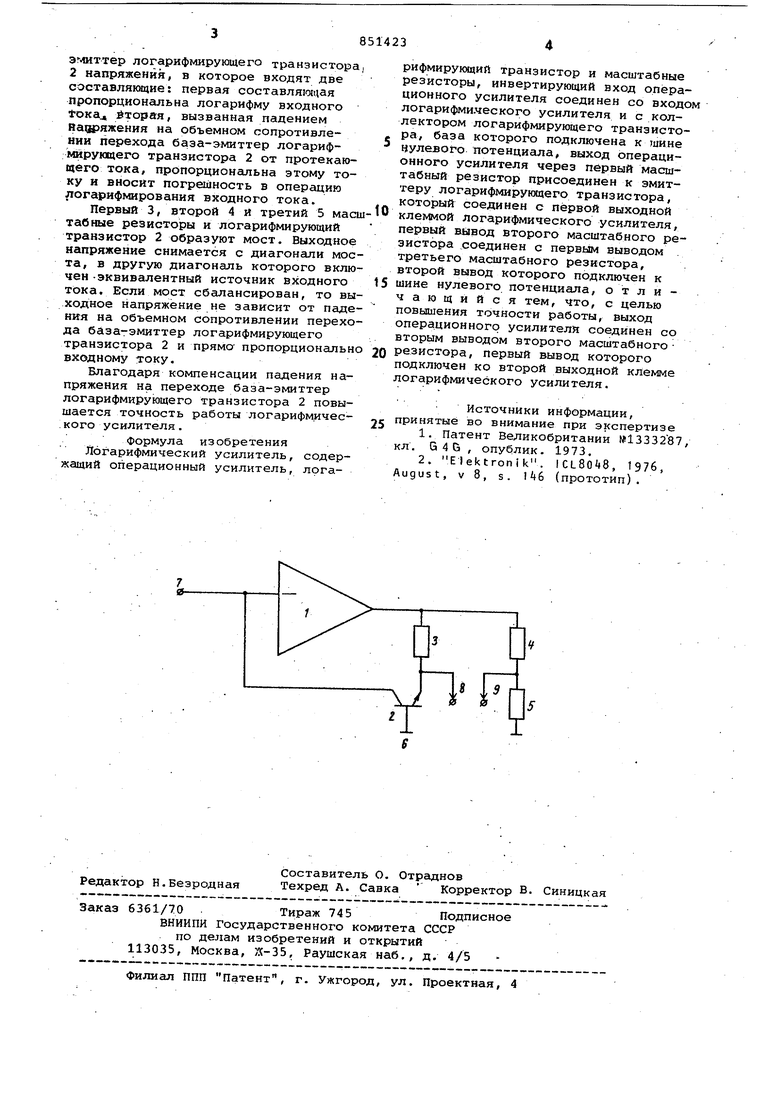

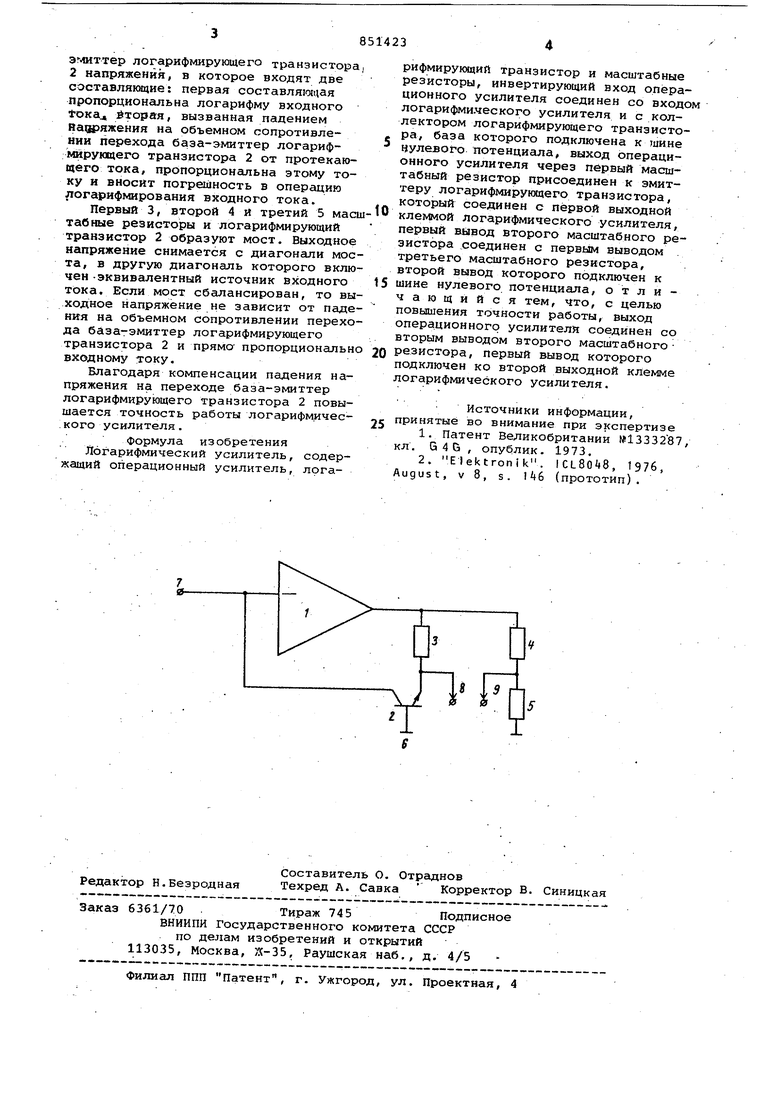

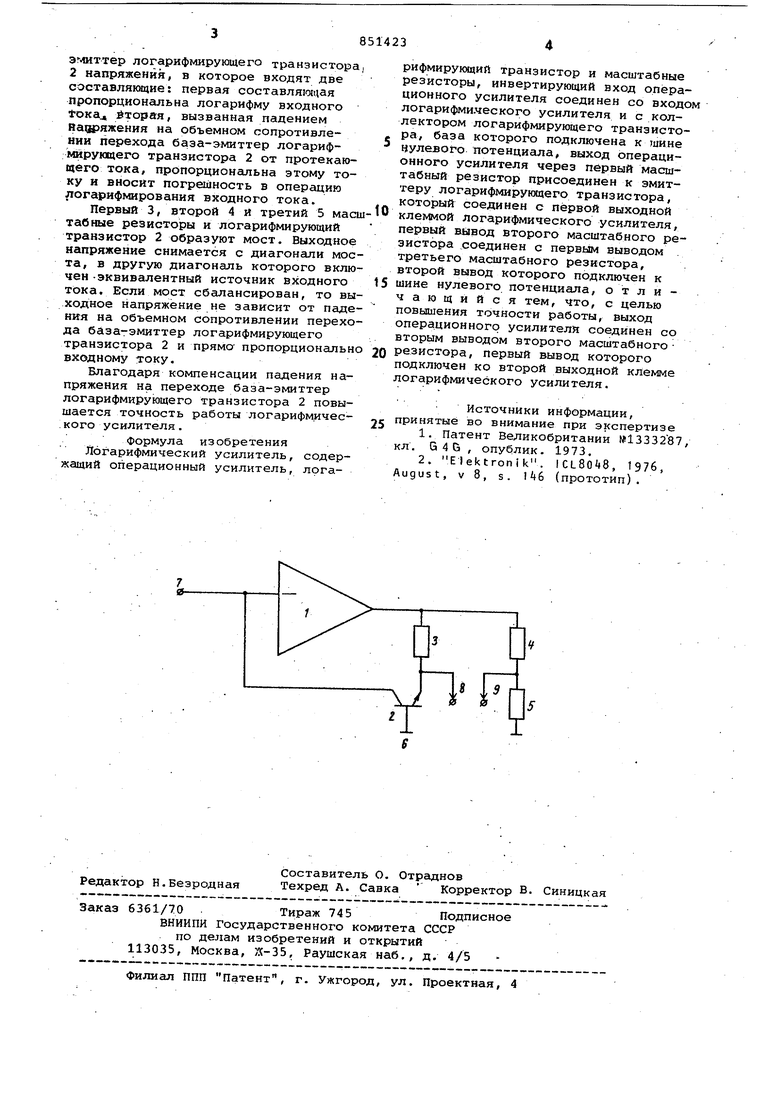

функциональная схема предлагаемого логарифмического усилителяизображена на чертеже.

Устройство содержит опереадионный

20 усилитель 1, логарифмирующий транзистор 2, первый 3, второй 4 и третий 5 масштабные резисторы, шину 6 нулевого потенциала, вход 7 и первую 8

25 и вторую 9 выходные клеммы логарифмического усилителя.

Логарифмический усилитель работает следующим образом.

Входной ток поступает на вход 7, вызывая появление на переходе база-

30

эмиттер логарифмирующего транзистора, 2 напряжения, в которое входят две составляющие: первая составляющая пропорциональна логарифму входного окал вторая, вызванная падением нацряжения на объемном сопротивлении перехода база-эмиттер логарифмирующего транзистора 2 от протекающего тока, пропорциональна этому току и вносит погрешность в операцию логарифкшрования входного тока.

Первый 3, второй 4 и третий 5 масштабные резисторы и логарифмирующий транзистор 2 образуют мост. Выходное напряжение снимается с диагонали моста, в другую диагональ которого включен -эквивалентный источник входного тока. Если мост сбалансирован, то выходное напряжение не зависит от падения на объемном сопротивлении перехода база-эмиттер логарифмирующего транзистора 2 и прямо- пропорционально входному току.

Благодаря компенсации падения напряжения на переходе база-эмиттер логарифмирующего транзистора 2 повышается точность работы логарифмического усилителя.

Формула изобретения

Логарифмический усилитель, содержащий операционный усилитель, логарифмирующий транзистор и масштабные резисторы, инвертирующий вход операционного усилителя соединен со входом логарифми-ческого усилителя и с коллектором логарифмирующего транзистора, база которого подключена к щине нулевого потенциала, выход операционного усилителя через первый масштабный резистор присоединен к эмиттеру логарифмирующего транзистора, который соединен с первой выходной клеммой логарифмического усилителя, первый вывод второго масштабного резистора соединен с первым выводом . третьего масштабного резистора, второй вывод которого подключен к

5 шине нулевого потенциала, отличающийся тем, что, с целью повышения точности работы, выход операционного усилителя соединен со вторым выводом второго масштабного

0 резистора, первый вывод которого подключен ко второй выходной клемме логарифмического усилителя.

Источники информации, 5 принятые во внимание при экспертизе

0б

. у

V - П

Авторы

Даты

1981-07-30—Публикация

1979-12-26—Подача