Иэобретение относится к автоматике и вычислительной технике и может быть использовано в аналоговых вычислительных машинах для реализации выражений вида

т. ef)

(О

где X,Y,Z- входные сигналы;

п - показатель степени, причем I п 1.

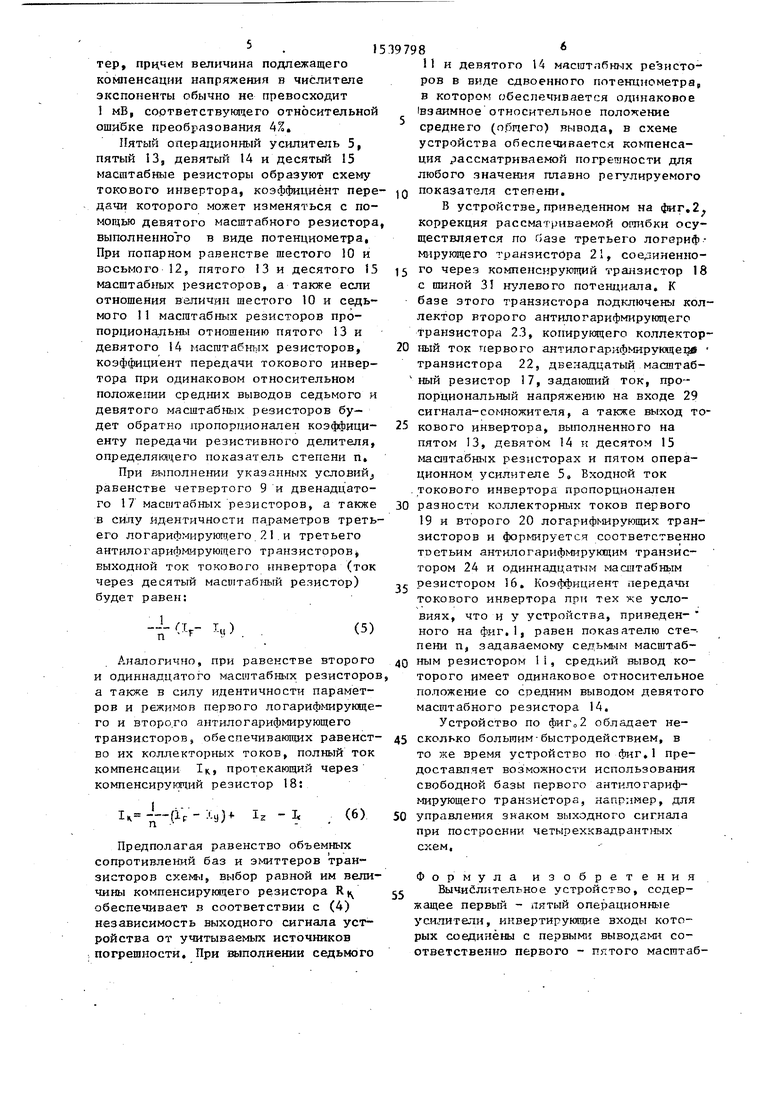

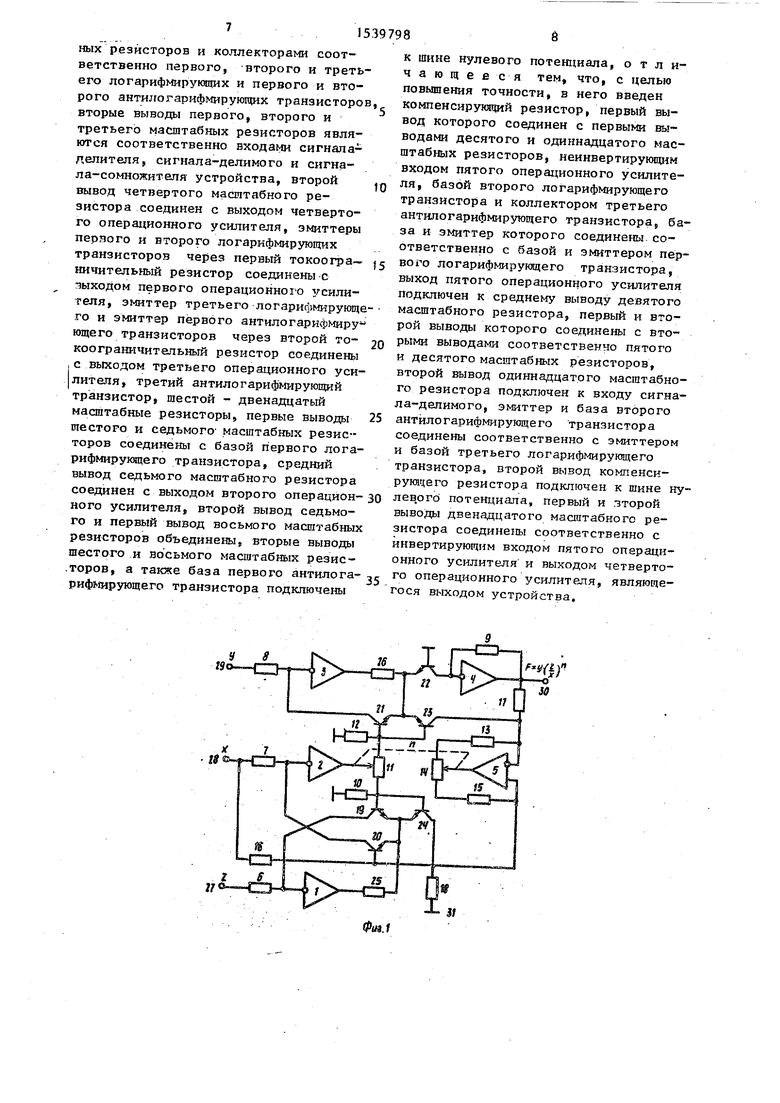

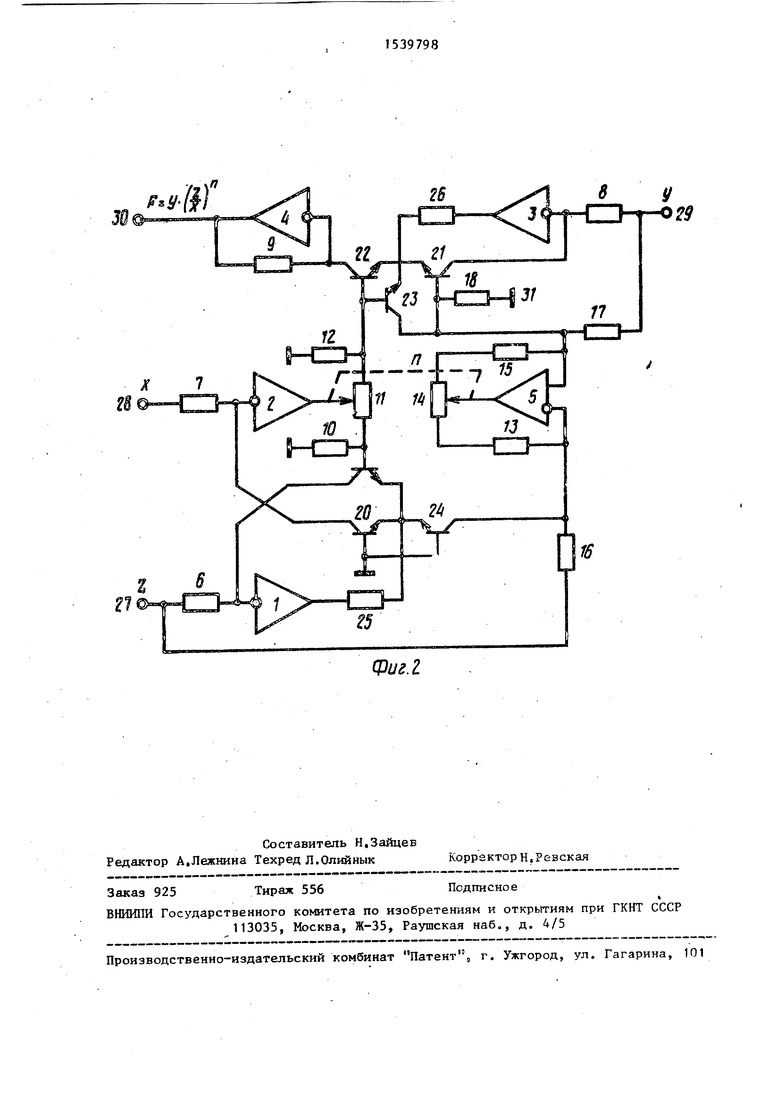

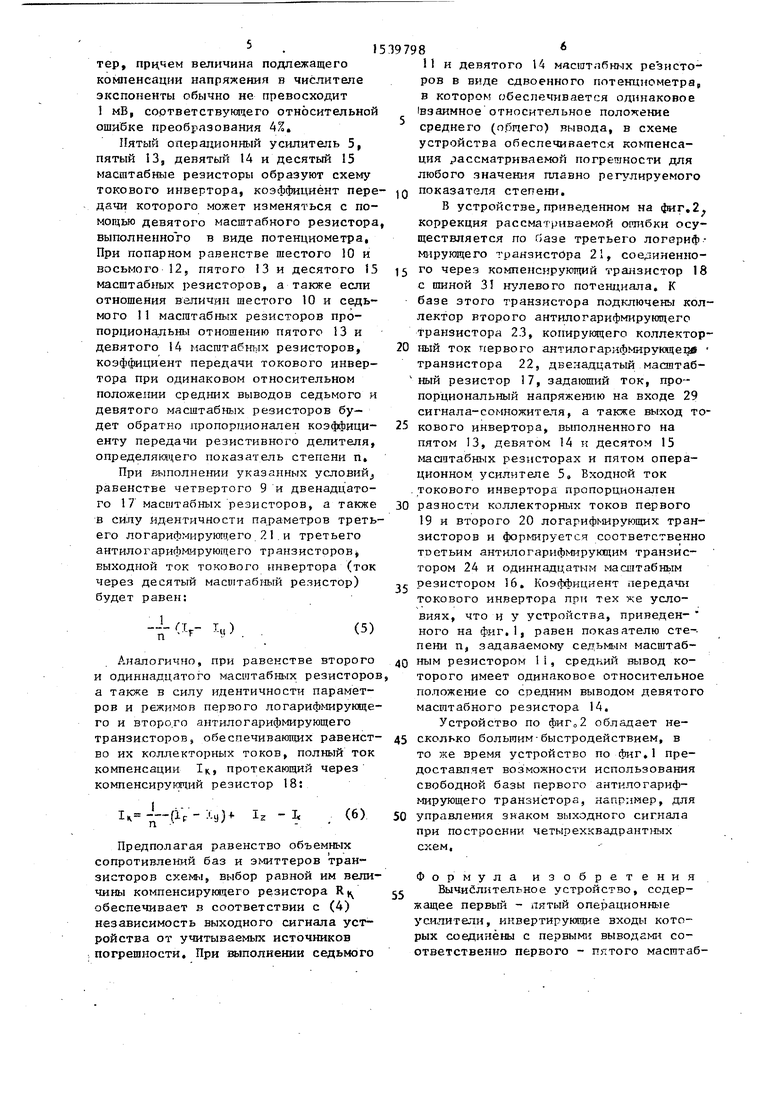

Цель изобретения - повышение точности.На фиг,I изображена функциональная схема предлагаемого вычислительного устройства; на Лиг.2 - то же, пример выполнения,

Вычислительное устройство (фиг,1) содержит первый I, второй 2, третий 3, четвертый 4 и пятни 5 операционные усилители, первый 6, второй 7, третий

8, четвертый 9, шестой 10, седьмой II, восьмой 12, пятый 13, девятый 14, десятый 35, одиннадцатый 16 и двенадцатый 17 масштабные резисторы, компенсирующий резистор 18, первый 19, второй 20 и третий 21 логарифмирующие транзисторы, первый 22, второй 23 и третий 24 антилогарифмирующие транзисторы, первый 25 и второй 26 токо- ограничительные резисторы, входы сигнала-делимого 27, сигнала-делителя 28 и сигнала-сомножителя 29, выход 30 устройства и шину 31 нулевого потенциала,

Устройство работает следухчшм обJ, ЧЗОМс

Первый $ второй 2, третий 3 и четвертый 4 операционные усилители, первый 19, второй 20 и третий 21 логарифмирующие и первый, антилогарифми- рующий 22 транзисторы, первый 6, второй 7, третий 8, четвертый 9, шестой 10, седьмой 11 и восьмой 12 масштаб- ные, первый 25 и второй 26 токоограни- читальные и компенсирующий 18 резис торы образуютодноквадрантный логарифмический вычислитель, реализующий выражение вида (1), с однополярными входными сигналами (положительными в случае использования it-p-n транзит торов, как это показано на фиг,I).

Седьмой масштабный резистор 11 выполняет функции потенциометра для плавной регулировки показателя степени п изменением коэффициента деления резистивного делителя, образованного совместно с шестым 10 и восьмым 2 масштабными резисторами.

Для компенсации ошибки обуслоялен- ной объемными сопротивлениями баз и эмиттеров логарифмирующих и антило- гарифмирующего транзисторов вычислителя, база логарифмирующего транзисто- ра 20 соединена с шиной 31 нулевого потенциала через компенсирующий резистор 18 величиной Нц, через который с помощью остальных элементов схемы задается ток 1ц,, пропорциональный напряжению ошибки, приведенной к логарифмической стороне.

Первый операционный усилитель 1 по цепи: первый токоограничительный резистор 25, переход эмиттер-база первого логарифмирующего транзистора 19 задает ток коллектора Iz,пропорциональный напряжению на входе 27 сигнала-делителяо При этом напряже

ние на переходе база-эмиттер первого логарифмирующего транзистора 19 равно логарифму сигнала с входа 27, Второй операционный усилитель 2 по цепи: седьмой 11 и тестой 10 масштабные резисторы, переходы эмиттер-база первого и второго логарифмирующих транзисторов 19 и 20 задает ток коллектора последнего 1х, пропорциональный сигналу-делимому входа 28. При этом на восьмом масштабном резисторе 12 с учетом действия компенсирующего тока формлруется сигнал

п( In Ь - МЧ1П ---г- + 1х г,

Iz г. + 1кК) ,

(2)

где п - масштабный коэффициент резистивного делителя, образованного шестым 10, седьмым 11 и восьмым 12 масштабными резисторами; т 0,026В- температурный потенциал;

1о - тепловой ток транзисторов. -Третий операнионный усилитель 3 через второй токоограничительный резистор 26, переход эмиттер-база третьего логарифмирующего транзистора 21 устанавливает коллекторный ток последнего Ту пропорциональным напряжению на входе 29 сигнала-сомножителя. Напряжение на эмиттере первого антилогарифмирующего транзистора 22 с учетом падения напряжения на его объемном сопротивлении базы и эмиттера rF:

ЧЧ In -Ь + If r, n(ifTln - +

Д-О- -

+ I,rҐ- I2rz+ IKRK) -л--Ичгч ,,

(3)

.Ь

То

где I - ток первого антилогарифмиругощего транзистора. Поскольку все транзисторы схемы идентичны друг другу и тепловые то-i ки их эмиттерных переходов равны, то напряжение на выходе 30 устройства пропорционально току:

)

Ъхр 3 &1 ЯЈ&& -&ЈЈ -) , М т . (4)

Как видно, погрешность преобразования носит мультипликативный характер, причем величина подлежащего компенсации напряжения в числителе экспоненты обычно не превосходит 1 мВ, соответствующего относительной ошибке преобразования 4%.

Пятый операционный усилитель 5, пятый 13, девятый 14 и десятый 15 масштабные резисторы образуют схему токового инвертора, коэффициент передачи которого может изменяться с помощью девятого масштабного резистора выполненно го в виде потенциометра, При попарном равенстве шестого 10 и восьмого 12, пятого 13 и десятого 15 масштабных резисторов, а также если отношения величин шестого 10 и седьмого 11 масштабных резисторов про- портдиональны отношению пятого 13 и девятого 14 масштабных резисторов, коэффициент передачи токового инвертора при одинаковом относительном положении средних выводов седьмого и девятого масштабных резисторов будет обратно пропор71ионален коэффициенту передачи резистивного делителя, определяющего показатель степени п,

При выполнении указанных условий равенстве четвертого 9 и двенадцатого 17 масштабных резисторов, а также в силу идентичности параметров третьего логарифмирующего 21 и третьего антилогарифмирующего транзисторов, выходной ток токового инвертора (ток через десятый масштабный резистор) будет равен:

,

197986

11 и девятого 14 масштлбнмх резисторов в виде сдвоенного потенциометра, в котором обеспечивается одинаковое взаимное относительное положение среднего (общего) вывода, в схеме устройства обеспечивается компенсация рассматриваемой погрешности для любого значения плавно регулируемого

JQ показателя степени.

В устройстве., приведенном на фиг.2, коррекция рассматриваемой ошибки осуществляется по Пазе третьего логериф- мирующего транзистора 21, соединенно15 го через компенсирующий транзистор 18 с шиной 31 нулевого потенциала. К базе этого транзистора подключены коллектор второго антилогарифмирующего транзистора 23, копирующего коллектор20 ный ток первого антилогарифмирукжце транзистора 22, двенадцатый масштаб- v ный резистор 17, задающий ток, пропорциональный напряжению на входе 29 сигнала-сомножителя, а также выход то25 кового инвертора, выполненного на пятом 13, девятом 14 и десятом 15 масштабных резисторах и пятом операционном усилителе 5 Входной ток токового инвертора пропорционален

30 разности коллекторных токов первого 19 и второго 20 логарифмирующих транзисторов и формируется соответственно тпетьим антилогарифмирующим транзистором 24 и одиннадцатым масштабным

,г резистором 16. Коэффициент передачи токового инвертора при тех же усло

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Четырехквадратное множительно-делительное устройство | 1987 |

|

SU1474686A1 |

| Множительно-делительное устройство | 1987 |

|

SU1543426A1 |

| Вычислительное устройство | 1987 |

|

SU1462364A1 |

| Устройство с регулируемым усилением | 1988 |

|

SU1741257A1 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

| Программируемый приемник сигналов для коммутационных сред | 1988 |

|

SU1718236A1 |

| Устройство регулирования уровня сигнала | 1982 |

|

SU1104653A1 |

| Устройство усиления | 1985 |

|

SU1338001A1 |

| УСТРОЙСТВО ПОДДЕРЖАНИЯ РЕЖИМА РАБОТЫ ПО ПОСТОЯННОМУ ТОКУ УСИЛИТЕЛЯ | 2001 |

|

RU2207712C2 |

Изобретение относится к автоматике и вычислительной технике, в частности к вычислительным устройствам, и служит для реализации по логарифмическому алгоритму множительно-делительных и степенных операций с сигналами в виде напряжения постоянного тока. Целью изобретения является повышение точности за счет компенсации ошибки, обусловленной объемным сопротивлением эмиттеров и баз логарифмирующих транзисторов. Устройство содержит одноквадратный логарифмический многофункциональный модуль, выполненный на первом 1, втором 2, третьем 3 и четвертом 4 операционных усилителях (ОУ), первом 19, втором 20 и третьем 21 логарифмирующих (ЛТ) и первом антилогарифмирующем (АЛТ) 22 транзисторах и первом 6, втором 7, третьем 8, четвертом 9, шестом 10, седьмом 11 и восьмом 12 масштабных резисторах. Для компенсации указанной ошибки база второго ЛТ соединена через компенсирующий резистор 18 с шиной нулевого потенциала, через который задается ток, пропорциональный компенсируемой ошибке и формируемый с помощью второго 23 и третьего 24 антилогарифмирующих транзисторов и одиннадцатого 16 и двенадцатого 17 масштабных резисторов. Токовый инвертор, выполненный на пятом ОУ 5 и пятом 13, девятом 14 и десятом 15 масштабных резисторах, имеет изменяемый с помощью девятого масштабного резистора 14 коэффициент передачи, и за счет его механической связи с седьмым масштабным резистором 11 обеспечивает выполнение условия компенсации при изменении показателя степени реализуемого выражения. 2 ил.

п

т-«)

Аналогично, при равенстве второго и одиннадцатого масштабных резисторов, а также в силу идентичности параметров и режимов первого логарифмирующего и второго антилогарифмирующего транзисторов, обеспечивающих равенство их коллекторных токов, полный ток компенсации «., протекающий через компенсирующий резистор 18:

(lV-. -s)

Iz - Ъ

(6)

Предполагая равенство объемных сопротивлений баз и эмиттеров транзисторов схемы, выбор равной им величины компенсирующего резистора R обеспечивает в соответствии с (4) независимость выходного сигнала устройства от учитываемых источников погрешности. При выполнении седьмого

,

виях, что и У устройства, приведен-

ного на фиг. 1, равен показателю с те-.

пени п, задаваемому седьмым масштаб40 ным резистором 1i, средкий вывод которого имеет одинаковое относительное положение со средним выводом девятого масштабного резистора 14.

Устройство по фиг„2 обладает не45 сколько большим-быстродействием, в то же время устройство по фиг.1 предоставляет возможности использования свободной базы первого антилогарифмирующего транзистора, например, для

50 управления знаком выходного сигнала при построении четырехквадрантных схем.

Формула изобретения Вычислительное устройство, содержащее первый - пятый операционные усилители, инвертирующие входы которых соединены с первыми выводами соответственно первого - пятого масштаб

ных резисторов и коллекторами соответственно первого, второго и третьего логарифмирующих и первого и второго антилогарифмирующих транзисторов вторые выводы первого, второго и третьего масштабных резисторов являются соответственно входами сигнала-1- делителя, сигнала-делимого и сигнала-сомножителя устройства, второй вывод четвертого масштабного резистора соединен с выходом четвертого операционного усилителя, эмиттеры пеолого и второго логарифмирующих транзисторов через первый токоогра- ничительный резистор соединены с выходом первого операционного усилителя, эмиттер третьего логарифмирующе го и эмиттар первого антилогарифмиру- ющего транзисторов через второй то- коограничительный резистор соединены с выходом третьего операционного усилителя, третий антилогарифмирующий транзистор, шестой - двенадцатый масштабные резисторы, первые выводы шестого и седьмого масштабных резисторов соединены с базой первого логарифмирующего транзистора, средний вывод седьмого масштабного резистора соединен с выходом второго операцией- ного усилителя, второй вывод седьмого и первый вывод восьмого масштабных резисторов объединены, вторые выводы шестого и восьмого масштабных резне- .торов, а также база первого антилога- рифмирующего транзистора подключены

У 8

0

г j 0 5 30 ,с

к шине нулевого потенциала, отличающейся тем, что, с целью повышения точности, в него введен компенсирующий резистор, первый вывод которого соединен с первыми выводами десятого и одиннадцатого масштабных резисторов, неинвертирующим входом пятого операционного усилителя, базой второго логарифмирующего транзистора и коллектором третьего антилогарифмирующего транзистора, база и эмиттер которого соединены соответственно с базой и эмиттером первого логарифмирующего транзистора, выход пятого операционного усилителя подключен к среднему выводу девятого масштабного резистора, первый и второй выводы которого соединены с вторыми выводами соответственно пятого и десятого масштабных резисторов, второй вывод одиннадцатого масштабного резистора подключен к входу сигнала-делимого, эмиттер и база второго антилогарифмирующего транзистора соединены соответственно с эмиттером и базой третьего логарифмирующего транзистора, второй вывод компенсирующего резистора подключен к шине ну- лев.ого потенциала, первый и -второй выводы двенадцатого масштабного резистора соединены соответственно с инвертирующим входом пятого операционного усилителя и выходом четвертого операционного усилителя, являющегося выходом устройства.

15

X 7 ГХ.Г±-± 7 WxlJ

°-cb-rf

ю Т Т /Т4

15

W

фуг.2

| Аналоговое множительное устройство | 1976 |

|

SU613333A1 |

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-30—Публикация

1987-08-18—Подача