(54)КОММУТАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматизированного контроля электрических параметров РЭА | 1986 |

|

SU1383306A1 |

| Устройство для обмена информацией | 1982 |

|

SU1091151A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| СИСТЕМА КОНТРОЛЯ И УПРАВЛЕНИЯ ВЫСОКОВОЛЬТНЫМИ ЯЧЕЙКАМИ РАСПРЕДЕЛИТЕЛЬНОЙ СЕТИ ШАХТЫ | 1990 |

|

RU2037205C1 |

| Устройство для сопряжения ЭВМ с абонентами | 1987 |

|

SU1411760A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1986 |

|

SU1319039A1 |

| Устройство для контроля блоков памяти | 1991 |

|

SU1833920A1 |

| Имитатор канала | 1985 |

|

SU1377857A2 |

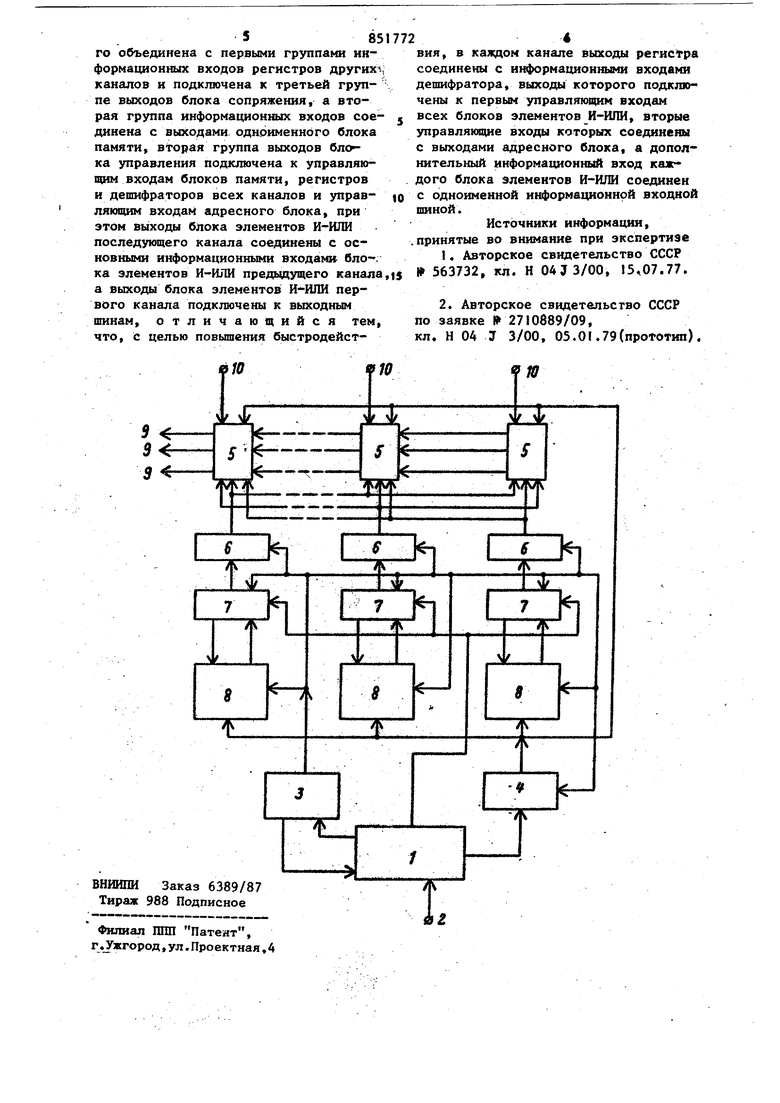

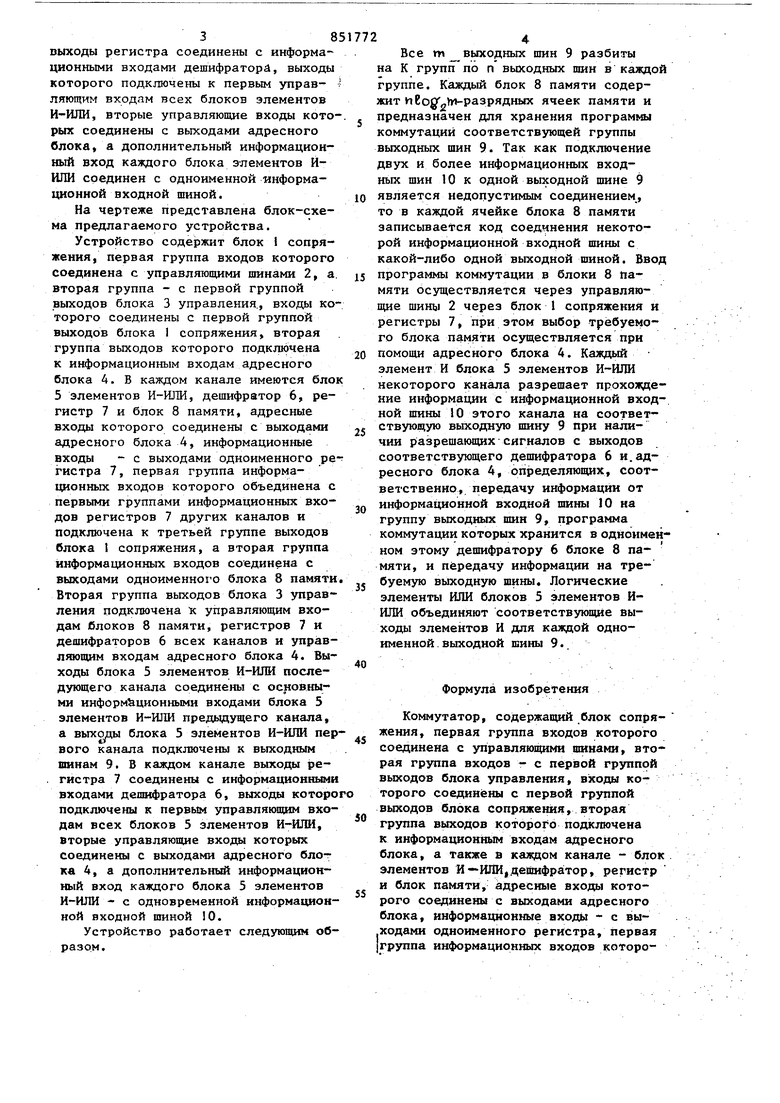

: . . V - Изобретение относится к кoммyтaцйонной технике. Известны крммутаторь, содержащие блок Сопряжения, блок управления и адресный блок, а также в каждой ка нале - блок элементов И-ИЛИ, дешифратор, регистр и блок памяти Д. Наиболее близким по технической сущности к предлагаемому является коммутатор, содержащий блок сопряжения, первая группа входов Которого соединена с управляющими шинами, вто рая группа входов - с первой группой выходов блсгка управления, вкоды которого соединены с первой группой выходов блока сопряжения, вторая группа выходов которого подключена к информацион1шм входам адресного блока, а также в каждом канале - бло элементов И-ИЛИ,дешифратор, регистр и блок памяти, адресные входы которого соединены с выходами адресного блока, информационные входы - с выходами одноименного регистра, первая irpynda информационных входов которого объединена с первыми группами информационных входов регистров других каналов и подключена к третьей группе выходов блока сопряжения, а вторая группа информационных выходов соединена с выходаш одноименного блока Памяти, вторая группа выходов блока управления подключена к управляювсим входам блоков памяти, регистров и дешифраторов всех каналов и управляющим входам адресного блока, при этом выходы блока элементов И-ИЛИ последующего канала соединены с основными информационными входами блока элементов И-ИЛИ предыдущего канала, а выходы блока элементов И-ИЛИ первого канала подключены к выходным щинам. Недостатком известных устройств является низкое быстродействие. Цель изобретения - повышение быстг родействия коммутатора. Указанная цель д эстигается тем, что в коммутаторе в каждом канапе 38 выходы регистра соединены с информационными входами дешифратора, выходы которого подключены к первым управляющим входам всех блоков элементов И-ИЛИ, вторые управляющие входы кото рых соединены с выходами адресного блока, а дополнительный информационный вход каждого блока элементов ЙИПИ соединен с одноименной информационной входной шиной. На чертеже представлена блок-схема предлагаемого устройства. Устройство содержит блок I сопряжения, первая группа входов которого соединена с управляющими шинами 2, а вторая группа - с первой группой выходов блока 3 управления., входы ко торого соединены с первой группой выходов блока 1 сопряжения, вторая группа выходов которого подключена к информационным входам адресного блока 4. В каждом канале имеются бло 5 элементов И-ИЛИ, дешифратор 6, регистр 7 и блок 8 памяти, адресные входы которого соединены с выходами адресного блока 4, информационные входы - с выходами одноименного ре гистра 7, первая группа информационньж входов которого объединена с первыми группами информационных входов регистров 7 других каналов и подключена к третьей группе выходов блока 1 сопряжения, а вторая группа информационных входов соединена с выходами одноименного блока В памяти Вторая группа вьпсодов блока 3 управления подключена к управляющим входам блоков 8 памяти, регистров 7 и дешифраторов 6 всех каналов и управляющим входам адресного блока 4. Выходы блока 5 элементов И-ИЖ последующего канала соединены с основными информационными входами блока 5 элементов И-ИЛИ предьодущего канала, а выходы блока 5 элементов И-ШШ пер вого канала подключены к выходным шинам 9. В каждом канапе выходы рс . гистра 7 соединены с информационными входами дешифратора 6, выходы которо подключены к первым управляющим входам всех блоков 5 элементов И-ИЛИ, вторые управляющие входы которых соединены с выходами адресного блока 4, а дополнительный информационный вход каждого блока 5 элементов И-ИЛИ - с одновременной информацион ной входной шиной 10. Устройство работает следующим об разом. Все т выходных пшн 9 разбиты на К групп по п выходных щин в каждой группе. Каждый блок 8 памяти содержит И ВоО дМ-разрядных ячеек памяти и предназначен для хранения программы коммутаций соответствующей группы выходных шин 9. Так как подключение двух и более информационных входных щин 10 к одной выходной щине 9 является недоцустимым соединением, то в каждой ячейке блока 8 памяти записывается код соединения некоторой информационной входной шины с какой-либо одной выходной шиной. Ввод программы коммутации в блоки 8 памяти осуществляется через управляющие шинь 2 через блок 1 сопряжения и регистры 7, при этом выбор требуемого блока памяти осуществляется при помощи адресного блока 4. Каждый элемент И блока 5 элементов И-ИЛИ некоторого канала разрешает прохояадение информации с информационной входной шины 10 этого канала на соответствующую выходную шину 9 при наличии разрешающих сигналов с выходов соответствующего дешифратора 6 и.адресного блока 4, определяющих, соответственно, передачу информации от информационной входной шины 10 на группу выходных шин 9, программа коммутации которых хранится в одно 1менном этому дешифратору 6 блоке 8 памяти, и передачу информации на требуемую выходную шины. Логические элементы ШШ блоков 5 элементов ИШШ объединяют соответствующие выходы элементов И для каждой одноименной выходной шины 9.. Формула изобретения Коммутатор, содержащий блок сопряжения, первая группа входов которого соединена с управляющими шинами, вторая группа входов - с первой группой выходов блока управления, входы которого соединены с первой группой выходов блока сопряжения, вторая группа выходов которого подключена к информационным входам адресного блока, а также в калодом канале - блок элементов И--ШШ,дешифратор, регистр и блок памяти, адресные входы которого соединены с выходами адресного блока, информационные входы - с выходами одноименного регистра, первая (группа информационных входов которо585го объединена с первыми группами информационных входов регистров других каналов и подключена к третьей группе выходов блока сопряжения, а вторая группа информационных входов соединена с выходами, одноименного блока памяти, вторая группа выходов блока управления подключена к управляющим входам блоков памяти, регистров и дешифраторов всех каналов и управляющим входам адресного блока, при этом выходы блока элементов И-ИЛИ последукицего канала соединены с основными информационными входами бло-. ка элементов И-ШШ предьщущего канала а выходы блока элементов первого канала подключены к выходным шинам, отличающийся тем, что, с целью повышения быстродействия, в каждом канале выходы регис1 ра соединены с информационными входами дешифратора, выходы которого подключены к первым управляющим входам всех блоков элементов И-ИЛИ, вторые управляющие входы которых соединены с выходами адресного блока, а дополнительный информационный вход каж дого блока элементов И-ИЛИ соединен с одноименной информационной входной шиной Источники информации, принятые во внш4ание при экспертизе . Авторское свидетельство СССР 563732, кл. Н 04J 3/00, 15,07.77. 2. Авторское свидетельство СССР по заявке № 2710889/09, кл. Н 04 J 3/00, 05.О1.79(прототип).

Авторы

Даты

1981-07-30—Публикация

1979-10-10—Подача