Изобретение относится к вычислительной технике и может быть использовано при разработке контрольно-испытательной аппаратуры для блоков памяти.

Целью изобретения является расширение области применения устройства за счет использования прямого доступа к памяти и обеспечения возможности подключения средств визуализации.

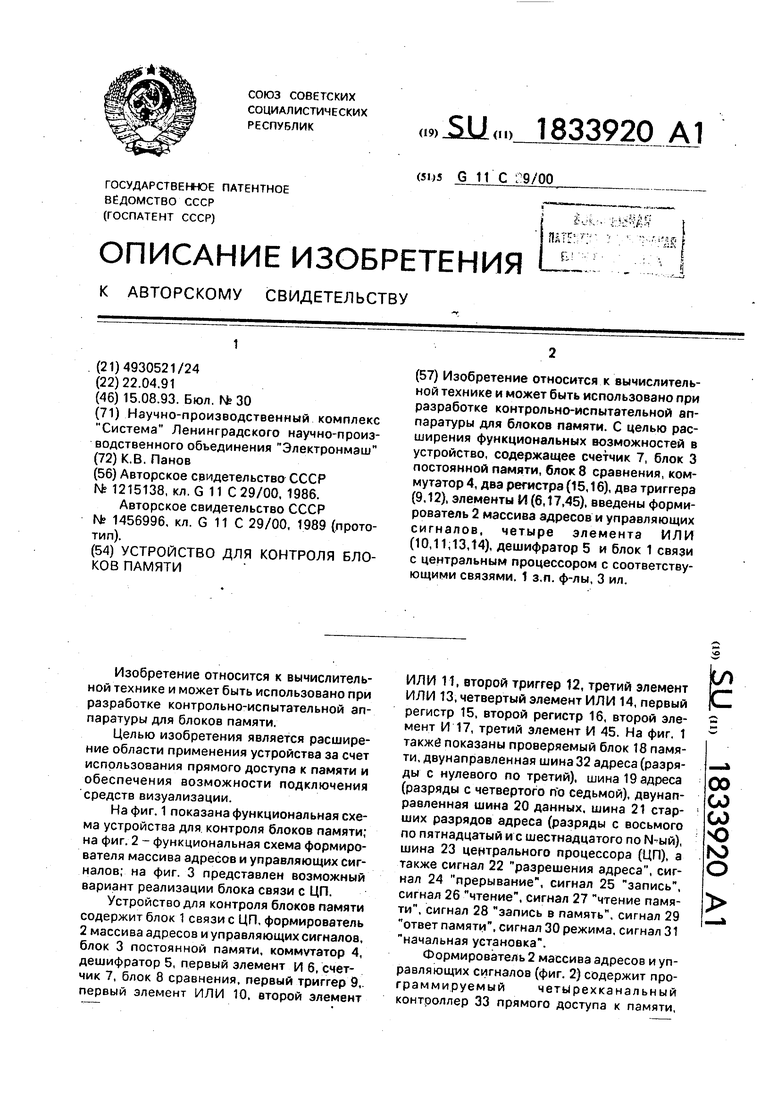

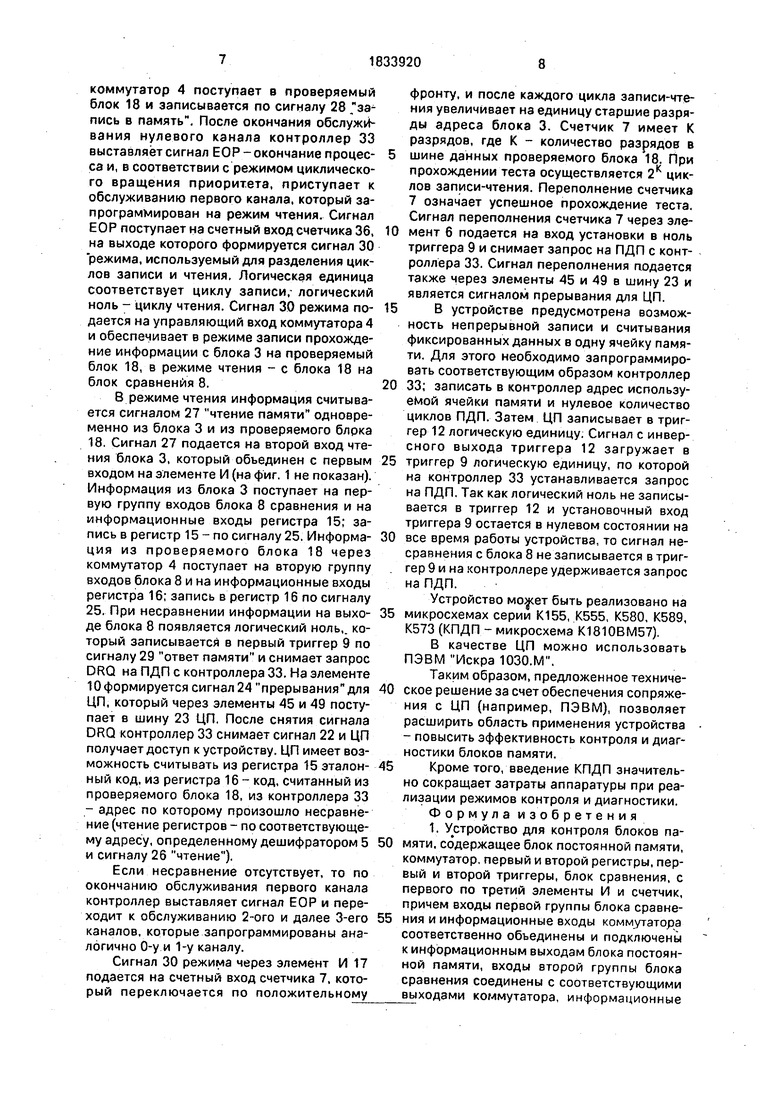

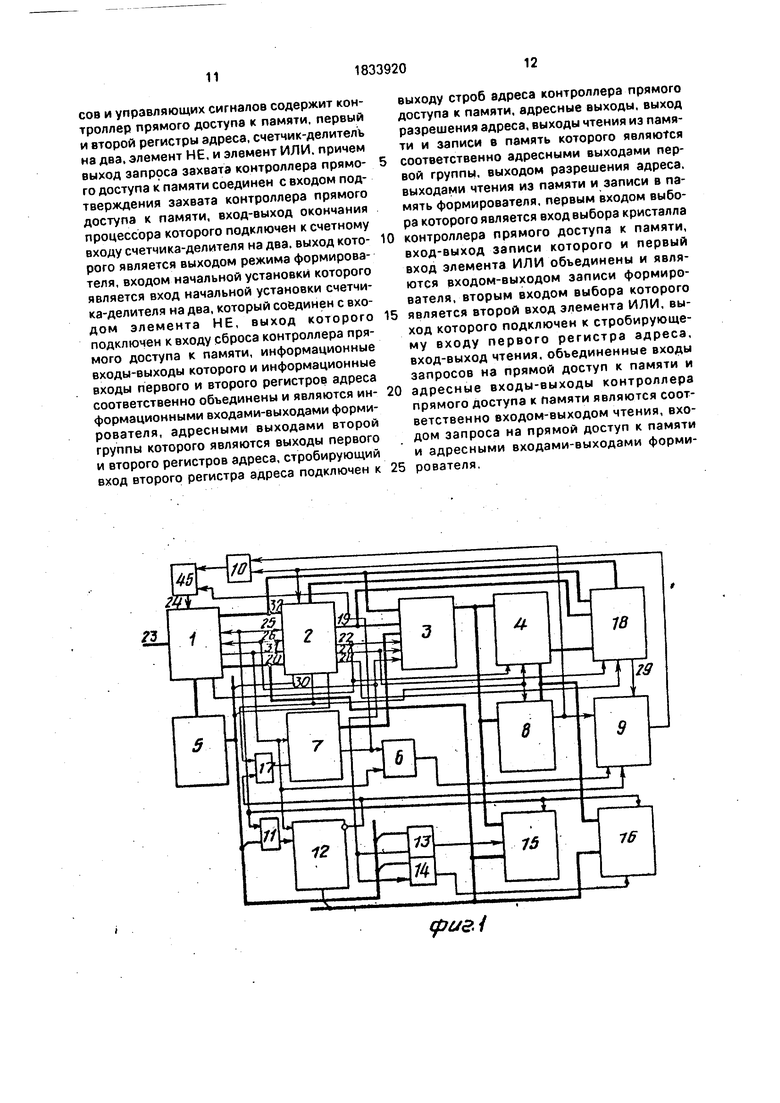

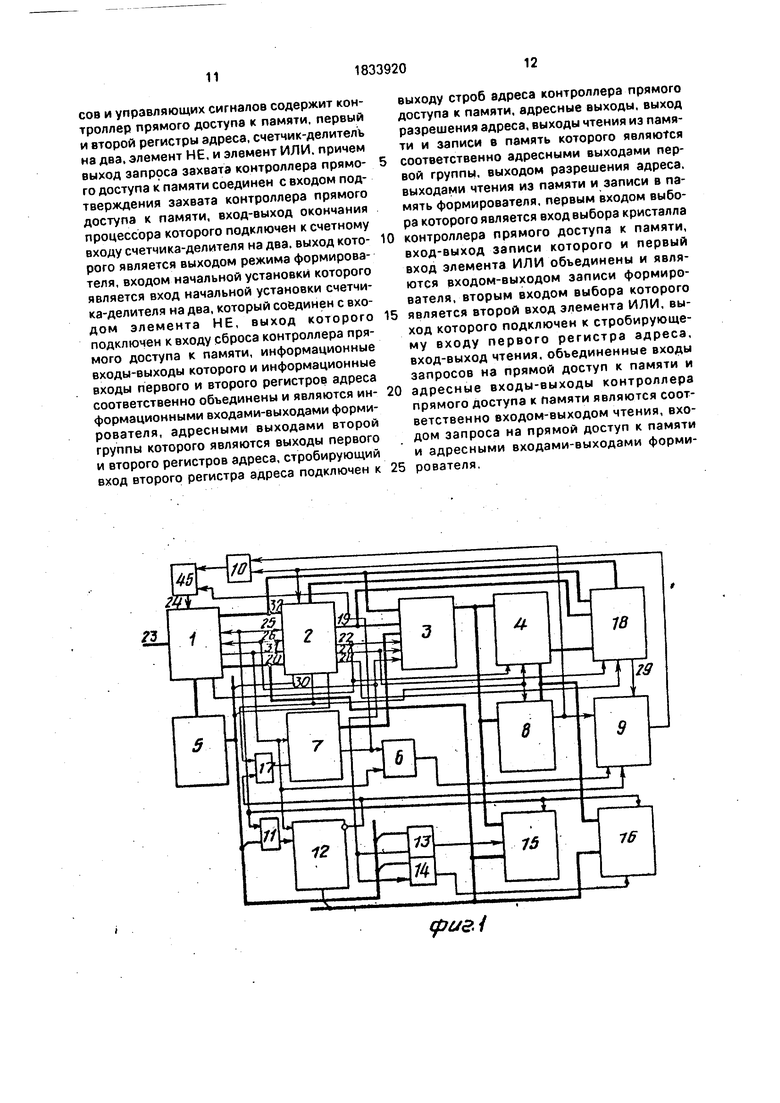

На фиг. 1 показана функциональная схема устройства для контроля блоков памяти; на фиг. 2 - функциональная схема формирователя массива адресов и управляющих сигналов; на фиг. 3 представлен возможный вариант реализации блока связи с ЦП.

Устройство для контроля блоков памяти содержит блок 1 связи с ЦП, формирователь 2 массива адресов и управляющих сигналов, блок 3 постоянной памяти, коммутатор 4, дешифратор 5, первый элемент и 6, счетчик 7, блок 8 сравнения, первый триггер 9,. первый элемент ИЛИ 10, второй элемент

ИЛИ 11, второй триггер 12, третий элемент ИЛИ 13, четвертый элемент ИЛИ 14, первый регистр 15, второй регистр 16, второй элемент И 17, третий элемент И 45. На фиг. 1 также показаны проверяемый блок 18 памяти, двунаправленная шина 32 адреса (разряды с нулевого по третий), шина 19 адреса (разряды с четвертого по седьмой), двунаправленная шина 20 данных, шина 21 старших разрядов адреса (разряды с восьмого по пятнадцатый и с шестнадцатого по ), шина 23 центрального процессора (ЦП), а также сигнал 22 разрешения адреса, сигнал 24 прерывание, сигнал 25 запись, сигнал 26 чтение, сигнал 27 чтение памяти, сигнал 28 запись в память, сигнал 29 ответ памяти, сигнал 30 режима, сигнал 31 начальная установка.

Формирователь 2 массива адресов и управляющих сигналов (фиг. 2) содержит программируемый четь рехканальный контроллер 33 прямого доступа к памяти,

Ё

00

GJ

W

ю к о

ервый регистр 34 адреса, второй регистр 5 адреса, счетчик 36 делитель на два, элеент ИЛИ 37, элемент НЕ 50. Контроллер 33 существляет выдачу массива адресов в шиы 32, 19, 20 и управляющих сигналов. Уп- 5 равляющие сигналы предназначены для перезаписи тестовой последовательности из блока 3 в блок 18, а также для считывания информации из блока 18 и ее сравнения на блоке 8 с эталоном из блока 3.Ю

Блок 1 связи с ЦП (фиг. 3) содержит

регистр 46, шинный формирователь 47,

шинный формирователь 48, повторитель 49.

На фиг. 3 показаны шина 39 младших разрядов адреса, шина 40 старших разря- 15 дов адреса, шина 42 данных, сигнал 41 строб адреса, сигнал 43 запись, сигнал 44 чтение, сигнал 31 начальная установка, шина 23 ЦП (объединяющая все перечисленные шины и сигналы).20

Шина 32 соединяет входы - выходы адреса формирователя 2 массива адресов и управляющих сигналов с адресными выходами первой группы блока 1 связи с ЦП, с адресными входами первой группы блока 3 25 постоянной памяти и с адресными входами первой группы тестируемого блока 18 памяти, шина 19 соединяет адресные выходы первой группы формирователя 2 с соответствующими входами 3 и с соответствующи- 30 ми входами блока 18, шина 21 соединяет адресные выходы второй группы формирователя 2 с адресными входами третьей груп- пы блока 18, шина 20 соединяет информационные входы-выходы формиро- 35 вателя 2 с одноименными входами - выходами блока 1, с информационными входами первого регистра 15 и второго регистра 16, причем нулевой разряд шины 20 соединен также с информационным входом триггера 40 12 установки, сигнал 25 запись подключен к одноименному входу - выходу формирователя 2, к выходу записи блока 1, к тактовому входу регистра 15 и регистра 16 и к первому входу второго элемента ИЛИ 11, сигнал 26 45 чтение соединен с одноименным входом - выходом формирователя 2, с выходом чтения блока 1, с первым входом чтения блока 3, со вторым входом элемента 13 и со вторым входом элемента 14, сигнал 31 началь- 50 ная установка подключен к одноименному выходу блока 1, к входу начальной установки формирователя 2, к одноименному входу счетчика 7, к входу установки в нулевое состояние триггера 12 и ко второму входу эле- 55 мента 6, сигнал 22 разрешение адреса подключен к выходу формирователя 2, к входу выбора блока 3, к.входу выбора блока 1 и к входу выбора коммутатора 4, сигнал 27 чтение памяти подключен к выходу формирователя 2, ко второму входу чтения блока 3 и к входу чтения блока 18, сигнал 28 запись в память соединен с выходом формирователя 2, с одноименным входом блока 18, сигнал 30 режима подключен к выходу формирователя. 2, к управляющему входу коммутатора 4, к входу выбора блока 8 сравнения и к первому входу элемента 17, выходы счетчика 7 подключены к адресным входам третьей группы блока 3, выход элемента 17 подключен к счетному входу счетчика 7, выход переполнения которого соединен со вторым входом элемента 45 и с первым входом элемента 6, выход которого соединен с входом установки в нулевое состояние триггера 9, выход которого соединен с входом запроса на ПДП формирователя 2 и с первым входом элемента 10, вход установки в единичное состо- яние триггера 9 соединен со вторым входом элемента 17 и с инверсным выходом триггера 12, тактовый вход которого соединен с выходом элемента 11, второй вход которого подключен ко второму выходу дешифратора 5, причем входы дешифратора 5 соединены с выходами соответствующих разрядов адреса блока 1, первый выход дешифратора 5 подключен к первому входу выбора формирователя 2, третий выход дешифратора 5 подключен к первому входу элемента 13, выход которого подключен к входу выбора регистра 15, выходы которого соединены с информационными выходами данных блока 3, первой группой входов блока 8, и с информационными входами коммутатора 4, четвертый выход дешифратора 5 подключен к первому входу элемента 14, выход которого подключен к входу выбора регистра 16, входы которого соединены с выходами коммутатора 4 и с второй группой входов блока

8сравнения, пятый выход дешифратора 5 подключен ко второму входу выбора формирователя 2, выход блока 8 сравнения подключен к информационному входу триггера

9и к первому входу элемента 10, выход которого соединен с первым входом эле- мента.45, выход которого соединен с входом прерывания блока 1, сигнал 29 ответ памяти подается с выхода блока 18 на тактовый вход триггера 9.

Тестовая последовательность для контроля блока 18 памяти, хранящаяся в блоке 3, реализует блочный адресный динамический тест. Принцип действия теста заключается в следующем. Все адресные поля блока 18 разбиваются на области объемом 2К, где К- разрядность шины данных блока 18. При первом проходе теста в каждый адрес проверяемого блока 18 записываются данные, равные младшей части текущего адреса.

Разрядность младшей части адреса - К. Затем осуществляется считывание информации из блока 18. При последующих проходах данные по текущему адресу увеличиваются на единицу. Количество проходов равно 2К. Этот тест позволяет выявить неисправности типа замыкание или обрыв шины адреса, замыкание или обрыв шины данных, дефекты ячеек памяти. Устройство допускает использование и других тестов.

Для перезаписи тестовой последовательности из блока 3 в проверяемый блок 18 используется режим прямого доступа к памяти (ПДП). Режим ПДП является самым скоростным способом обмена и реализуется с помощью контроллера 33. Для осуществления ПДП контроллер 33 должен выполнять ряд последовательных операций:

1)Принять запрос DRQ на ПДП с триггера 9;

2)сформировать запрос HRQ на захват шины 20 данных и шины 32 адреса;

3)принять сигнал HLDA - подтверждение захвата;

4)сформировать на шинах 32, 19; 21, адрес ячейки памяти, предназначенной для обмена;

5)выработать сигналы 25 записи, 26 чтения, 27 чтения памяти, 28 записи в память ;

6)по окончанию ПДП либо повторить цикл ПДП, изменив адрес, либо прекратить ПДП по снятию запроса DRQ на ПДП.

Устройство работает следующим образом. При подаче с шины 23 сигнала 31 начальная установка (фиг. 3) контроллер 33 устанавливается в исходное состояние, приводятся в нулевое состояние все разряды счетчика 7, триггер 9 и триггер 12. Устанавливается в единицу счетчик 36. Далее про- граммируется контроллер 33. Программирование осуществляется от ЦП (на фиг. 1 не показан) командами ввода - вывода через блок 1 связи с ЦП. Адреса внутренних регистров контроллера 33 определяются кодом на шине 32. Записываемые в контроллер 33 константы представляются 16-разрядным словом. Их загрузка требует для ЦП выполнения двух последовательных операций вывода с одинаковым кодом. Внутренний триггер контроллера управляет последовательность ввода. Сначала загружается младший байт, затем старший. В регистры хранения текущего адреса всех каналов контроллера заносится код начального адреса, в регистры циклов - количество циклов прямого доступа к памяти; в регистр режима - код,обеспечивающий режим обслуживания - передачи по требованию тип цикла ПДП (цикл записи для каналов 0 и 2, цикл чтения для каналов 1 и 3); режим автоинициализации; в регистр команд - код, 5 обеспечивающий вращение приоритета каналов.

Такое программирование обеспечит запись тестовой последовательности в прове- 0 ряемый блок 18 в зоне адресов, которая определяется начальным адресом и количеством циклов ПДП. Циклом записи управляет нулевой канал контроллера. Затем (в силу режима вращения приоритета) обслужива5 ется первый канал, который запрограммирован на цикл чтения и т.д. Когда наивысший приоритет снова получит нулевой канал (из-за режима автоинициализации) будут повторены все циклы ПДП в той

0 же зоне адресов.

После окончания программирования ЦП записывает в регистр 34 с шины 20 код, определяющий область памяти, в которой проводится тестирование. Запись осущест5 вляется сигналом 25 запись, который подается на вход записи регистра 34 через элемент 37. На,второй вход элемента 37 подается сигнал с выхода дешифратора 5, определяющего адрес регистра 34 в устрой0 стве. Далее ЦП устанавливает в единичное состояние триггер 12 (по младшему разряду шины 20 единица записывается в триггер 12 сигналом 25 запись при соответствующем адресе сигналом с дешифратора 5). Сигнал

5 с инверсного выхода триггера 12 переключает триггер 9 в состояние логической единицы и на входе DRQ контроллера 33

0 устанавливается запрос на ПДП. Затем ЦП аналогично записывает в триггер 12 логический ноль. Получив запрос DRQ контроллер 33 выставляет сигнал HRD (запрос захвата), подключенный к его же входу HLDA (под5 тверждение захвата), по которому начинается генерация массива адресов и управляющих сигналов с нулевого канала. Далее контроллер 33 устанавливает сигнал 22 разрешение адреса, переключающий в

0 третье состояние регистр 46, шинные формирователи 47 и 48 блока 1. Младшие разряды адреса (АО-А7) поступают в шины 32,

19и подаются на соответствующие адресные входы блока 18 и блока 3. Старшие

5 разряды адреса (А8-А15) поступают в шину

20и записываются в регистр 95 сигналом ADSTB. Выходы регистра 35 подключаются на соответствующие адресные входы блока 18.

Так как нулевой канал контроллера 33 запрограммирован на режим записи, тестовая последовательность считывается из блока 3 (сигналом 26 чтение, который подается на 1-ый вход чтение блока) через

коммутатор 4 поступает в проверяемый блок 18 и записывается по сигналу 28 запись в память. После окончания обслуживания нулевого канала контроллер 33 выставляет сигнал ЕОР - окончание процес- са и, в соответствии с режимом циклического вращения приоритета, приступает к обслуживанию первого канала, который запрограммирован на режим чтения. Сигнал ЕОР поступает на счетный вход счетчика 36, на выходе которого формируется сигнал 30 режима, используемый для разделения циклов записи и чтения. Логическая единица соответствует циклу записи,- логический ноль - циклу чтения. Сигнал 30 режима по- дается на управляющий вход коммутатора 4 и обеспечивает в режиме записи прохождение информации с блока 3 на проверяемый блок 18, в режиме чтения - с блока 18 на блок сравнения 8.

В режиме чтения информация считывается сигналом 27 чтение памяти одновременно из блока 3 и из проверяемого блрка 18. Сигнал 27 подается на второй вход чтения блока 3, который объединен с первым входом на элементе И (на фиг. 1 не показан). Информация из блока 3 поступает на первую группу входов блока 8 сравнения и на информационные входы регистра 15; запись в регистр 15 - по сигналу 25. Информа- ция из проверяемого блока 18 через коммутатор 4 поступает на вторую группу входов блока 8 и на информационные входы регистра 16; запись в регистр 16 по сигналу 25. При несравнении информации на выхо- де блока 8 появляется логический ноль,, который записывается в первый триггер 9 по сигналу 29 ответ памяти и снимает запрос DRQ на ПДП с контроллера 33. На элементе 10 формируется сигнал 24 прерывания для ЦП, который через элементы 45 и 49 поступает в шину 23 ЦП, После снятия сигнала DRQ контроллер 33 снимает сигнал 22 и ЦП получает доступ к устройству. ЦП имеет возможность считывать из регистра 15 эталон- ный код, из регистра 16 - код, считанный из проверяемого блока 18, из контроллера 33 - адрес по которому произошло несравнение (чтение регистров - по соответствующему адресу, определенному дешифратором 5 и сигналу 26 чтение).

Если несравнение отсутствует, то по окончанию обслуживания первого канала контроллер выставляет сигнал ЕОР и переходит к обслуживанию 2-ого и далее 3-его каналов, которые запрограммированы аналогично 0-у и 1-у каналу.

Сигнал 30 режима через элемент И 17 подается на счетный вход счетчика 7, который переключается по положительному

фронту, и после каждого цикла записи-чтения увеличивает на единицу старшие разряды адреса блока 3. Счетчик 7 имеет К разрядов, где К - количество разрядов в шине данных проверяемого блока 18. При прохождении теста осуществляется 2К циклов записи-чтения. Переполнение счетчика 7 означает успешное прохождение теста. Сигнал переполнения счетчика 7 через элемент 6 подается на вход установки в ноль триггера 9 и снимает запрос на ПДП с контроллера 33. Сигнал переполнения подается также через элементы 45 и 49 в шину 23 и является сигналом прерывания для ЦП.

В устройстве предусмотрена возможность непрерывной записи и считывания фиксированных данных в одну ячейку памяти. Для этого необходимо запрограммировать соответствующим образом контроллер 33; записать в контроллер адрес используемой ячейки памяти и нулевое количество циклов ПДП. Затем ЦП записывает в триггер 12 логическую единицу; Сигнал с инверсного выхода триггера 12 загружает в триггер 9 логическую единицу, по которой на контроллер 33 устанавливается запрос на ПДП, Так как логический ноль не записывается в триггер 12 и установочный вход триггера 9 остается в нулевом состоянии на все время работы устройства, то сигнал несравнения с блока 8 не записывается в триггер 9 и на контроллере удерживается запрос на ПДП.

Устройство может быть реализовано на микросхемах серии К155, К555, К580, К589, К573 (КПДП - микросхема К1810ВМ57).

В качестве ЦП можно использовать ПЭВМ Искра 1030.М.

Таким образом, предложенное техническое решение за счет обеспечения сопряжения с ЦП (например, ПЭВМ), позволяет расширить область применения устройства - повысить эффективность контроля и диагностики блоков памяти.

Кроме того, введение КПДП значительно сокращает затраты аппаратуры при реализации режимов контроля и диагностики.

Ф о р м у л а и з о б р е т е н и я

1. Устройство для контроля блоков памяти, содержащее блок постоянной памяти, коммутатор, первый и второй регистры, первый и второй триггеры, блок сравнения, с первого по третий элементы И и счетчик, причем входы первой группы блока сравнения и информационные входы коммутатора соответственно объединены и подключены к информационным выходам блока постоянной памяти, входы второй группы блока сравнения соединены с соответствующими выходами коммутатора, информационные

входы-выходы которого являются информационными входами-выходами устройства, входом ответа памяти которого является тактовый вход первого триггера, информационный вход которого соединен с выходом блока сравнения, отличающееся тем, что, с целью расширения области применения устройства за счет использования прямого доступа к памяти и обеспечения возможности подключения средств визуализации, в него введены формирователь массива адресов и управляющих сигналов, с первого по четвертый элементы ИЛИ, дешифратор и блок связи с центральным процессором, причем адресные входы-выходы формирователя массива адресов и управляющих сигналов и адресные входы первой группы Ьлока постоянной памяти соответственно объединены и подключены к адресным выходам первой группы блока связи с центральным процессом, которые являются адресными выходами первой группы устройства, адресные выходы первой группы формирователя массива адресов и управляющих сигналов подключены к соответствующим адресным входам второй группы блока постоянной памяти и являются адресными выходами второй группы устройства, адресными выходами третьей группы которого являются адресные выходы второй группы формирователя массива адресов и управляющих сигналов, информационные входы-выходы которого и информационные входы-выходы блока связи с центральным процессором соответственно объединены и подключены к выходам первого и второго регистров, причем выход нулевого разряда соединен с информационным входом второго триггера, тактовый вход которого соединен с выходом второго элемента ИЛИ, первый вход которого, тактовые входы первого и второго регистров и вход-выход записи формирователя массива адресов и управляющих сигналов объединены и подключены к выходу записи блока связи с цен-, тральным процессором, вход выбора которого, вход выбора блока постоянной памяти и вход выбора коммутатора объединены и подключены к выходу разрешения адреса формирователя массива адресов и управляющих сигналов, вход-выход чтения которого, первый вход чтения блока постоянной памяти и первые входы третьего и четвертого элементов ИЛИ объединены и подключены к выходу чтения блока связи с центральным процессором, вход начальной установки формирователя массива адресов и управляющих сигналов, вход начальной установки счетчика, вход установки в О второго триггера и первый вход первого элемента И объединены и подключены к выходу начальной установки блока связи с центральным процессором, выход чтения из памяти формирователя массива адресов и 5 управляющих сигналов соединен с вторым входом чтения блока постоянной памяти и является выходом чтения устройства, выходом записи которого является выход записи в память формирователя массива адресов и

0 управляющих сигналов, вход запроса на прямой доступ к памяти которого и первый вход первого элемента ИЛИ объединены и подключены к выходу первого триггера, вход установки в Г которого соединен с

5 инверсным выходом второго триггера и первым входом второго элемента И, второй вход которого, вход выбора блока сравнения и управляющий вход коммутатора объединены и подключены к выходу режима

0 формирователя массива адресов и управляющих сигналов, первый вход выбора которого подключен к первому выходу дешифратора, входы которого соединены с адресными выходами второй группы блока

5 связи с центральным процессором, вход прерывания которого соединен с выходом третьего элемента И, первый вход которого и второй вход первого элемента И объединены и подключены к выходу переполнения

0 счетчика, информационные выходы которого соединены с соответствующими адресными входами третьей группы блока постоянной памяти, счетный вход счетчика соединен с выходом второго элемента И,

5 второй вход третьего элемента И соединен с выходом первого элемента ИЛИ, второй вход которого соединен с информационным входом первого триггера, вход установки в О которого соединен с выходом первого

0 элемента И, второй вход второго элемента ИЛИ соединен с вторым выходом дешифратора, .третий выход которого подключен к второму входу третьего элемента ИЛИ, выход которого соединен с входом выбора

5 первого регистра, информационные входы которого соединены с информационными выходами блока постоянной памяти, четвертый выход дешифратора подключен к второму входу четвертого элемента ИЛИ, выход

0 которого соединен с входом выбора второго регистра, входы которого соединены с выходами коммутатора, пятый выход дешифратора подключен к второму входу выбора формирователя массива адресов и управля5 ющих сигналов, входы-выходы связи с центральным процессором блока связи с центральным процессором являются входами-выходами устройства.

2. Устройство по п. 1, о т л и ч а ю щ е е- с я тем. что формирователь массива адресов и управляющих сигналов содержит контроллер прямого доступа к памяти, первый и второй регистры адреса, счетчик-делитель на два, элемент НЕ, и элемент ИЛИ. причем выход запроса захвата контроллера прямого доступа к памяти соединен с входом подтверждения захвата контроллера прямого доступа к памяти, вход-выход окончания процессора которого подключен к счетному входу счетчика-делителя на два. выход которого является выходом режима формирователя, входом начальной установки которого является вход начальной установки счетчика-делителя на два, который соединен с входом элемента НЕ, выход которого подключен к входу сброса контроллера прямого доступа к памяти, информационные входы-выходы которого и информационные входы первого и второго регистров адреса соответственно объединены и являются информационными входами-выходами формирователя, адресными выходами второй группы которого являются выходы первого и второго регистров адреса, стробирующий вход второго регистра адреса подключен к

выходу строб адреса контроллера прямого доступа к памяти, адресные выходы, выход разрешения адреса, выходы чтения из памяти и записи в память которого являются

соответственно адресными выходами первой группы, выходом разрешения адреса, выходами чтения из памяти и записи в память формирователя, первым входом выбора которого является вход выбора кристалла

контроллера прямого доступа к памяти, вход-выход записи которого и первый вход элемента ИЛИ объединены и являются входом-выходом записи формирователя, вторым входом выбора которого

является второй вход элемента ИЛИ, выход которого подключен к стробирующе- му входу первого регистра адреса, вход-выход чтения, объединенные входы запросов на прямой доступ к памяти и

адресные входы-выходы контроллера прямого доступа к памяти являются соответственно входом-выходом чтения, входом запроса на прямой доступ к памяти и адресными входами-выходами формирователя,

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Электронная вычислительная машина с прямым доступом в память | 1990 |

|

SU1751776A1 |

| Устройство для ввода информации | 1987 |

|

SU1531082A1 |

| Устройство сопряжения с памятью | 1985 |

|

SU1262515A1 |

| ЭВМ | 1990 |

|

RU2024928C1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для ввода информации от аналоговых датчиков | 1988 |

|

SU1578706A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке контрольно-испытательной аппаратуры для блоков памяти. С целью расширения функциональных возможностей в устройство, содержащее счетчик 7, блок 3 постоянной памяти, блок 8 сравнения, коммутатор 4, два регистра (15,16), два триггера

фиг. /

Фиг. 2.

зг

| Устройство для контроля памяти | 1984 |

|

SU1215138A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1456996A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1993-08-15—Публикация

1991-04-22—Подача