сегмента, дешифратор 3 адреса, регистр 4 номера массива, первый 5, второй 6, третий 7 приемопередатчики, коммутатор 8, первый 9, второй 10. элементы И, триггер И. УстройИзобретение относится к вычислительной технике и может быть использовано при построении мультипроцессорных вычислительных систем на базе .мини- и микро-ЭВМ,

Целью изобретения является повышение производительности устройства при организации многопроцессорной системы.

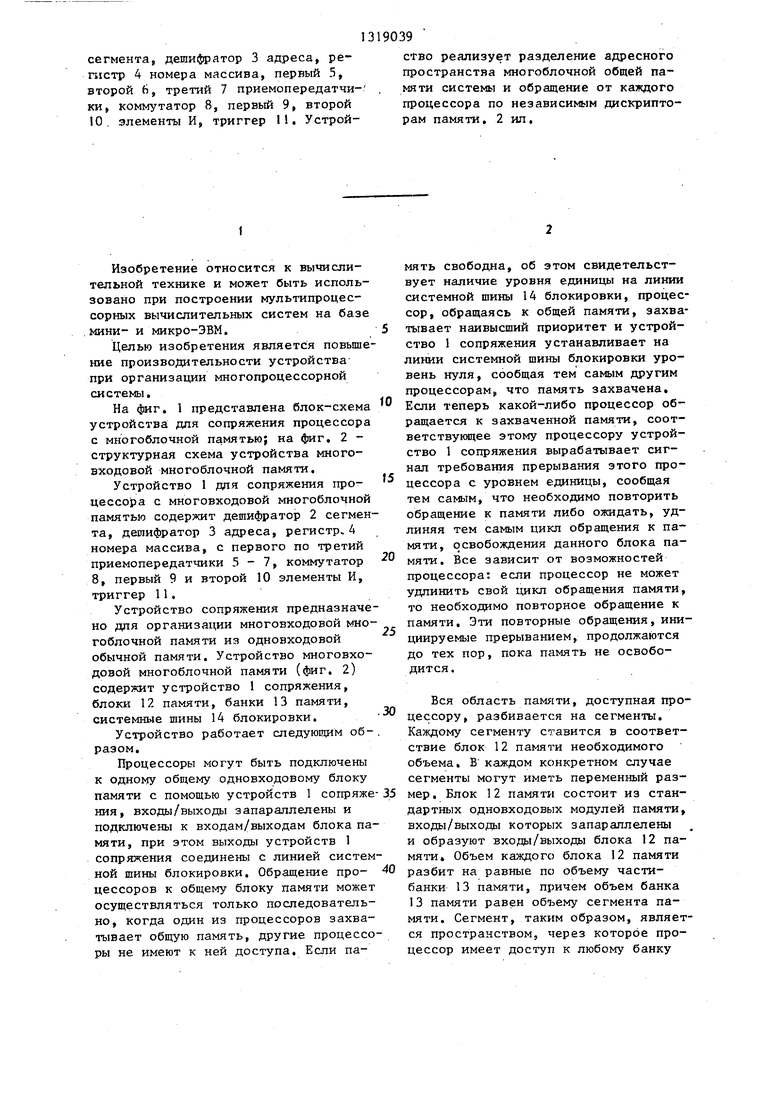

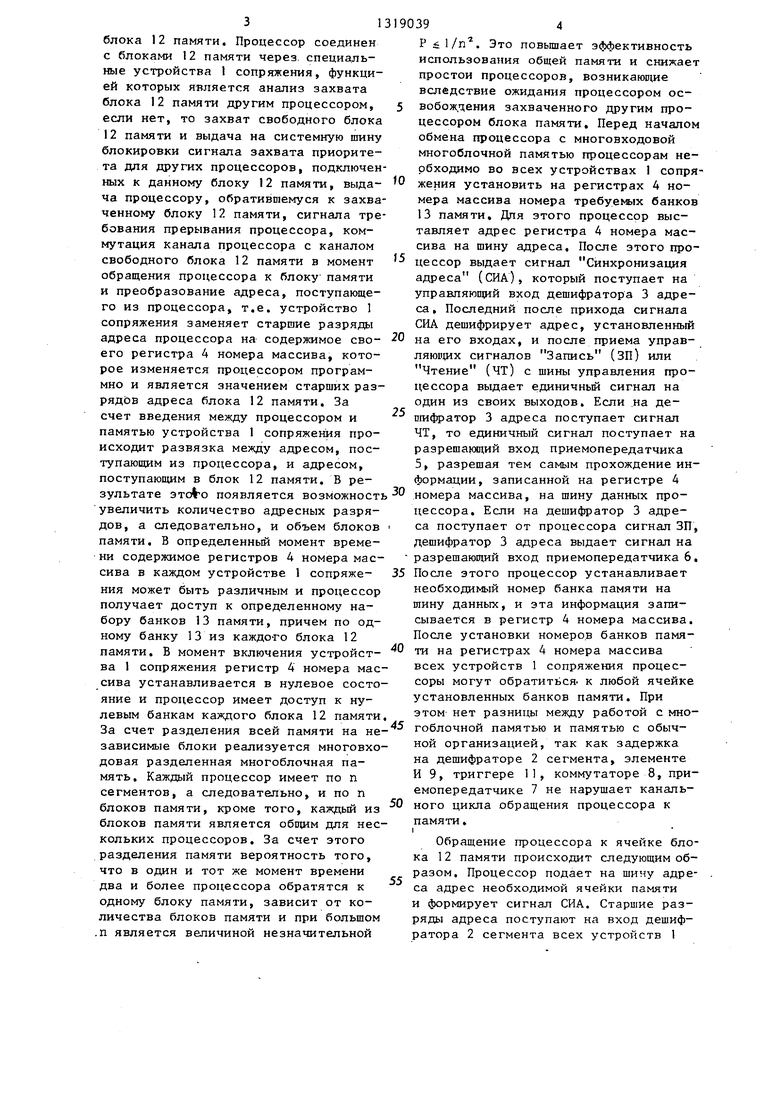

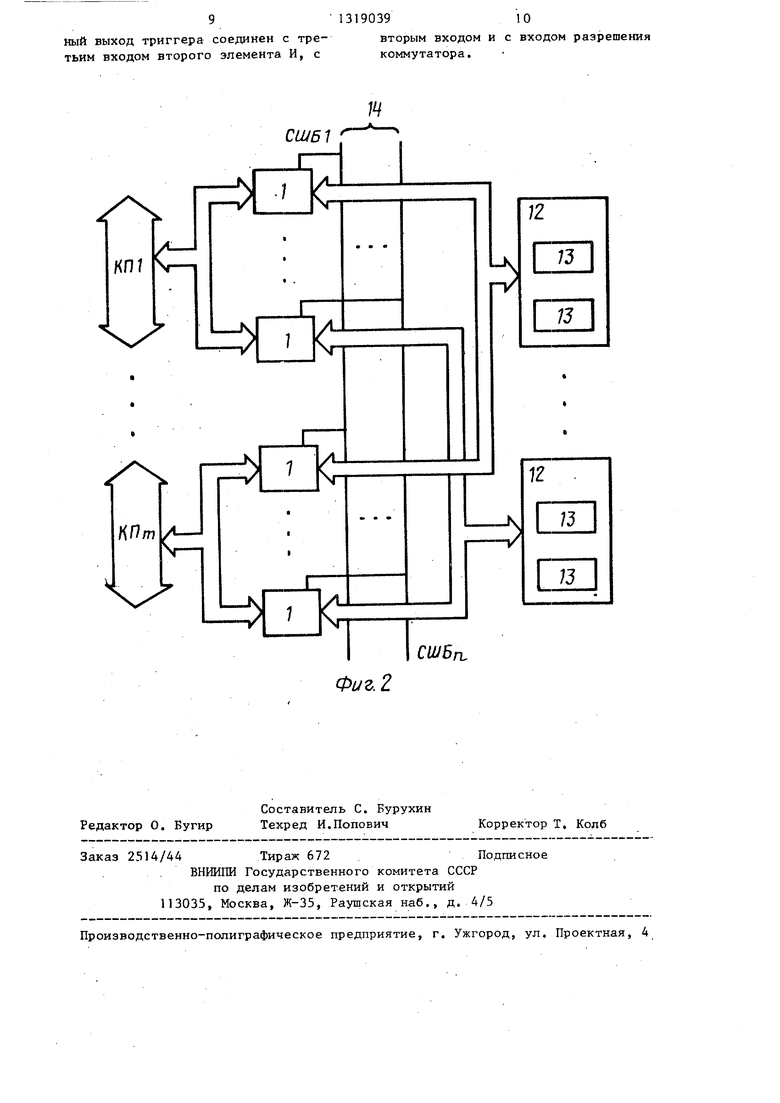

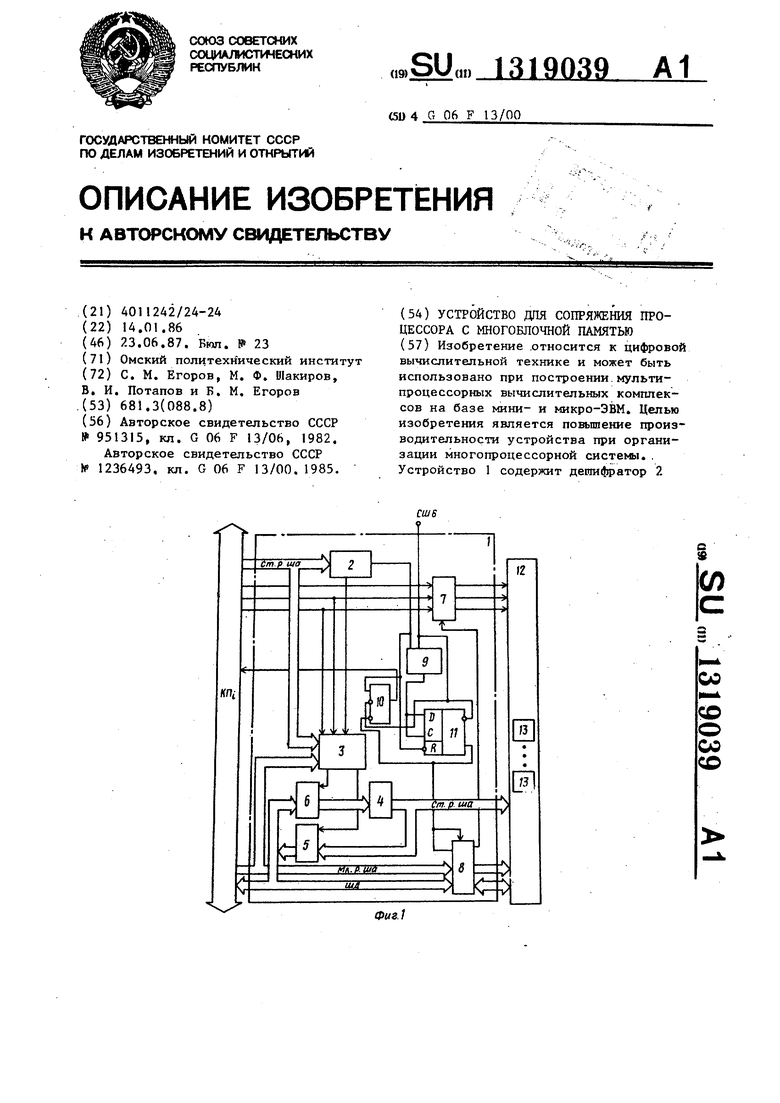

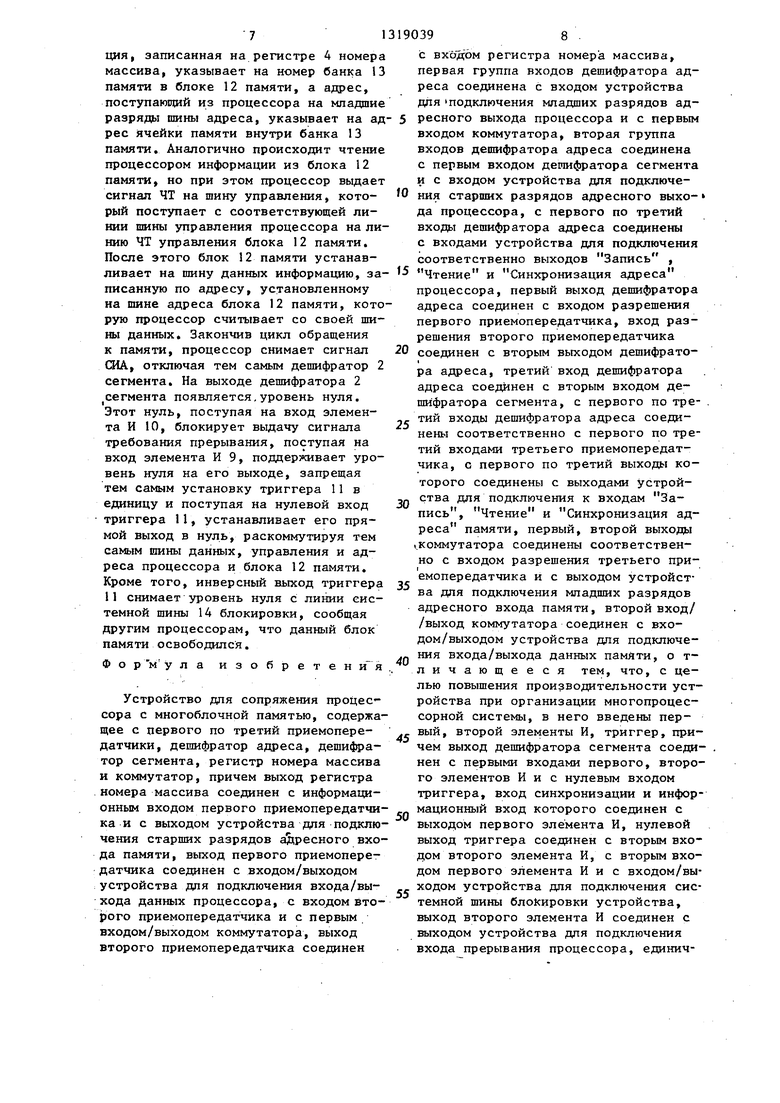

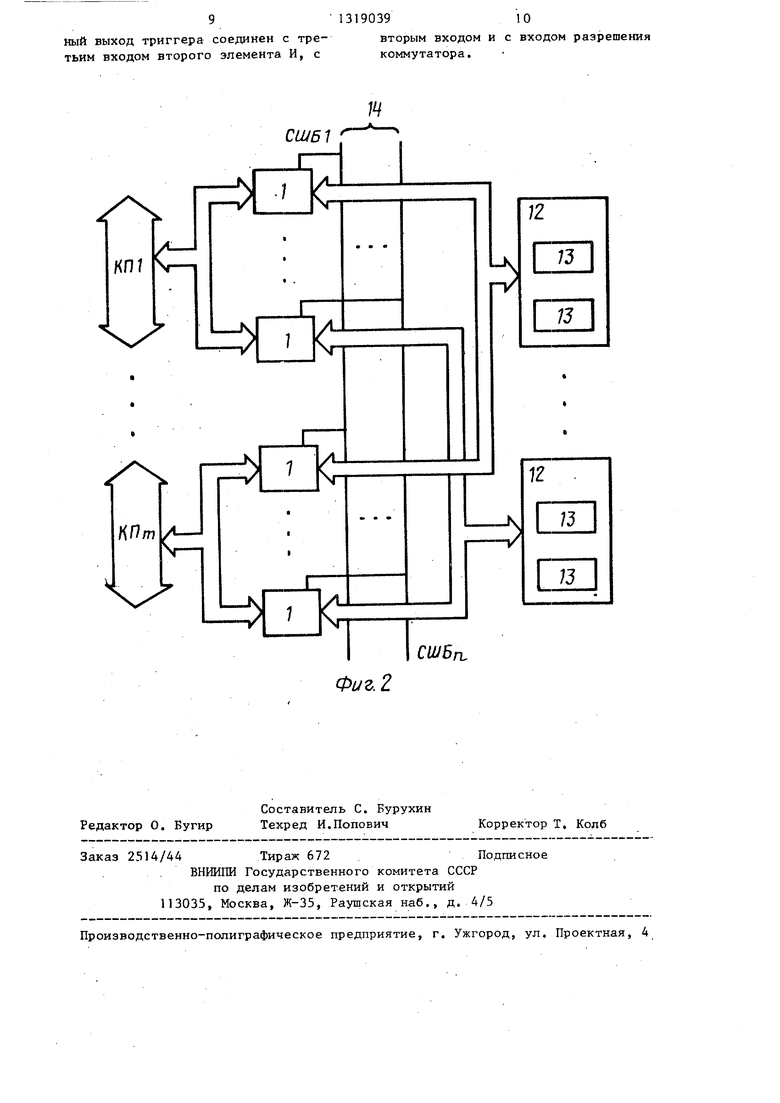

На фиг, 1 представлена блок-схема устройства для сопряжения процессора с многоблочной памятью; на фиг, 2 - структурная схема устройства много- входовой многоблочной памяти.

Устройство 1 для сопряжения процессора с многовходовой многоблочной памятью содержит дешифратор 2 сегмента, дешифратор 3 адреса, регистр. 4 номера массива, с первого по третий приемопередатчики 5-7, коммутатор 8, первый 9 и второй 10 элементы И, триггер 11,

Устройство сопряжения предназначено дпя организации многовходовой многоблочной памяти из одновходовой обычной памяти. Устройство многовходовой многоблочной памяти (фиг, 2) содержит устройство 1 сопряжения, блоки 12 памяти, банки 13 памяти, системные шины 14 блокировки.

Устройство работает следующим образом.

Процессоры могут быть подключены к одному общему одновходовому блоку памяти с помощью устройств 1 сопряжения, входы/выходы запараллелены и подключены к входам/выходам блока памяти, при этом выходы устройств 1 сопряжения соединены с линией системной шины блокировки. Обращение процессоров к общему блоку памяти может осуществляться только последовательно. Когда один из процессоров захватывает общую память, другие процессоры не имеют к ней доступа. Если па

ство реализует разделение адресного пространства многоблочной общей памяти системы и обращение от каждого процессора по независимым дискрипто- рам памяти, 2 ил.

0

15

0

5

0

5

0

мять свободна, об этом свидетельствует наличие уровня единицы на линии системной шины 14 блокировки, процессор, обращаясь к общей памяти, захватывает наивысший приоритет и устройство 1 сопряжения устанавливает на линии системной шины блокировки уровень нуля, сообщая тем самым другим процессорам,, что память захвачена. Если теперь какой-либо процессор обращается к захваченной памяти, соответствующее этому процессору устройство 1 сопряжения вырабатывает сигнал требования прерывания этого процессора с уровнем единицы, сообщая тем самым, что необходимо повторить обращение к памяти либо ожидать, удлиняя тем самым цикл обращения к памяти, освобождения данного блока памяти. Все зависит от возможностей процессора: если процессор не может удлинить свой цикл обращения памяти, то необходимо повторное обращение к памяти. Эти повторные обращения, инициируемые прерыванием, продолжаются до тех пор, пока память не освободится.

Вся область памяти, доступная процессору, разбивается на сегменты, Каждому сегменту ставится в соответствие блок 12 памяти необходимого объема. В каждом конкретном случае сегменты могут иметь переменный размер , Блок 12 памяти состоит из стандартных одновходовых модулей памяти, входы/выход1з1 которых запараллелены и образуют входа/выходы блока 12 памяти Объем каждого блока 12 памяти разбит на равные по объему части- банки 13 памяти, причем объем банка 13 памяти равен сегмента памяти. Сегмент, таким образом, является пространством, через которое процессор имеет доступ к любому банку

31

блока 12 памяти. Процессор соединен с блоками 12 памяти через, специальные устройства 1 сопряжения, функцией которых является анализ захвата блока 12 памяти другим процессором, если нет, то захват свободного блока 12 памяти и выдача на системную шину блокировки сигнала захвата приоритета для других процессоров, подключенных к данному блоку 12 памяти, выдача процессору, обратившемуся к захваченному блоку 12 памяти, сигнала требования прерывания процессора, коммутация канала процессора с каналом свободного блока 12 памяти в момент обращения процессора к блоку памяти и преобразование адреса, поступающего из процессора, т.е. устройство 1 сопряжения заменяет старшие разряды адреса процессора на содержимое своего регистра А номера массива, которое изменяется процессором программно и является значением старших разрядов адреса блока 12 памяти. За счет введения между процессором и памятью устройства 1 сопряжения происходит развязка между адресом, поступающим из процессора, и адресом, поступающим в блок 12 памяти. В результате появляется возможность увеличить количество адресных разрядов, а следовательно, и объем блоков памяти. В определенный момент времени содержимое регистров 4 номера массива в каждом устройстве 1 сопряжения может быть различным и процессор получает доступ к определенному набору банков 13 памяти, причем по одному банку 13 из каждо-го блока 12 памяти. В момент включения устройства 1 сопряжения регистр 4 номера массива устанавливается в нулевое состояние и процессор имеет доступ к нулевым банкам каждого блока 12 памяти За счет разделения всей памяти на независимые блоки реализуется многовхо довая разделенная многоблочная память. Каждый процессор имеет по п сегментов, а следовательно, и по п блоков памяти, кроме того, каждый из блоков памяти является обпщм для нескольких процессоров. За счет этого разделения памяти вероятность того, что в один и тот же момент времени два и более процессора обратятся к одному блоку памяти, зависит от количества блоков памяти и при большом .п является величиной незначительной

394

Р 1/п . Это повышает эффективность использования общей памяти и снижает простои процессоров, возникаюп;ие вследствие ожидания процессором освобож.цения захваченного другим процессором блока памяти. Перед началом обмена процессора с многовходовой многоблочной памятью процессорам необходимо во всех устройствах 1 сопряжения установить на регистрах 4 номера массива номера требуемых банков 13 памяти. Для этого процессор выставляет адрес регистра 4 номера массива на шину адреса. После этого процессор выдает сигнал Синхронизация адреса (СИА), который поступает на управляюпщй вход дешифратора 3 адреса. Последний после прихода сигнала СИА дешифрирует адрес, установленный

на его входах, и после приема управляю11а1х сигналов Запись (ЗП) или Чтение (ЧТ) с шины управления процессора выдает единичный сигнал на один из своих выходов. Если на де- шифратор 3 адреса поступает сигнал ЧТ, то единичный сигнал поступает на разреша1оп1ий вход приемопередатчика 5, разрешая тем самым прохождение информации, записанной на регистре 4

номера массива, на шину данных процессора. Если на дешифратор 3 адреса поступает от процессора сигнал ЗП, дешифратор 3 адреса выдает сигнал на разрешающий вход приемопередатчика 6.

5 После этого процессор устанавливает необходимый номер банка памяти на шину данных, и эта информация записывается в регистр 4 номера массива. После установки номеров банков памя0 ти на регистрах 4 номера массива всех устройств 1 сопряжения процессоры могут обратиться- к любой ячейке установленных банков памяти. При этом нет разницы между работой с мно5 гоблочной памятью и памятью с обычной организацией, так как задержка на дешифраторе 2 сегмента, элементе И 9, триггере II, коммутаторе 8, приемопередатчике 7 не нарушает канапь0 ного цикла обращения процессора к

памяти.

I

Обращение процессора к ячейке блока 12 памяти происходит следующим образом. Процессор подает на шину адреса адрес необходимой ячейки памяти и формирует сигнал СИА. Старшие разряды адреса поступают на вход дешифратора 2 сегмента всех устройств 1

сопряжения, подключенных к данному процессору. Сигнал СИЛ поступает на управляющий вход дешифратора 2 сегмента всех устройств 1 сопряжения, С приходом сигнала СИЛ дешифраторы 2 сегмента каждого устройства 1 сопряжения, подключенного к данному процессору, дешифрирую.т старшие разряды адреса, поступающие на их входы. Дешифратор 2 сегмента, которому соответствует установленный адрес на старших разрядах адреса, выдает управляющий единичный сигнал на первый вход элемента И 10 и на нулевой вход триггера 11, Если на линии системной шины 14 блокировки установлен нуль, т,е, данный блок памяти уже з&хвачен другим процессором, то этот нуль, поступая на вход элемента И 9, поддерживает нулевой уровень на его выходе и блокирует -тем самым установку в единицу триггера 11, а также поступает на вход элемента И 10, Для нормальной работы устройства 1 сопряжения необходимо, чтобы выход триггера 11 захвата приоритета бьш с открытым коллектором, т,е, при наличии уровня единицы этот выход не влиял на подключенные к нему входы, но при наличии уровня нуля этот уровень поддерживается на входах элементов И 10 и 9 и на линии системной шины 14 блокировки. Так как триггер 11 еще не установлен в единицу, уровень нуля с выхода триггера 11 поступает на инверсный вход элемента И 10, В этом случае с выхода элемента И 10 уровен единицы поступает на шину требования прерывания процессора, инициируя тем самым повторное обращение процессора к памяти, либо сообщает процессору, что для нормального продолжения уже начатого цикла необходимо дождаться снятия этого сигнала. Если же на линии системной шины 14 блокировки уровень единицы-(это говорит о том, что этот блок памяти свободен в данный момент времени)i то уровень единицы поступает на вход элемента И 9 и с его выхода, если на его втором входе тоже установлена единица, на информационный и стробирующий входы триггера II, устанавливая тем самым его прямой выход в единицу, С инверсного выхода триггера 11 захвата приоритета уровень нуля поступает на инверсный вход элемента И 10 и на линию системной шины 14 блокировки, сообщая тем самым другим процессорам, подключенным к данному блоку памяти, что этот блок уже захвачен. Теперь этот процессор, захвативший блок памяти, имеет наивысший приоритет при работе с этим блоком памяти и ни один процессор не может прервать его работу с памятью. Сигнал требования прерывания процессора на шине требования прерывания данного устройства 1 сопряжения не возникает, так как на инверсный вход элемента И 10 с выхода триггера 1 поступает уровень единицы, поддерживая на выходе элемента 10 уровень нуля. Далее с выхода триггера 11 единичный уровень поступает на разрешающий и информационный входы коммутатора 8, коммутируя тем самым шины данных и младших разрядов адреса канала выбранного блока 12 памяти. После срабатывания коммутатора 8 управляюпр1й сигнал

поступает на разрешающий вход приеI

мопередатчика 7 с блоком памяти, разрешая прохождение управляющих сигналов ЗП, ЧТ, СИЛ на соответствующие линии шины управления блока памяти, В остальных устройствах 1 сопряжения, подключенных к данному процессору.

прохождение управляющих Сигналов на

0

5

0

5

блоки памяти и коммутация шин данных и младших разрядов адреса процессора и блоков памяти запрещены. После этого процессор устанавливает необходи- 5 мую информацию на шину данных и подает сигнал ЗП на соответствующую линию шины управления. Так как шины данных и младших разрядов адреса процессора и память оказываются соединенными, то информация, установленная на шине данных и младших разрядов адреса, поступает на шину данных и младших разрядов адреса блока 12 памяти, Сигнгш ЗП поступает на вход приемопередатчика 7 и с его выхода на линию ЗП шины управления блока 12 памяти. По сигналу ЗП информация, установленная на щине данных блока 12 памяти, записывается в ячейку блока 12 памяти, адрес которой установлен на шине адреса блока памяти, Информа- ция с выходов регистра 4 номера массива поступает на старшие разряды гчины адреса блока 12. памяти. Младшие разряды шины адреса блока 12 памяти непосредственно соединены с одноименными младишми разрядами шины адреса процессора. Таким образом, информа

-

ция, записанная на регистре 4 номера массива, указывает на номер банка 13 памяти в блоке 12 памяти, а адрес, поступающий из процессора на младшие разряды шины адреса, указывает на ад рее ячейки памяти внутри банка 13 памяти. Аналогично происходит чтение процессором информации из блока 12 памяти, но при этом процессор выдает сигнал ЧТ на шину управления, который поступает с соответствующей линии шины управления процессора на линию ЧТ управления блока 12 памяти. После этого блок 12 памяти устанавливает на шину данных информацию, за писанную по адресу, установленному на шине адреса блока 12 памяти, которую процессор считывает со своей шины данных. Закончив цикл обращения к памяти, процессор снимает сигнал ША, отключая тем самым дешифратор 2 сегмента. На выходе дешифратора 2 сегмента появляется,уровень нуля. Этот нуль, поступая на вход элемента И 10, блокирует выдачу сигнала требования прерывания, поступая на вход элемента И 9, подцерзкивает уровень нуля на его выходе, запрещая тем самым установку триггера 11 в единицу и поступая на нулевой вход триггера 11, устанавливает его прямой выход в нуль, раскоммутируя тем самым шины данных, управления и адреса процессора и блока 12 памяти. Кроме того, инверсный выход триггера И снимает уровень нуля с линии системной щины 14 блокировки, сообщая другим процессорам, что данный блок памяти освободился.

Ф о р м ула изобретен и я

Устройство для сопряжения процессора с многоблочной памятью, содержащее с первого по третий приемопередатчики, дешифратор адреса, дешифратор сегмента, регистр номера массива и коммутатор, причем выход регистра номера массива соединен с информационным входом первого приемопередатчика и с выходом устройства для ПОД1ШЮ- чения старших разрядов гйресного входа памяти, выход первого приемопередатчика соединен с входом/выходом :устройства для подключения входа/выхода данных процессора, с входом вто- приемопередатчика и с первым входом/выходом коммутатора, выход второго приемопередатчика соединен

W

15

25

5 20

30

35

40

45

50

55

с входом регистра номера массива, первая группа входов дешифратора адреса соединена с входом устройства для подключения младших разрядов адресного выхода процессора и с первым входом коммутатора, вторая группа входов дешифратора адреса соединена с первым входом дешифратора сегмента и с входом устройства для подключения старших разрядов адресного выхо- да процессора, с первого по третий входы дешифратора адреса соединены с входами устройства для подключения соответственно выходов Запись , Чтение и Синхронизация адреса процессора, первый выход дешифратора адреса соединен с входом разрешения первого приемопередатчика, вход разрешения второго приемопередатчика соединен с вторым выходом дешифратора адреса, третий вход дешифратора адреса соединен с вторым входом дешифратора сегмента, с первого по тре- , тий входы дешифратора адреса соединены соответственно с первого по третий входами третьего приемопередатчика, с первого по третий выходы которого соединены с выходами устройства для подключения к входам Запись, Чтение и Синхронизация адреса памяти, первый, второй выходы «.коммутатора соединены соответственно с входом разрешения третьего приемопередатчика и с выходом устройства для подключения младших разрядов адресного входа памяти, второй вход/ /выход коммутатора соединен с входом/выходом устройства для подключения входа/выхода данных памяти, о т- личающееся тем, что, с целью повышения производительности устройства при организации многопроцессорной системы, в него введены первый, второй элементы И, триггер, причем выход дешифратора сегмента соединен с первыми входами первого, второго элементов И и с нулевым входом триггера, вход синхронизации и информационный вход которого соединен с выходом первого элемента И, нулевой выход триггера соединен с вторым входом второго элемента И, с вторым входом первого элемента И и с входом/выходом устройства для подключения системной шины блокировки устройства, выход второго элемента И соединен с выходом устройства для подключения входа прерывания процессора, единичНый выход триггера соединен с третьим входом второго элемента И, с

СШ61

х

Фиг. 2

Редактор О. Бугир

Составитель С. Бурухин Техред И.Попович

Заказ 2514/44 Тираж 672 ,Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

вторым входом и с входом разрешения коммутатора.

СШБп,

Корректор Т. Колб

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1571599A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1984 |

|

SU1236493A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1987 |

|

SU1432538A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1557568A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

| Устройство для сопряжения процессора с группой устройств памяти | 1986 |

|

SU1348843A1 |

| Устройство сопряжения процессора с многоблочной памятью | 1989 |

|

SU1702383A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1980 |

|

SU951315A1 |

| Устройство для сопряжения процессоров | 1990 |

|

SU1807495A1 |

Изобретение .относится к цифровой вычислительной технике и может быть использовано при построении.мультипроцессорных вычислительных комплексов на базе мини- и микро-ЭВМ. Целью изобретения является повышение производительности устройства при организации многопроцессорной системы. . Устройство 1 содержит дешифратор 2 00 со о оо со

| Устройство для сопряжения процессора с многоблочной памятью | 1980 |

|

SU951315A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1984 |

|

SU1236493A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1987-06-23—Публикация

1986-01-14—Подача