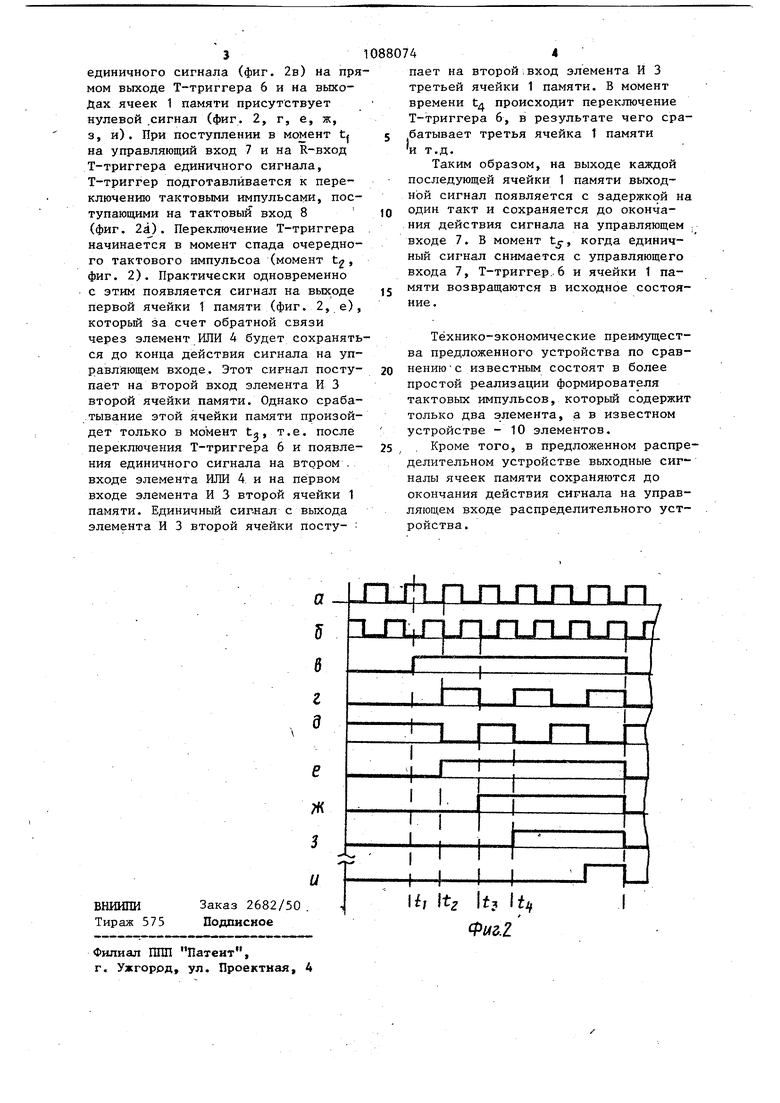

Изобретение О|Тносится к вычислительной технике и может быть использовано как устройство управления станками, технологическими процессами и т.п., если требуется выполнить ряд последовательньгх действий, которые завершаются одновременно. Известен однофазньш двухтактный регистр сдвига, содержащий разрядные, ячейки, каждая из которых состоит из двухвходов1 пс элементов И с инвертором на первом входе, соединенных последовател:зно с элементом Этот регистр сдвига может быть использован в качестве распределительногоустройства. Недостатком такого регистра сдвига является сложность схемного выполнения. Наиболее близким по технической сущности к предлсрсеиному является регистр сдвига, содержащий ячейки памяти, каждая из которых состоит из последовательно соединенных элементов ИЛИ и И, формирователь тактовых импульсов. входы которого соединены с тактовой шиной и шиной сбро са, при этом выход элемента И каждой ячейки памяти соединен с входом элеи последующей ячеек мента ИЛИ данной памяти и является выходом регистра, вход элемента ИЛИ первой ячейки явля ется входом регистра, входы элементов И четных и нечетных ячеек соеди нены с первым и Аторым выходами фор мирователя тактовых импульсов соответственно J . Недостатками известного .регистра сдвига при его использовании в качестве распределительного устройств для выполнения функций управления являются сложность схемного выполнения формирователя тактовых импуль сов, и то,- что выходной сигнал каж.дой ячейки памяти является импульс ным сигналом и не может сохраняться в течение всего интервала времени .действия входного сигналаi Целью изобретения является упрощение устройства Поставленная цель достигается тем, что в распределительном устрой стве (регистре сдвига), содержащем ячейки памяти, каждая из которых состоит из элементов И и ИЛИ, причем выход элемента И каждой ячейки памяти соединен с первым входом эле мента ИЛИ данной ячейки, памяти и распределительного является выходом устройства, выход элемента ИЛИ каждой ячейки памяти соединен с первым входом элемента И данной ячейки памяти, и формирователь тактовых импульсов, содержащий Т-триггер и элемент НЕ, второй вход элемента И ячейки памяти, кроме- первой, соединен с вьгходом элемента И предьодущей ячейки памяти, а второй вход элемента И первой ячейки памяти является управляющим входом распределительного устройства, прямой и инверсный выходы Т-триггера соединены со в.торыми входами элементов ИЛИ нечетных и четных ячеек памяти соответственно, Т-триггера подключен к выходу элемента НЕ, вход которого является тактовым вйодом распределительного устройства, а R-вход Т-триггера подключен к управляющему входу распределительного устройства. На фиг. 1 представлена функциональная йхема предложенного распределительного устройства; на фиг. 2 - временная диаграмма, поясняющая его работу. Распределительное устройство содержит ячейки 1 памяти и формирователь 2 тактовых импульсов. Ячейки состоят из элементов И 3 и ИЛИ 4, а формирователь тактовых импульсов - из элемента НЕ 5 Т-трнггера 6. Выход элемента И 3 каждой ячейки памяти 1 соединен с первым входом элемента ИЛИ 4 данной ячейки памяти, со вторым входом элемента И 3 последующей ячейки памяти и является выходом распределительного устройтсва. Второй вход элемента И 3 первой ячейки памяти является управляющим входом 7 распределитель-. ноге устройства. Выход элемента ИЛИ 4 каждой ячейки памяти соединен с первым входом элемента И 3 данной ячейки памяти. Вторые входы элементов ИЛИ 4 нечетных и четных ячеек памяти соединены с прямым и инверсным выходами Т-триггера 6. Вход элемента НЕ 5 является тактовым входом 8 распределительного устройства, а выход элемента НЕ 5 соединен с Т-входом Т-триггера 6, R-вход которого подключен к управляющему входу 7 распределительного устройства. Распределительное устройство работает следующим образом. В исходном состоянии, т.е. до поступления на управляющий вход 7 единичного сигнала (фиг. 2в) на пря мом выходе Т-триггера 6 и на выходах ячеек 1 памяти присутствует нулевой .сигнал (фиг. 2, г, е, ж, 3, и). При поступлении в момент tj на управляющий вход 7 и на R-вход Т-триггера единичного сигнала, Т-триггер подготавливается к переключению тактовыми импульсами, поступающими на тактовый вход 8 (фиг. 2d). Переключение Т-триггера начинается в момент спада очередного тактового импульсоа (момент t, фиг. 2). Практически одновременно с этим появляется сигнал на выходе первой ячейки 1 памяти (фиг. 2, е), который за счет обратной связи через элемент ИЛИ 4 будет сохранять ся до конца действия сигнала на управлйющем входе. Этот сигнал поступает на второй вход элемента И 3 второй ячейки памяти. Однако срабатывание этой ячейки памяти произойдет только в момент t, т.е. после переключения Т-триггера 6 и появления единичного сигнала на втором . входе элемента ИЛИ 4 и на первом входе элемента И 3 второй ячейки 1 памяти. Единичный сиг-нал с выхода элемента И 3 второй ячейки посту- 44 пает на второй i вход элемента И 3 третьей ячейки 1 памяти. В момент времени t происходит переключение Т-триггера 6, в результате чего срабатывает третья ячейка 1 памяти и т.д. Таким образом, на выходе каждой последующей ячейки 1 памяти выходной сигнал появляется с задержкой на один такт и сохраняется до окончания действия сигнала на управляющем , входе 7. В момент t, когда единичный сигнал снимается с управляющего входа 7, Т-триггер. 6 и ячейки 1 памяти возвращаются в исходное состояние. Технико-экономические преимущества предложенного устройства по сравнениюС известным состоят в более простой реализации формирователя тактовых импульсов, который содержит только два элемента, а в известном устройстве - 10 элементов. . Кроме того, в предложенном распределительном устройстве выходные сигналы ячеек памяти сохраняются до окончания действия сигнала на управляющем входе распределительного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор времяимпульсных кодов | 1991 |

|

SU1807562A1 |

| Регистр сдвига | 1979 |

|

SU855732A1 |

| Устройство задержки | 1990 |

|

SU1750036A1 |

| Регистр сдвига | 1988 |

|

SU1539841A1 |

| Устройство для исследования оперативной памяти | 1986 |

|

SU1404059A1 |

| Вычислительное устройство | 1980 |

|

SU1001090A1 |

| Симметричный делитель частоты импульсов | 1982 |

|

SU1089763A2 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2527188C1 |

| Устройство для передачи и приема команд телеуправления | 1988 |

|

SU1667135A1 |

| Устройство для отображения информации на экране электроннолучевой трубки | 1988 |

|

SU1695370A1 |

РАСПРЕДЕЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее ячейки памяти, каждая из которых состоит из,элементов И и ИЛИ, причем выход элемента И каждой ячейки памяти соединен с первым вхо дом элемента ИЛИ данной ячейки памяти и является выходом распределительного устройства, выход элемента ИЛИ каждойячейки памяти соединен с первым, входом элемента И данной ячейки памяти, и формирователь тактовых импульсов, содержащий Т-триггер и элемент НЕ, отличающийся тем, что, с целью Упрощения устройства, второй вход элемента И каждой ячейки памяти, кроме первой, соединен с выходом элемента И предыдущей ячейки памяти, а второй вход элемента И . первой ячейки памяти является управ. ляющим входом распределительного устройства, прямой и инверсный выходы Т-триггера соединены с вторыми § входами элементов ИЛИ нечетных и четных ячеек памяти Соответственно, (Л Т-вход Т-триггера подключен к выходу элемента НЕ, вход которого является тактовым входом распределительного устройства, а R-вход Т-триггера подключен к управляющему входу распределительного устройства. 00 00 о 4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Букреев И.Н | |||

| идр | |||

| Микройлёктронные схемы цифровых устройств, М., Советское радио, 1975, с | |||

| Способ подпочвенного орошения с применением труб | 1921 |

|

SU139A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Регистр сдвига | 1979 |

|

SU855732A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-04-23—Публикация

1982-11-16—Подача