(54J НЕЛИНЕЙНОЕ КОРРЕКТИРУЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Нелинейное корректирующее устройство | 1979 |

|

SU866539A1 |

| Устройство для измерения параметров динамического объекта | 1978 |

|

SU777599A1 |

| Устройство для преобразования сигналов в системах управления | 1977 |

|

SU641485A1 |

| НЕЛИНЕЙНОЕ КОРРЕКТИРУЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU377725A1 |

| Устройство измерения сдвига фаз между двумя сигналами | 1978 |

|

SU702315A1 |

| Нелинейное корректирующее устройство с фазовым опережением | 1988 |

|

SU1718182A1 |

| Способ преобразования переменного напряжения в постоянное и устройство для его осуществления | 1981 |

|

SU966827A1 |

| Асинхронный электропривод | 1975 |

|

SU809461A1 |

| Электропривод с асинхронной машиной с фазным ротором | 1975 |

|

SU610275A1 |

| Способ управления электроприводом постоянного тока | 1982 |

|

SU1150721A1 |

1

ИзобС«етение относится к технике систем автоматического регулирования, в частности к нелинейным коррек тирующим устройствам, и предназначено для повшиения помехоустойчивости и точности систем управления летательных аппаратов.

Известно что сигналы в системах управления летательными аппаратами, представляют собой обычно сумму постоянных составляющих и гармонической составляющей,частота которой изменяется в широких пределах. При этом, если частота гармоничег;кой составляющей меньше частоты среза ) Шо , она считается полезным сигналом. В противном случае частота считается помехой и должна быть отфильтрована .

фвёстно корректирующее устройство, позволякнцее йодавлять гармоническую составляющую входного сигнала t.

Недостатком его является то, что в нем Осуществляется подавление гармонической составляклцей лишь фиксированной частоты.

Нгшболее близким к предлагаемому является нелинейное корректирукицее устройство, содержащее блок мажоритарной логики, последовательно соединенные первое дифференцирующее звено и инвертор, а также сумматор и второе дифференцирующее звено,вход которого соединен с первым входом сумматора 2 .

Недостатком известного устройства . является недостаточная помехоустойчивость за счет нелинейных искаже10ний формы сигнала.

Цель изобретения - повьпиение помехоустойчивости нелинейного корректирующего устройства.

Поставленная цель достигается

15 тем, что в устройство введено множительно-делительное звено, причем выход второго дифференцирующего з-вена соединен с первым входом блока мажоритарной логики, входом первого

20 дифференцирукяцего звена и первым входом множительно-делительного звена, второй вход которого соединен с выходом блока мажоритарной логики, третий вход - с выходом инвертора и

25 вторым входом блока мажоритарной логики, а выход - с вторым входом сумматора.

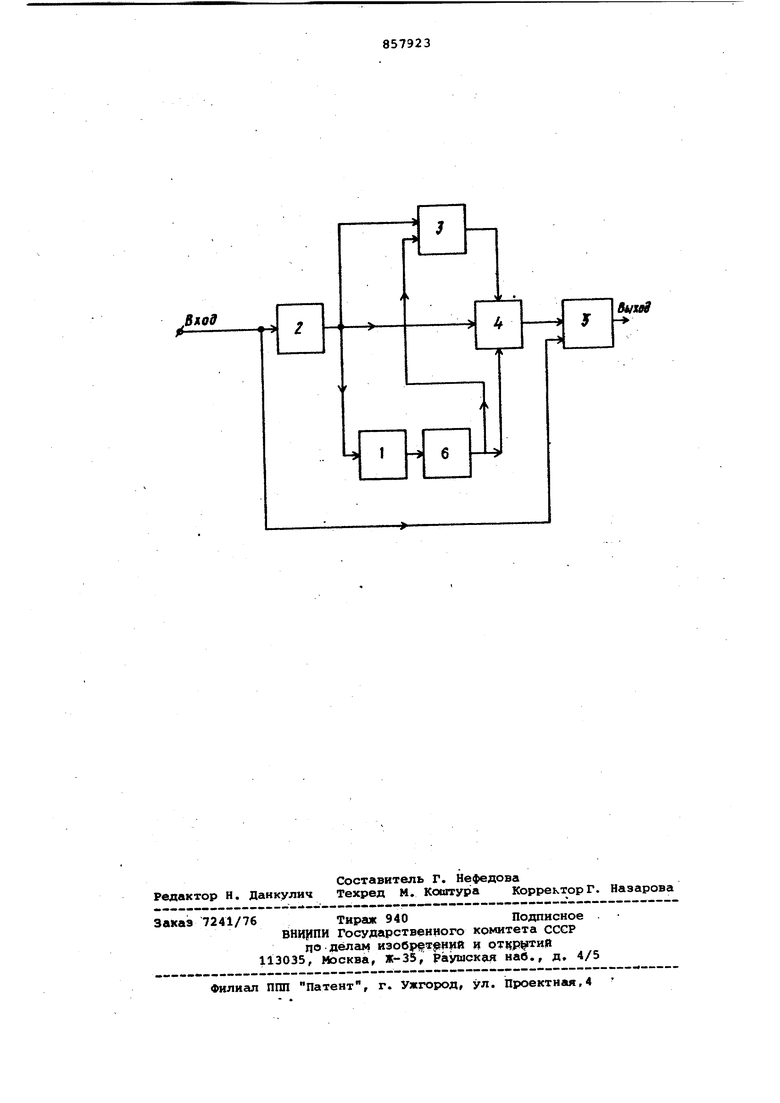

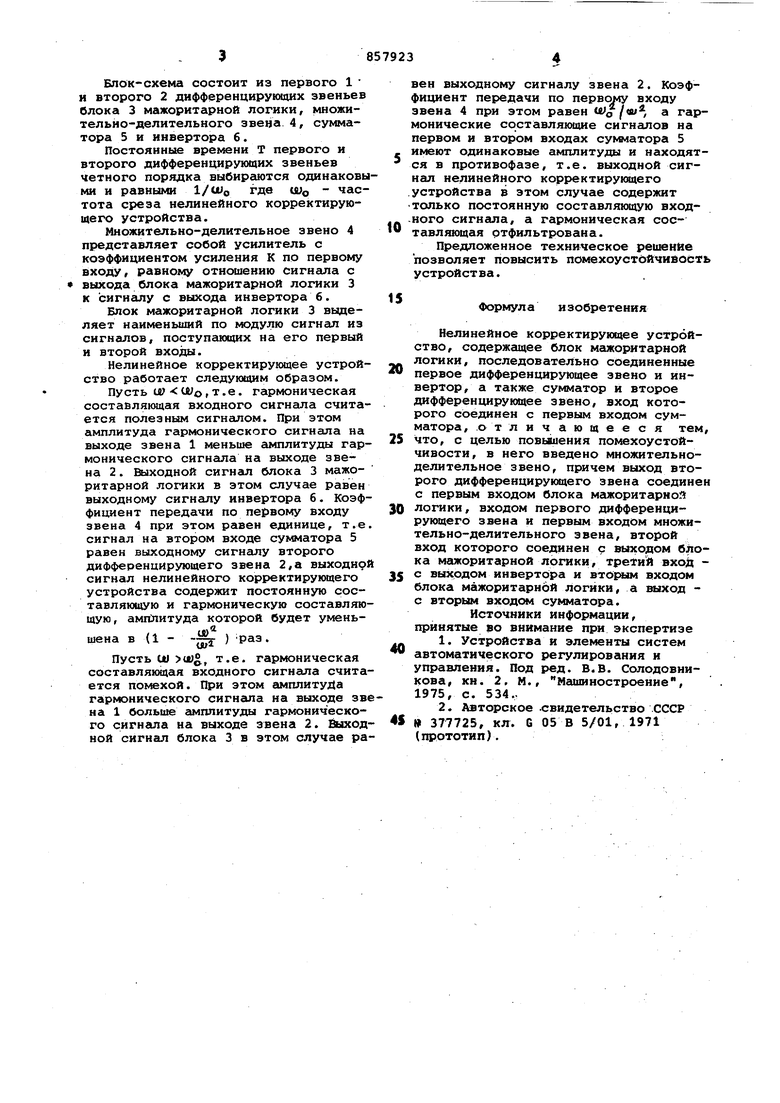

На чертеже представлена блок-схема нелинейного корректирующего устрой30ства.

Блок-схема состоит из первого 1 и второго 2 дифференцирующих звеиьев блока 3 мажоритарной логики, множительно-делительного звеца 4, сумматора 5 и инвертора 6.

Постоянные времени Т первого и второго дифференцирующих звеньев четного порядка выбираются одинаковыми и равными 1/cUo где Шо - частота среза нелинейного корректирующего устройства.

Множительно-делительное звено 4 представляет собой усилитель с коэффициентом усиления К по первому входу, равному отношению сигнала с выхода блока мажоритарной логики 3 к сигналу с выхода инвертора 6.

Блок мажоритарной логики 3 выделяет наименьший по модулю сигнал из сигналов, поступающих на его первый и второй входы.

Нелинейное корректирующее устройство работает следующим образом.

Пусть (jU Шо, т.е. гармоническая составляющая входного сигнгша считается полезным сигналом. При этом амплитуда гармонического сигнала на выходе звена 1 меньше амплитуды гармонического сигнала на выходе звена 2 . исходной сигнал блока 3 мажоритарной логики в этом случае равен выходному сигналу инвертора 6. Коэффициент передачи по первому входу звена 4 при этом равен единице, т.е. сигнал на втором входе сумматора 5 равен выходному сигнгшу второго дифференцирующего звена 2,а выходной сигнал нелинейного корректирующего устройства содержит постоянную составляющую и гармоническую составляющую , амплитуда которой будет умень1Х

шена в (1 ) раз. Пусть Ш т.е. гармоническая составляющая входного сигнала считается помехой. При этом амплитуда гармонического сигнала на зве на 1 больше амплитуды гармонического сигнала на выходе звена 2. Выходной сигнал блока 3 в этом случае равен выходному сигналу звена 2. Коэффициент передачи по первому входу звена 4 при этом равен а гармонические составляющие сигналов на первом и втором входах сукматора 5 имеют одинаковые амплитуды и находятся в противофазе, т.е. выходной сигнал нелинейного корректирукнцего .устройства в этом случае содержит только постоянную составляющую вход-ного сигнала, а гармоническая составляющая отфильтрована.

Предложенное техническое решение позволяет повысить помехоустойчивост устройства.

Формула изобретения

Нелинейное корректирующее устройство, содержащее блок мажоритарной логики, последовательно соединенные

первое дифференцирующее звено и инвертор, а также сумматор и второе дифференцирующее звено, вход которого соединен с первым входом сумматора, отличающееся тем,

что, с целью повышения помехоустойчивости, в него введено множительноделительное звено, причем выход второго дифференцирукицего звена соединен с первым входом блока мгмсоритарной

логики, входом первого дифференцирукяцего звена и первым входом множительно-делительного звена, второй вход которого соединен с выходом бЛока мажоритарной логики, третий вхоЬ с выходом инвертс ра и ВТОЕШМ входом блока мажоритарной логики, а выход с вторым входом сумматора.

Источники информации, принятые во внимание при экспертизе

автоматического регулирования и

управления. Под ред. в.В. Солодовникова, кн. 2. М., Машиностроение, 1975, с. 534.,

О 377725, кл. G 05 В 5/01, 1971 (прототип).

.Вяод

Bt/xe9

Авторы

Даты

1981-08-23—Публикация

1977-11-18—Подача