(54) УСТРОЙСТВО ДЛЯ ВЫВОДА ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| Кольцевая система для обмена информацией | 1988 |

|

SU1550522A1 |

| Устройство для обмена информацией | 1986 |

|

SU1336017A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения ЭВМ с различными регистрирующими устройствс ш в старт-стопном режиме параллельно-последовательного вывода информации.

Известно устройство вывода информации, содержащее два регистра, коммутатор, дешифраторы, триггеры, элементы И,ИЛИ, НЕ, ИЛИ-НЕ и усилители 1 .

Недостаток устройства - значительное количество оборудования.

Наиболее близким к предлагаемому по технической сущности и достигаемому эффекту является устройство для выводе информации, содержащее регистр r.ijiieMa информации, восемь входов которого соединены с информационным выходом ЭВМ девятый выход ЭВМ соединен с входом блока включения УВЛ и с синхронизирующим входом регистра приема, при этом восемь выходов регистра приема соединены с первыми входа1 ш вентилей, вторые входы которых соединены с выходом первого триггерч управления, выходы вентилей соединены с входами кодовых усилителей, выходы KOTopJX подключены к кодовым электромагнитам перфоратора, выходпервого синхронизирующего сигнала перфоратора подключен к первому входу первого триггера управления и к первому входу второго триггера управления, выход второго синхронизирующего сигнала перфоратора подключен ко второму входу первого триггера управления, а также к первому входу управляющего вентиля, выход

10 третьего синхронизирующего сигнала пе.рфоратора - ко второму входу второго триггера управления, выход которого подключен ко второму входу управляющего вентиля,.его выход сое15динен с первым входом третьего триггера управления и с десятым входом регистра приема, второй вход третьего триггера управления и его выход соединены с управляющей шиной уст20ройства 2 .

Недостаток устройства состоит в том, что оно требует значительных затрат оборудования для его реализации .

25

Цель изобретения - сокращение оборудования.

Поставленная цель достигается тем, что в устройство вывода информации, содержащее регистр приема,

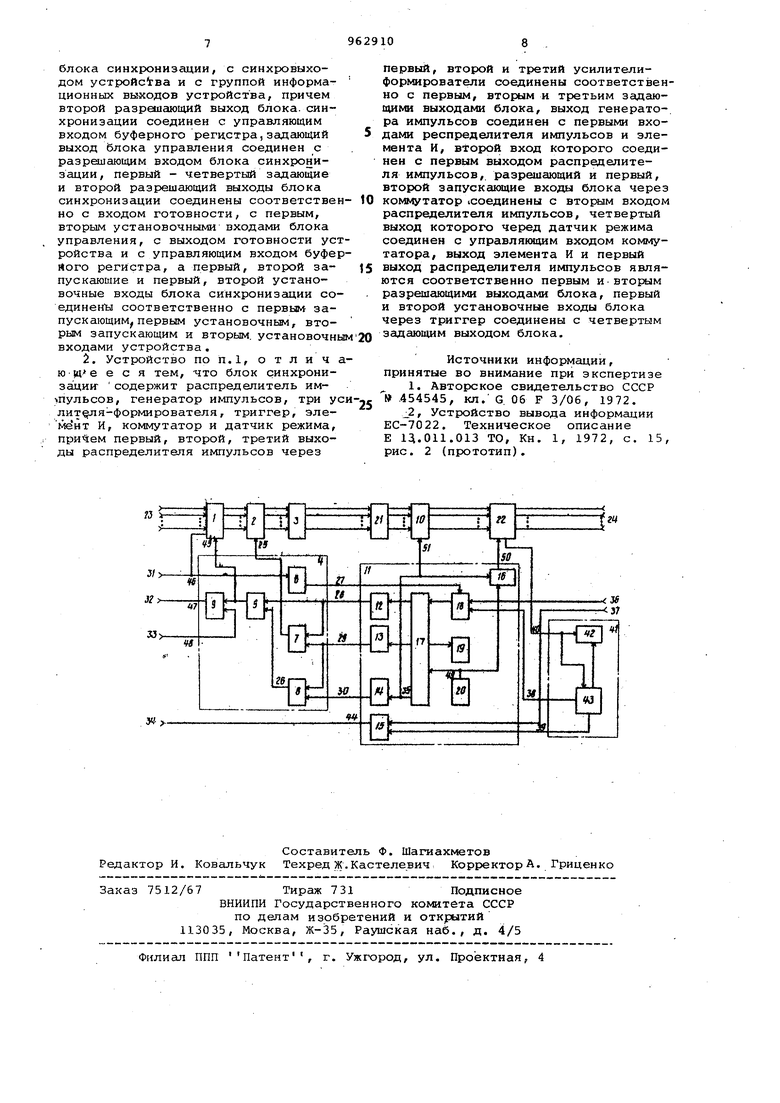

30 первый управляющий вход которого соединен с обнуляющим выходом блока уп равленйя, блок элементов И, управля щий эход которого соединен с разреш ющим выходом блока управления, преобразователь кода, причем первый вхо устройства соединен с вторым управЛ ющим входом регистра приема и с запускающим входом блока управления, второй вход устройства соединен с тактовым входом блока управления, группа входов устройства соединена с информационными входами регистра приема, выходал регистра приема соеди нены с информационными входами блок элементов И, выходы блока элементов .(Соединены с входами группы усилителе а сигнальным выходом устройства является запросный выход, блока управления , введены блок.синхронизации, , буферный регистр и блок согласования уровней, причем входы и выходы блока согласования уровней соединены соот.ветс.твенно с выходами груп11Ы усилит лей и с информационными входами буферного регистра,выходы которого соедине ны с информационными входами преобразо вателя параллельно-последовательного кода, управляющий вход выход и группа выходов которого соединены соот.ветственно с первым разрешающим выходом блока синхронизации,с вторым вы ходом устройства и -с группой выходов устройства, причем второй разрешающий выход блока синхронизации соединен с управляющим входом буферного регистра, задающий выход блока управления соединен с разрешающим входом блока Синхронизации, первый - четвер тый задающие и второй разрешающий выходы блока синхронизации соединены соответственно с входом готовности , с первым, вторым установочными звхода ми блока управления, с третьим выходом устройства и с управляющим входом буферного регистра, а первый, второй запускающие и первый, второй установочные входы блока синхронизации соединены соответственно с треть им - шестым входами устройства. Кроме того, блок синхронизации .содержит распределитель импульсов, генератор импульсов, три усилителяформирователя, триггер, элемент И, коммутатор и датчик режима, причем первый, второй, третий выходы распредепи еля импульсов через первый, второй и третий усилители-формирователи соединены соответственно с первым, вторым и третьим задающимивыходами блока, выход генератора импульсов соединен с первыми входами распределителя импульсов и элемента И, второй вход которого соединей с первым выходом распределителя импуль сов, разрешающий и первый, второй запускающие входы блока через коммутатор соединены с вторым входом распредегителя импульсой, четвертый вы ход которого через датчик режима соединен с управляющим входом коммутатора, выход элемента И и первый выход распределителя импульсов являются соответственно первым и вторым разрешающими выходами блока, первый и второй установочные входы блока через триггер соединены с четвертым задающим выходом блока. На чертеже представлена структурная схема устройства. Устройство вывода информации соде1мсит регистр 1 приема, блок 2 элементов И, группу 3 усилителей, блок 4 управления, выполненный в виде элемента. ИЛИ-НЕ 5, усилителя б, триггеров 7-9, буферный регистр 10, блок 11 синхронизации, выполненный в виде усилителей-формирователей 12-14, триггера 15, элемента И 16, распределителя 17 импульсов, коммутатора 18, датчика 19 режима, генератора 20 импульсов, блок 21 согласования уровней, преобразователь 22 кода, группу 23 ;входов, группу 24 выходов, управляю- . щий вход 25 блока элементов И 2, выход триггера 8, разрешающий вход 27, первый, второй, третий задающие выходы 28-30 блока синхрюнизации, пер.вый вход 31 у.стройства, первый выход 32 устройства, второй вход 33 устройства, третий выход 34 устройства, управляющий вЛод 35 буферного регистра 10, третий вход 36 устройства, Которлй является первым запускающим входом блока синхронизации, четвертый вход 37 устройства,являются первым установочным входом блока синхронизации, пятый вход 38 устройства, он же второй запускающий вход блока синхронизации, шестой вход 39 устройства, являются вторым,установочным входом блока синхронизации, второй выход 40 устройства. На схеме такде обозначено регистрирующее устройство 41, содержащееблоки 42 и 43 управления. УЬтройство вывода содержит выход 44 готовности блока синхронизации, обнуляющий выход 45 блока управления, запускающий вход 46 блока управления, запросный выход 47 блока управления, тактовый вход 48 блока управления, выход 49 генератора импульсов, первый 50 и второй 51 разрешающие выходы блока управления. . По сигналу Начальный сброс с блока 43 управл.ения регистрирующего устройства 41 ввдается на вход 39 сигнал на триггер 15, с выхода 44 которого выставляется признак Устройство готово (выход 34 устройства) . По обнаружению этого сигнала из ЭВМ повходу 31 вьщается сигнал Пуск на вход усилителя 6 блока 4. С выхода усилителя 6 по входу 27 блока 11 это.т сигнал выдается на вход коммутатора 18, включающего распреяелитель 17 импульсов. В результате этого распределитель 17 вырабатывает однократную последовательность сигналов: прием кода, начало цикла, готовность ГПРК , НЦ , Т ), поступающих на входы усилителей-формдрователей 12-14 счастотой генератора 20. Сигнал 29 с выхода усилителя-формирователя 13 включае т триггер 7 и сбрасывает триггер 8. С выхода 25 выдается сигнал на блок 2 элементов И Сигнал 30 включает триггер 8, выход 26 которого разрешает прохождение синосронизирутощего сигнала 28, поступающего с выхода усилителя-формирователя 12. Этот сигнал включает триг- . гер 9 Требование информации и сбрасывает регистр приема.1 и триггер 7, т.е. устройство подготавливается к приему информации от ЭВМ. В результате этого на выходе 32 выставляется требование на прием информации от ЭВМ.

ЭВМ выдает по входу 33 сигнал сброса триггера 9 Требование информации и по.входу 31 сигнал синхронизации записи первого байта информации , поатупающего параллельным кодом по входам 23 на вход регистра 1 приема информации.

Таким образом, по сигналу 31 Пуск в регистр 1 приема .будет записан первый байт информации. При включении регистрирующего устройства 41 в режим Работа оно выдает на вход 38 блока 11 с.игнал ,3аПо э.тому сигналу коммутатор.

прос

18 включает распределитель 17 импулсов. В этом случае сигнал 29 включает триггер 7 и выключает триггер 8.

С выхода. 25 выдается сигнал на блок 2 элементов И. Код информации с выходов этого блока поступает на входы усилителей 3 и далее через блок 21 производится запись первого байта информации в буферный регистр 10.

Синхронизирующий сигнал на входе 30 повторно включает триггер 8, выход 26 которого разрешает прохождение сигнала со входа 28 на вход тригера 9 Требов.ание через элемент ИЛИ-НЕ 5 блока 4. Этот же сигнал, поступающий на вход 35, переписывает информацию с буферного регистра 10 в преобразователь 22 кода и .включает элемент И 16, навторой вход которого поступают импульсы генератора 20.

Элемент И 16 вырабатывает сигнал управляющий выдачей преобразователем кода 22 параллельно-последовательного кода (параллельный код по выходам 24, последовательный код по выходу 40). В рассматриваемом примере для фотокооряинатографа Итоп - ЗП последовательный код поступает на выход.40, т.е. на входы

блока управления модуляцией луча 42 и блока 43 управления регистрирующего устройства 41, который вырабатывает на вход 39 сигнал Устройство готово и на вход 38 сигнал Запрос следующего байта информации. Синхронизирующий сигнал с выхода 28 сбрасывает триггер 7 в исходное состояние и через элемент ИЛИ-НЕ 5 блока 4 сбрасывает регистр 1 приема

и включает триггер 9 Требование информации , а на выходе 32 выставляется требование следующего байта инjl)opмaции от ЭВМ,

Далее алгоритм работы устройства

1повторяется, т.е. происходит стартстопный прием информации по мере ее отработки регистрирующим устройством и вьщачей им сигнала запрос последующих байтов информации.

Прием информации заканчивается в случае отсутствия сигналов Запрос, Устройство готово и Пуск .

Датчик 19 режима предназначен для выработки распределителем 17 непрерыв.ной или старт-стопной последовательности синхронизирующих сигналов.

Формула изобретения

30

ющий вход которого соединен с разрешающим выходом блока управления, преобразователь параллельно-последовательного кода, причем первый синхровход устройства соединен с втором yri40 равляющим входом регистра приема и с запускающим входом блока управления, второй синхровход устройства соединен с тактовым входом блока управления, группа входов устройства

45 соединена с информационными входами регистра приема, выходы регистра приема соединены с информационным входаи м блока элементов И, выходы блока элементов И соединены с входа5Q ми группы усилителей, а сигнальным выходом устройства является запросны выход блока управления, о т л и ч аю щ е е с я тем, что, с целью сокра;щения оборудования,оно содержит блок

ее синхронизации,буферный регистр и бло согласования уровней,причем входы и выходы блока согласования уровней соединены соответственно с выходами группы усилителей и с информационными входаиий буферного регистра, вы60ходы которого соединены с информационными входами преобра.зователя параллельно-последовательного кода, управляющий вход, выход и группа выходов которого соединены соответственно с первым разрешающим выходом

блока синхронизации, с синхровыходом устройс4-ва и с группой информационных выходов устройства, причем второй разрешающий выход блока, синхронизации соединен с управляющим входом буферного регистра,задающий

выход блока управления соединен с разрешающим входом блока синхронизации, первый - четвертый задающие и второй разрешающий выходы блока синхронизации соединены соответственно с входом готовности, с первым, вторым установочными входами блока управления, с выходом готовности устройства и с управляющим входом буферного регистра, а первый, второй запускаюшие и первый, второй установочные входы блока синхронизации соединены соответственно с первым запуск ающим первым установочньни, вторым запускающим и вторым, установочным входами устройства .

первый, второй и третий усилителиформирователи соединены соответственно с первым, вторым и третьим задающи1Ю1 выходами блока, выход генератора импульсов соединен с первыми входами распределителя импульсов и эле1 нта И, второй вход которого соединен с первым выходом распределителя импульсов, разрешающий и первый, второй запускакицие входы блока через коммутатор «соединены с вторым входом распределителя импульсов, четвертый выход которого черед датчик режима соединен с управляннцим входом коммутатора, выход элемента И и первый выход распределителя импульсов являются соответственно первым и-вторым разрешгиощими выходами блока, первый и второй установочные входы блока через триггер соединены с четвертым задающим выходом блока.

Источники информации, принятые во внимание при экспертизе

2, Устройство вывода информации ЕС-7022. Техническое описание Е 1Д.011.013 ТО, Кн. 1, 1972, с. 15 рис. 2 (прототип).

Авторы

Даты

1982-09-30—Публикация

1980-04-01—Подача