J(54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ДЛЯ ПОВОРОТА

ВЕКТОРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство для поворота вектора | 1987 |

|

SU1520511A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1370653A1 |

| Устройство для деления | 1990 |

|

SU1742815A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Преобразователь координат | 1988 |

|

SU1566345A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU883897A1 |

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

| Устройство для вычисления направляющих косинусов вектора в пространстве | 1982 |

|

SU1164700A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

I

Изобретение относится к цифровой вычислительной технике и может быть использовано для выполнения операции поворота вектора в сэпециалиэированных процессорах.

Известно вычислительное устройство, содержащее четыре сумматора-вычйтателя, коммутирующих блока, два регистра сдвига. Это устройство вьтолняет поворот вектора с одновременной коррекцией результата 11 и 2.

Недостатком этого устройства является большой объем оборудования.

Наиболее близким по технической сущности к предлагаемсшу изобретению является вычислительное ус юйство для поворота вектора, содержащее два сумматора-вычйтателя, выходы которых соединены соответственно с входами первого и второго регистров, выходы которых соединены с первыми входами первого и второго сдвигателей соответственно, первые входы первого и второго мультиплексоров являются входами устройства, выходы первого и второго регистров являются выходами устройства и соединены с первыми входами соответственно первого и второго сумматоров -вычитателей, а

также с входами соответственно третьего и четвертого регистров, выходы которых соединь ны со вторыми входами второго и первого мультиплексоров соответственно, выходы первого мультиплексора и первого сдвигателя через nepBjao группу элементов И соединены с вторым входом второго сумматора-вычйтателя, а выходы второго мультиплексора и второго сдвигателя через вторую группу элементов И соединены с вторым входом первого сумматора-вычйтателя.

to при этом управляющие входы первого и второго мультиплексоров соединены вместе и являются первым кодовым входом устройства, управляющие входы первого и второго сдвигателей также соединены вместе и являются вторым кодоISвым входом устройства, управляющие входы первого и второго сумматоров-вычитателей являются соответственио третьим и четвертым кодовыми входами устройства.

Это устройство обеспечивает поворот векто20ра, заданного своими проекциями, которые представляются п-разрядными двоичными числами и, коррекцию результата поворота. Пово рот и коррекш1я в этом устройстве вьтолняготся последовательно, затрачивая на обе эти операции 2п итераций 3. Недостатком этого устройства является низкое быстродействие, объяснимое большим временем коррекции результата поворота, которое может еще больше увеличиваться из-за необходимости проведения дополнительно подготови тельных пересылок информации между регистрами. Цель изобрететш - увеличение быстродействия устройства. Указанная цель достигается тем, что в вычислительное устройство для поворота вектора, содержащее четыре регистра, два мультиплексора, два сумматора вычитателя, выходы которых соединены с входами соответственно первого и второго регистров, выходы которых соединены с информационными входами первого и второго сдвигателей соответственно, первые информационные входы первого и второго мультиплексоров являются информационными входами устро ства, вторые информационные входы первого и второго мультиплексоров соединены с выходами соответственно третьего и четвертого регистров, Заправляющий вход первого мультиплексора и управляющий вход первого сдвигателя являются соответственно первым и вторым управляющим входами устройства, а управляющие входы первого и второго сумматоров-вычитателей соответ ственно - третьим и четвертым зшравляющими входами устройства, введены пятый и шестой регистры, при этом вход пятого регистра соеди нен с входами первого и четвертого регистров, а выход пятого регистра соединен с третьим и четвертым информационными входами первого мультиплексора, вход шестого регистра соединен 35

с входами второго и третьего регистров, а вьь ход шестого регистра соединен с третьим информационным входом второго мультиплексора, четвертый информационный вход которого соединен с выходом третьего регистра, выходы первого и второго мультиплексоров соединены с первыми информационными входами соответственно первого и второго сумматоров-вычитателей, вторые информационные входы которых соединены с выходами соответственно первого и второго сдвигателей, выходы сумматоров-вычитателей являются информационными выходами устройства, управляющие входы второго мультиплексора и второго сдвигателя являются соотретственно пятым и шестым управляющими входами устройства.

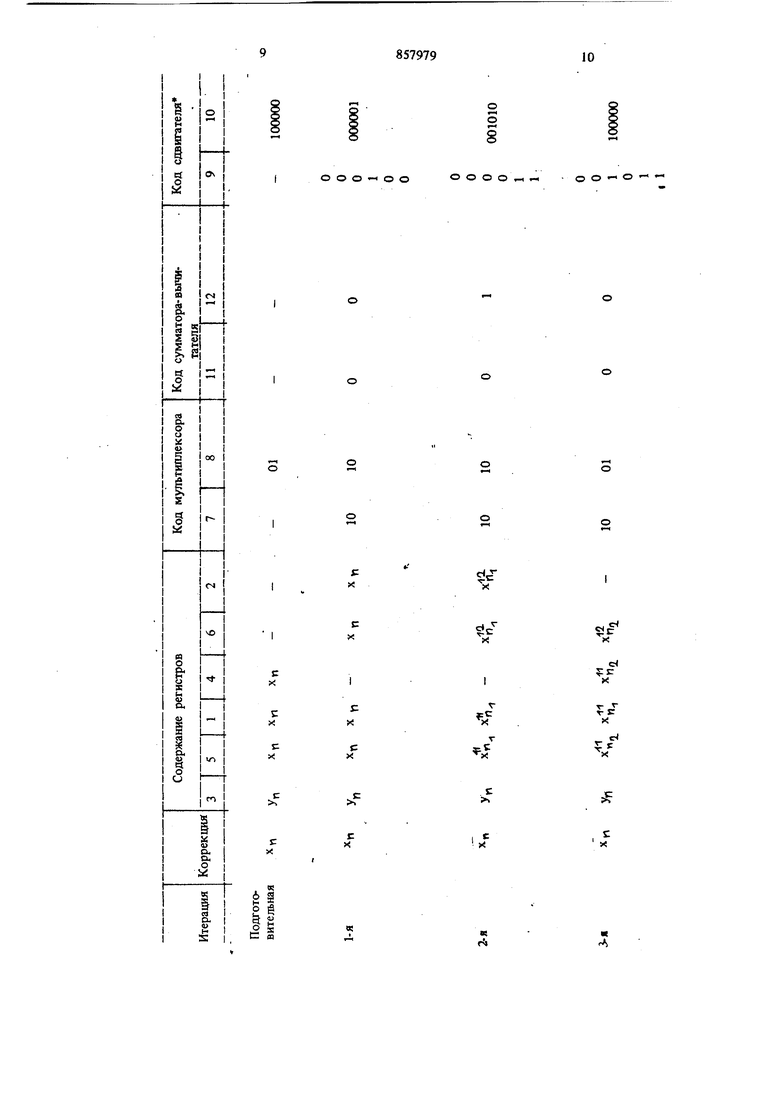

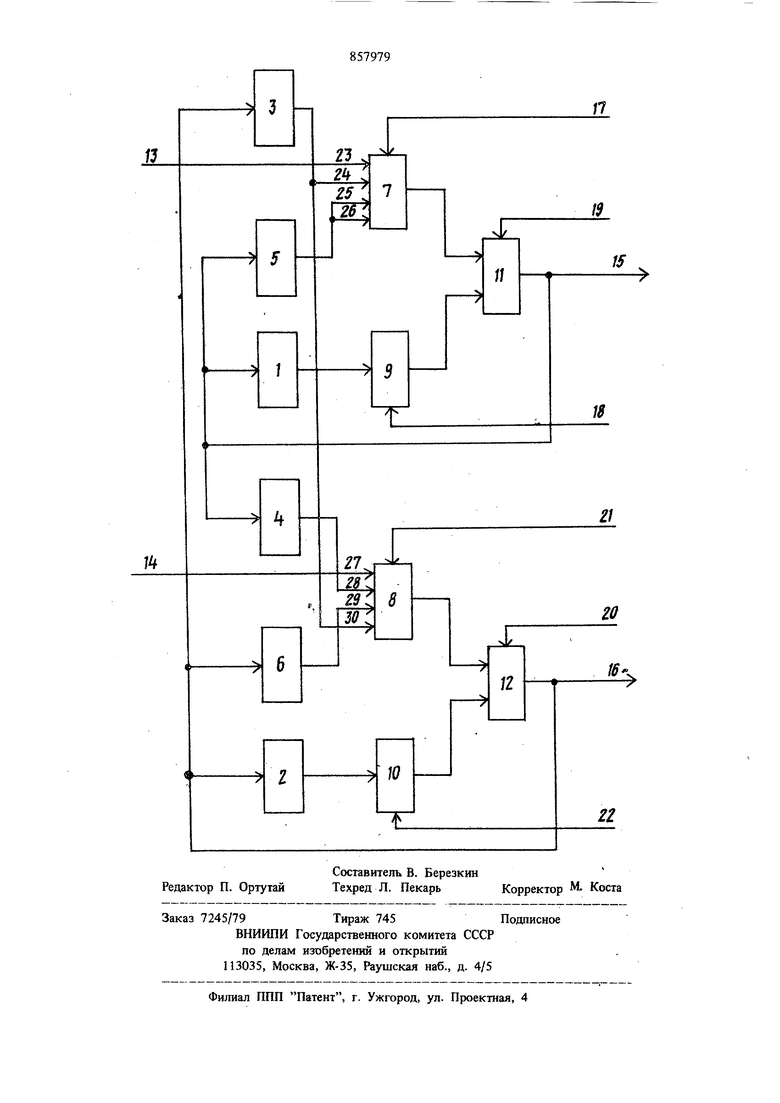

На чертеже представлена структурная схема вычислительного устройства для поворота вектора.

Устройство, содержит регистры 1-6 для хранения начальной и промежуточной числовой информации, мультиплексоры 7 и 8 (четыре информационных входа, один выход), сдвигатели

зацию этапа I.

Рассмотрим работу предлагаемого устройства в процессе вьшолиения этапа 11 и коррекции, которые представляют собой итерациойные процессьь Начало итеращш есть момент подачи управляющих сигналов на регистры, мультиплексоры, сдвигатели, сумматоры-вьпштатели. Управляющие сигналы обеспечивают подключение соответствующих входов мультиплексоров 7 и 8, сдвиг на требуемое число разрядов сдвигателями 9 и 10, выполнение требуемой операции сумматорами-вычитателями 11 и 12. Концом итерации является установление на выходах сумматоров-вьиитателей II и

12 результата конкретаой операции.

Начальными данными этапа Т Г являются (j, Уд- И набор f , соответствующих углу 0Q. Перед выполнением этапа II по формулам (3),(4) на данном устройстве необходимо

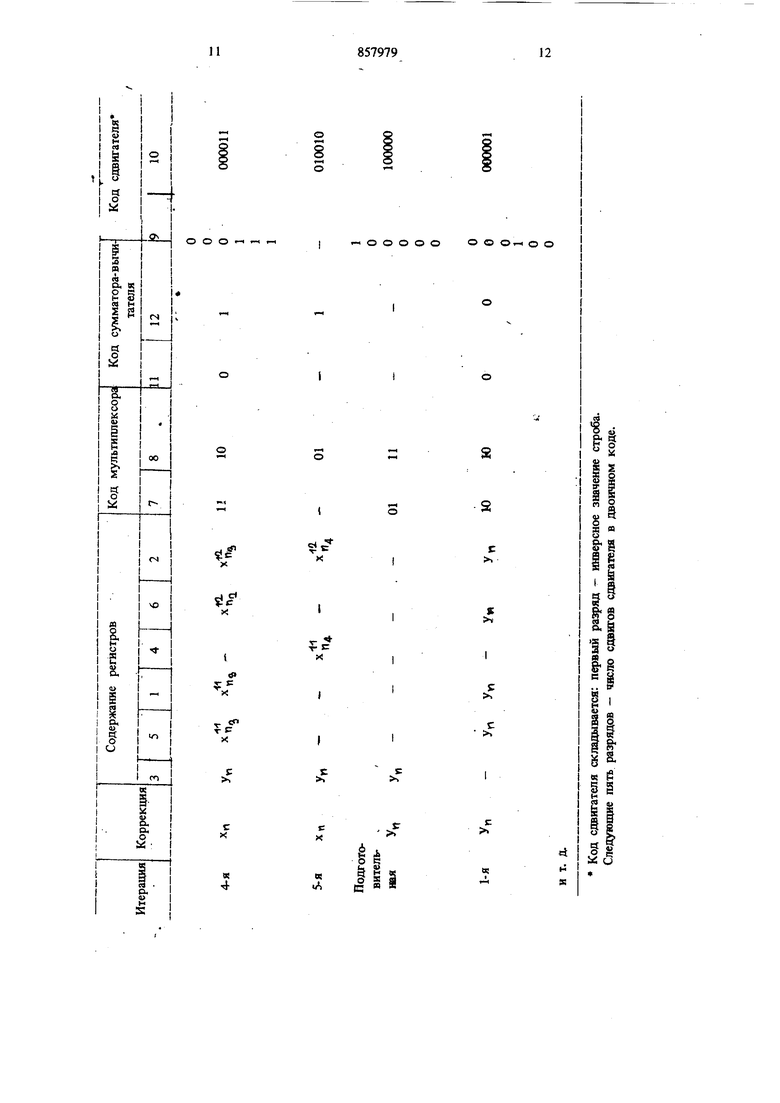

осуществить подготовительную итерацию. Она заключается в том, чтобы начальные условия подать на вход определенных регистров. Пусть на входе 13 присутствует XQ, на входе 14 - уд. 4 и 10 на () разрядов, ,..., со стробиованием, сумматоры-вычитатели 11 и 12. инормационные входы 13 и 14 устройства, инормационные выходы 15 и 16 устройства, перый и второй управляющие входы 17 и 18 стройства, третий и четвертый управляю1дие ходы 19 и 20 устройства, пятый и щестой упавляющие входы 21 и 22 устройства, входы 23-30 мультиплексоров 7 и 8. Поворот вектора осуществляется по следующим зависимостям. t Q.vr.-f.oirrtcra, Этап 1 n-f 1 -( (Л0,. . i.,-vfri:. V V f . 1 где 1 0,1,..., п-1; 90- угол поворота; XQ, Уд- начальные координаты вектора. Полученные в результате этой процедуры значения х. у в К раз больше истинных координат вектора после поворота. Поэтому необходима коррекция полученных результатов, то есть надо найти Y, , где К коэффивдеит деформации вектора. Этап Г в данном устрюйстве без потери общности не выполняется ввиду того, что устройство используется в режиме, когда углы хранятся в памяти в требуемом виде, т. е. в виде набора , ранее вычисленных. Использование данного устройства в другом режиме легко осуществить, дополнив необходимыми известными схемами, обеспечивающими реалиВ результате подготовительной итерации необходимо обеспечить на выходе сумматора-вычитателя 11 зиачение х, что достигается подключением входа 23 мультиплексора 7, обеспечением на выходе сдвигателя 9 нуля за счет снятия стробирующего сигнала, установкой ко|Да суммирования на сумматоре-вычитателе И. Аналогичным образом на вьтходе сумматоравычитателя 12 получаем у. Первая итерация этапа 1Г начинается с записи в регистры 1 и 4 значения в регистры 2 и 3 записывается у. В вычислении формулы (3) принимают участие регистры 1 и 3, мультиплексор 7, сдвигатель 9, сумматорвьиитатель 11. На выходе сумматора-вычитателя 11 имеем у. Одновременно вычисляется формула (4) с участием регистров 2 и 4, мультиплексора 8, сдвигателя 10, сумматора-вычитателя 12. На выходе сумматора-вычитателя 12 имеем х. Вторая итерация начинается с записи х в регистры 2 и 3 и записи у в регистры 1 и 4 На выходе сумматора-вычитателя 11 имеем к, на выходе сумматора-вычитателя 12 - у-. И так далее. Таким образом, если на вход 13 подан XQ, а на вход 14 - у.,, то на нечетной итеридии с сумматора-вычитателя 11 получаем значение v-, с сумматора-вычитателя 12 - х. На четной итерации наоборот: с сумматора-вычи тателя 11 - х., с сумматора-вычитателя 12 - Коррекция полученных результатов х, Уп будет осуществляться последовательно. Сначала корректируется х, затему. Перед вьшолнением коррекции х и у необходимо провести подготовительные итерации. Подготовительная итерация для коррекции х состоит в следующем. Значение х с выхода сумматора-вычитателя 11 записывается в регистры 5, 1 и 4, а значение у с сумматоравычитателя 12 записывается в регистр 3, где хранится до окончания коррекдаи х,. С выхода сумматора-вычитателя 12 имеем х„. Значение полученное с сумматора-вычитателя 11 на этой итерации, безразлично: оно не будет записываться в регистры. Первая итерация коррекции х у начинается с записи Xj, в регистры 2 и 6. В регистрах 1 и 5 х уже записано. Коррекция заключается в умножении х на константу- -. Двоичное представление этой константы, полученной для 31-й. итерации, имеет вид: - 0,1001101101110100111011011010100 Алгоритмы умножения на константу} можно представить в виде следующей итерационной процедуры где XY,.J- промежуточное значение, получаемое в результате i-ой итерации коррекции Ш1 J-OM cj MHTope-вычитателе , 2, 3, 4; j 11, 12); х„- корректируемая величина; х„ - результат коррекции. э Подготовительная итерация для коррекции Уf заключается в том, чтобы обеспечить на входе регистров 5,1,6,2 значение у, которое хранилось в регистре 3. Коррекц)1я у осуществляется с помощью той же итерацио1шой процедуры, которая иоюльзуется при коррекции х. В таблице представлено начальное состояние всех компонентов вычислительного устройства для поворота вектора для всех итераций коррекции, в том числе подготовительных. Символом - показано безразличное состояние компонента. Код сумматора-вычитателя О означает сложение, 1 - вычитание, Введение двух новых регистров и ряда дополнительных связей в устройство позволило получить уменьшение времени на коррекцию результата поворота вектора по методу Волдера. Так, в известном устройстве для осуществления коррекции результата, являющегося двумя 32разрядными двоичными числами, требуется 32 гтерации (сдвиг, суммирование-вычитание, запись в регистры), не считая подготовительных. При использовании предлагаемого изобретения достаточно выполнить пять итераций на одно 32-разрядное число, также не считая одной подготовительной. Время, затрачиваемое на выполнение зтих пяти итеращи на современной элементной базе, не превыщает 1 мкс. Последовательное, а не параллельное выполнение коррекции двух чисел результата позволяет совместить счет и вьщачу результата в 32-разрядном формате из специализированного процессора в ЦВМ, что также сокраиадет общее время получения результата (ЦВМ -спецпроцессор ЦВМ

Кроме того, данное устройство без изменения микропрограммы коррекции может выполнять коррекцию двух 16-разрядных двоичных чнселлараллельно, что занимает четыре вычислительных итерации, формулы (5), (7), (9), (11). Так как результат и в этом случае формируется в виде 32-разрядного слова (два 16разрядных слова), его также удобно выдавать в ЦВМ.

Эффективность данного устройства по сравнению с известным характеризуется относительным увеличением быстродействия. Увеличение быстродействия Д1Тй 32-разрядных чисел 34%.

Увеличение быстродействия для 16-разрядных чисел « 37,5%.

Такое увеличение быстродействия оправдывает введение двух дополнительных регистров,

которое практически не сказывается на увеличении оборудования.

Данное устройство может работать и с другими форматами данных, -например с 24-разрядными. В этом случае можно либо применять

приведенную в описании микропрограмму для коррекции 32-разрядных слов, так как константы коррекции совпадают в 24-разрядах, либо разработать новую микропрограмму, чем можно добиться уменьшения числа итераций

на коррецию.

13 Формула изобретения

Вычислительное устройство для поворота вектора, содержащее четыре регистра, два мультивибратора, два сумматора-вычитателя, выходы которых соединены с входами соответственно первого и второго регистров, выходы которых соединены с информационными входами первого и второго сдвигателей соответственно, первые информационные входы первого и второго мультиплексоров являются информационными входал1и устройства, вторые информационные входы первого и второго мультиплексоров соединены с выходами соответственно третьего и четвертого регистров, управляющий вход первого мультиплексора и управляющий вход первого сдвигателя являются соответственно первым и вторым управляющими входами устройства, а управляющие входы первого и второго сумматоров-вычитателей соответственнотретьим и четвертым управяяющидш входами устройства, отличающееся тем, что, с целью увеличения быстродействия, в него введены пятый и щестой регистры, при этом вход пятого регистра соединен с входами первого и четвертого регистров, а выход пятого регистра соединен с третьим и четвертым информационными входами первого мультиплексора, вход

14

857979шестого, регистра соединен с входами второго и третьего регистров, а выход шестого регистра соединен с третьим информационным входом второго мультиплексора, четвертый информационный вход которого соединен с выходом третьего регистра, выходы первого и второго мультиплексоров соединены с первыми информационными входами соответственно первого и второго сумматоров-вычитателей, вторые информационные входы (соторых соединены с выходами

0 соответственно первого и второго сдвигателей, выходы сумматоров-вычитателей являются информационными вьйсодами устройства, управляющие входы второго мультиплексора и второго сдвигателя являются соответственно пя5тым н щестым управляннцими входами устройства.

Источники информации, принятые во внимание при экспертизе

0

Авторы

Даты

1981-08-23—Публикация

1979-10-10—Подача