30

блок 8 памяти констант, сдвигатели 9 25 ляется количеством значащих циЛр раз- и 10, регистры 11 и 12, сумматоры-вы- читатели 13 - 1Ь, блок 16 управления, управляющие выходы 17-20 блока управления.

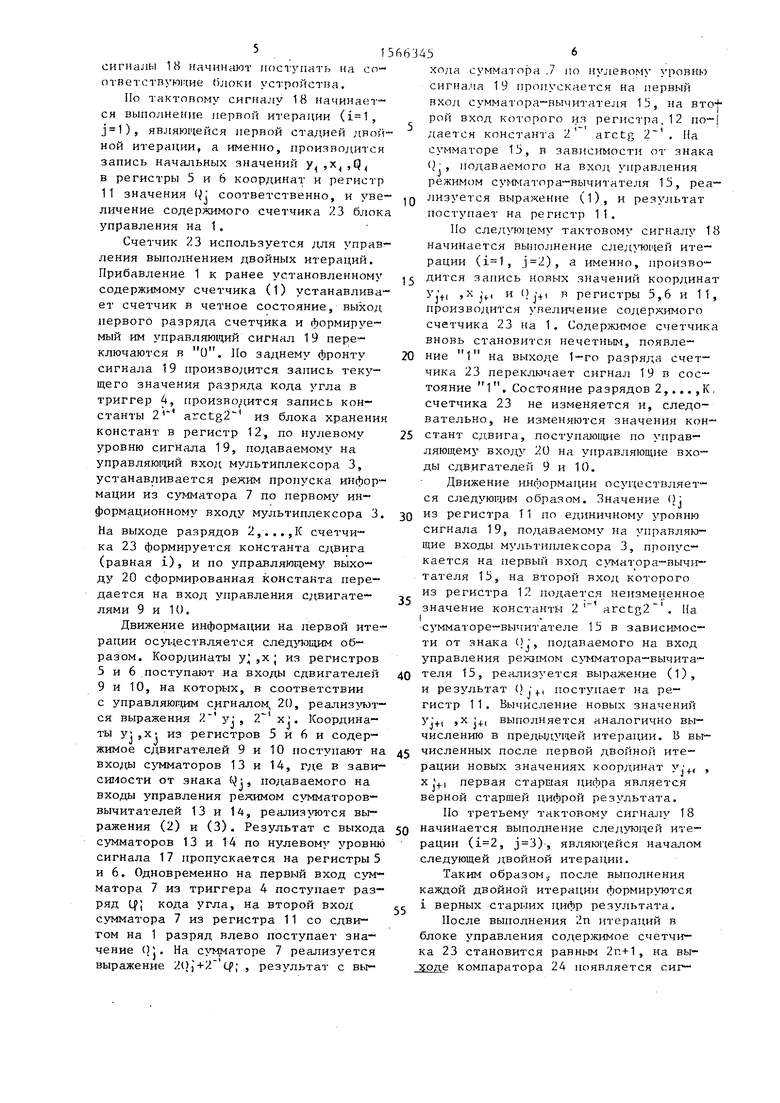

Блок управления (йиг. 2) содержит генератор 21 сигналов, элемент И 22, счетчик 23 итераций на log(2n+1)+1 разрядов, схему 24 сравнения, триггер 2з, элемент HJDI-HE 26, элемент II задержки.

Работа устройства основана на реализации следующих рекурентных соотношений :

35

рядов кода vrjia if . При разрядности операнда п преобразователь выполняет

2п итераций. I

Преобразователь работает следующим образом.

На информационные входы устройства у,х, подаются исходные значения координат y,Y/K,, (. На информационный вход Ц, подается значение первого старпего разряда кода угла ер поворот а.

По сигналу Пуск в блоке 16 управления производится начальная установка, а именно, сигнал Пуск устанавливает триггер 25 в состояние 1. Сигнал с инверсного выхода триггера 25, проходя через элемент ИЩ- НЕ 26 и элемент 27 задержки, формирует на выходе элемента ИЛИ-НЕ 26 одиночный сигнал 1/.

}Я1 2СЬ+ 2-Ч-Гн

X J+, Xj+ Fj2-1 Yj sign signQj

О, для ,4,.., 1, для j 1,3,. . ,

arctg(2

) (1 (2 (3)

,, , 2n ,2n-1, :,X/K,, y,,

145 ()

Начальные значения х Y/K,, q,0

fif,,,..., где К, - коэффициент деЛормации (,355909).

Для учета веса вводимого 1-го разряда (cf( ) кода угла поворота при сло50

По сигналу Пуск в блоке 16 управления производится начальная установка, а именно, сигнал Пуск ус танавливает триггер 25 в состояние 1. Сигнал с инверсного выхода три гера 25, проходя через элемент ИЩ- 26 и элемент 27 задержки, формирует на выходе элемента ИЛИ-НЕ 26 одиноч ный сигнал 1/.

Но единичному уровню сигнала 1/ производится установка счетчика 23 итераций в состояние 1, производи ся обнуление буферного регистра 11, пропуск начальных значений у,,xf че рез мультиплексоры 1 и 2 в регистры 5 и 6. Появление 1 на выходе первого разряда счетчика 23 являетс источником управляющего сигнала 19.

жении в сумматоре в предлагаемом пре- Затем сигнал 17 переключается в О1

Сигнал с прямого выхода триггера 25 разрешает прохождение сигналов из г нератора 21 сигналов через элемент И 22. С выхода элемента И 22 тактов

образователе осуществляется сдвиг значения О на 1 разряд влево и ис- пользуют9я заранее вычисленные константы 2 arctg (21 ). Константы в

30

25 ляется количеством значащих циЛр раз-

35

)

145 )

50

рядов кода vrjia if . При разрядности операнда п преобразователь выполняет

2п итераций. I

Преобразователь работает следующим образом.

На информационные входы устройства у,х, подаются исходные значения координат y,Y/K,, (. На информационный вход Ц, подается значение первого старпего разряда кода угла ер поворот а.

По сигналу Пуск в блоке 16 управления производится начальная установка, а именно, сигнал Пуск устанавливает триггер 25 в состояние 1. Сигнал с инверсного выхода триггера 25, проходя через элемент ИЩ- НЕ 26 и элемент 27 задержки, формирует на выходе элемента ИЛИ-НЕ 26 одиночный сигнал 1/.

Но единичному уровню сигнала 1/ производится установка счетчика 23 итераций в состояние 1, производится обнуление буферного регистра 11, пропуск начальных значений у,,xf через мультиплексоры 1 и 2 в регистры 5 и 6. Появление 1 на выходе первого разряда счетчика 23 является источником управляющего сигнала 19.

Затем сигнал 17 переключается в О1

Сигнал с прямого выхода триггера 25 разрешает прохождение сигналов из генератора 21 сигналов через элемент И 22. С выхода элемента И 22 тактовые

515

сигналы 18 начинают поступать на со- от нет сп пуюцне Олоки устройства.

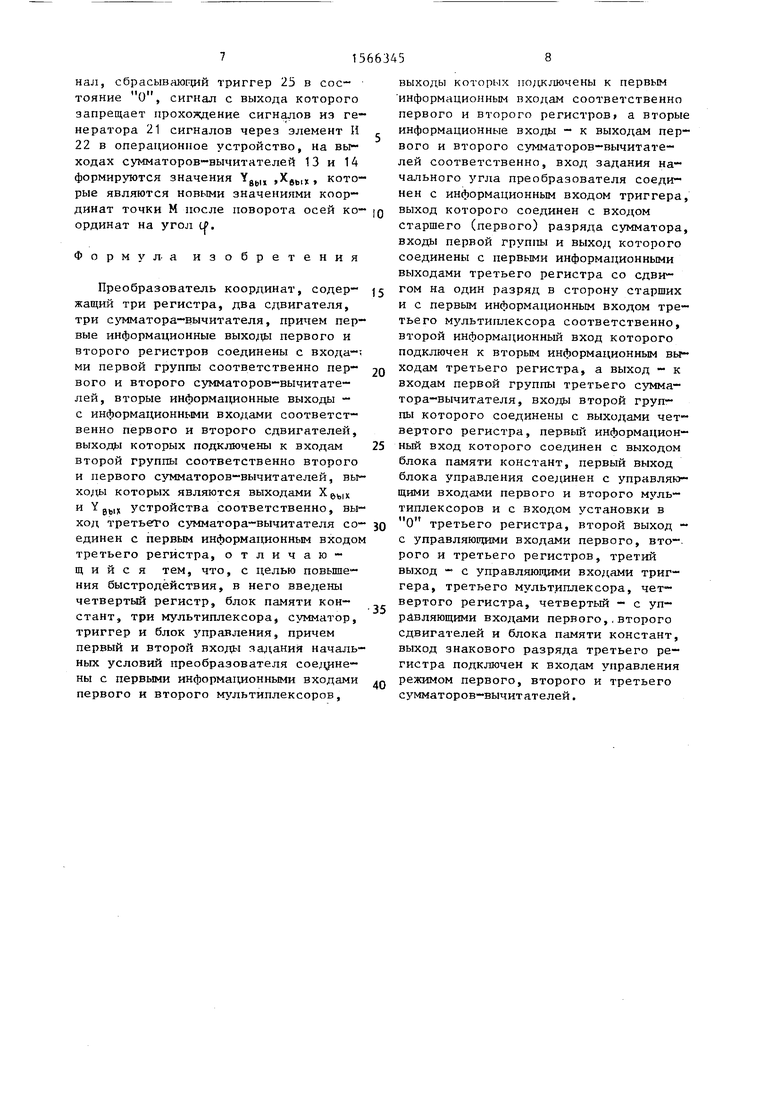

Но тактопому сигналу 18 начинается выполнение нерпой итерации (, ), являющейся нерпой стадией днои- ной итерации, я именно, производится запись начальных -значении y,,Q{ в регистры 5 и Ь координат и регистр 11 значения (} . соответственно, и уве- личение содержимого счетчика 23 блока управления на 1.

Счетчик 23 используется для управления выполнением двойных итерации. Прибавление 1 к ранее установленному содержимому счетчика (1) устанавливает счетчик в четное состояние, выход первого разряда счетчика и Нормируемый им управляющий сигнал 19 переключают ся в О. По заднему Аронту сигнала 19 производится запись текущего значения разряда кода угла в триггер 4, производится запись константы arctg2 из блока хранения констант в регистр 12, по нулевому уровню сигнала 19, подаваемому на управляющий вход мультиплексора 3, устанавливается режим пропуска инАор- мации из сумматора 7 по первому информационному входу мультиплексора 3. На выходе разрядов 2,...,К счетчика 23 формируется константа сдвига (равная i), и по управляющему выходу 20 сформированная константа передается на вход управления сдвигате- лями 9 и 10.

Движение информации на первой итерации осуществляется следующим образом. Координаты у ,х; из регистров 5 и 6 поступают на входы сдвигателей 9 и 10, на которых, в соответствии с управляющим сигналом, 20, реализуются выражения у;, х:. Координаты из регистров 5 и 6 и содержимое сдвигателей 9 и 10 поступают на входы сумматоров 13 и 14, где в зависимости от знака (:, подаваемого на входы управления режимом сумматоров- вычитателей 13 и 14, реализуются выражения (2) и (3). Результат с выхода сумматоров 13 и 14 по нулевому уровню сигнала 17 пропускается на регистры 5 и 6. Одновременно на первый вход сумматора 7 из триггера 4 поступает разряд LfJ кода угла, на второй вход сумматора 7 из регистра 11 со сдвигом на 1 разряд влево поступает значение ():. На сумматоре 7 реализуется выражение l)j+/T cp; , результат с выО

хода (.умм.пора 7 по нулевому уровню сигнала 14 пропускается на первый вход сумматора-вычитателя 1Ь, на втох рой вход которого из регистра,12 по-| дается константа 2 arrtg 2 . Па сумматоре 13, в зависимости от знака Q , подаваемого на вход управления режимом сумматора-вычитителя 1Ь, реализуется выражение (1), и результат поступает на регистр 11.

По следующему тактовому сигналу 18 начинается выполнение след тощей итерации (, 1), а именно, производится запись новпх значений координат У. +1 xjv и Ч j+i H регистры 5,6 и 11, производится увеличение содержимого счетчика 23 на 1. Содержимое счетчика вновь становится нечетным, появление 1 на выходе 1-го разряда счетчика 23 переключает сигнал 14 в состояние 1. Состояние разрядов 2,. .. , К счетчика 23 не изменяется и, следовательно, не изменяются значения констант сдвига, поступающие по управляющему входу 20 на управляющие входы сдвигателей 9 и К).

Движение инпормацпн осуществляется следующим образом. Значение. )j из регистра 11 по единичному уровню сигнала 19, подаваемому на управляющие входы мультиплексора 3, пропускается на первый вход суматора-нычн- тателя 1Ь, на второй вход которого из регистра 12 подается неизмененное значение константы 2 arctg2 . Па сумматоре-вычитателе 13 в зависимости от знака О., подаваемого на вход управления рехнмом сумматора-вычнта- теля 15, реализуется выражение (1),

и результат ()

J+

поступает на регистр 11. Вычисление новых значений yf( ,х- + | выполняется аналогично вычислению в предыдущей итерации. В вычисленных после первой двойной итерации новых значениях координат у 44 х, первая старшая цигЬра является верной старшей цисЪрой результат а.

По третьему тактовому сигнал} 18 начинается выполнение следующей итерации (, ), являющейся началом следующей двойной итерации.

Таким образом... после выполнения каждой двойной итерации Лорнируются i верных старпих циЛр результата.

После выполнения 2п итераций в блоке управления содержимое счетчика 23 становится равным 2г+1, на вы- ходе компаратора 24 появляется CHI-

нал, сбрасывающий триггер 25 в состояние О, сигнал с выхода которого запрещает прохождение сигналов из генератора 21 сигналов через элемент И 22 в операционное устройство, на выходах сумматоров-вычитателей 13 и 14 формируются значения Yg()l, ,ХвЬ1«, которые являются новыми значениями координат точки М после поворота осей ко- ординат на угол if.

Формула изобретения

Преобразователь координат, содер- жащий три регистра, два сдвигателя, три сумматора-вычитателя, причем первые информационные выходы первого и второго регистров соединены с входа-; ми первой группы соответственно пер- вого и второго сумматоров-вычитате- лей, вторые информационные выходы - с информационными входами соответственно первого и второго сдвигателей, выходы которых подключены к входам второй группы соответственно второго и первого сумматоров-вычитателей, выходы которых являются выходами Хеы)1 и устройства соответственно, выход третьего сумматора-вычитателя со- единен с первым информационным входом третьего регистра, отличающийся тем, что, с целью повышения быстродействия, в него введены четвертый регистр, блок памяти кон- стант, три мультиплексора, сумматор, триггер и блок управления, причем первый и второй входы задания начальных условий преобразователя соединены с первыми информационными входами первого и второго мультиплексоров,

выходы которых подключены к первым информационным входам соответственно первого и второго регистров а вторые информационные входы - к выходам первого и второго сумматоров-вычитате- лей соответственно, вход задания начального угла преобразователя соединен с информационным входом триггера, выход которого соединен с входом старшего (первого) разряда сумматора, входы первой группы и выход которого соединены с первыми информационными выходами третьего регистра со сдвигом на один разряд в сторону старших и с первым информационным входом третьего мультиплексора соответственно, второй информационный вход которого подключен к вторым информационным выходам третьего регистра, а выход - к входам первой группы третьего сумматора-вычитателя, входы второй группы которого соединены с выходами четвертого регистра, первый информационный вход которого соединен с выходом блока памяти констант, первый выход блока управления соединен с управляющими входами первого и второго мультиплексоров и с входом установки в О третьего регистра, второй выход - с управляющими входами первого, второго и третьего регистров, третий выход - с управляющими входами триггера, третьего мультиплексора, четвертого регистра, четвертый - с управляющими входами первого,,второго сдвигателей и блока памяти констант, выход знакового разряда третьего регистра подключен к входам управления режимом первого, второго и третьего сумматоров-вычитателей.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

| Вычислительное устройство для поворота вектора | 1987 |

|

SU1520511A1 |

| Устройство для вычисления функций | 1986 |

|

SU1374219A1 |

| МАТРИЧНЫЙ СПЕЦПРОЦЕССОР | 1994 |

|

RU2079879C1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1370653A1 |

| Вычислительное устройство для поворота вектора | 1979 |

|

SU857979A1 |

| Устройство для преобразования координат | 1985 |

|

SU1254475A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1690195A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных системах, работающих в реальном масштабе времени, для выполнения преобразования координат при повороте осей на заданный угол, при последовательном вводе кода угла. Цель изобретения - повышение быстродействия. Работа преобразователя базируется на использовании способа вращения векторов по методу Волдера. Отличительной особенностью преобразователя является возможность получать разряды новых координат на его выходе по мере поступления кода угла поворота старшими разрядами вперед на его входы. Выигрыш в быстродействии составляет N(N - разрядность кода угла) раз по сравнению с устройствами, использующими сформированный полноразрядный код аргумента. Преобразователь содержит мультиплексоры 1-3, триггер 4, регистры 5, 6 координат, сумматор 7, блок 8 памяти констант, сдвигатели 9, 10, регистры 11, 12, сумматоры-вычитатели 13-15, блок 16 управления. 3 ил.

I-г

i-г

| Цифровой преобразователь координат | 1981 |

|

SU1076903A1 |

| С, Ob F 7/548, 1984 | |||

| Voider I.E | |||

| The Cordic trigonometric Computing technique - IRK Frans of Electronic Computers, vol EC-8, If 3, September, 1959, pp | |||

| Катодная трубка Брауна | 1922 |

|

SU330A1 |

Авторы

Даты

1990-05-23—Публикация

1988-07-11—Подача