устройства,выход первого сумматоравычитателя f-ro ( 5, 6, 7, 8) . итерационного- блока соединен с (f - 4)-м выходом устройства, управляющие входы с первого по третий сумма.торов-вычитателей всех итерационных блоков соединены с соответствующими входами задания режима устройства, управляюпще входы третьего, первого и второго преобразователей прямого кода в дополнительный второго,-четвертого, шестого и восьмого итерационных блоков соединены с выходом знака первого сумматора-вычитатёля соответственно второго, третьего и четвертого итерационного блока, управляиощй вход третьего преобразователя прямого кода в дополнительный первого, третьего, пятого и седьмого итерационных блоков соединен с выходом знака первого сумматора-вычитатёля четвертого итерационного блока, управляющий вход первого преобразователя прямого кода в дополнительный первого и пятого итерационных; блоков соединены с выходом знака первого сумматора-вычитатёля третьего итерационного блока, управляющий вход второго преобразователя прямого кода в дополнительный первого и пятого итерационных блоков и управляющий вход первого преобразователя прямого кода в дополнительный третьего и седьмого итерационньЬс блоков соединены с выходом знака первого сум мауора-Бычитателя второго итерационкого блока, выход знака первого сумматора-вычитатёля третьего итерационного блока соединен с управляющим входом второго преобразователя прямого кода в дополнительньй третьего и седьмого итерационных блоков, выход знака первого сумматора-вьгчитателя четвёртого итерационного блока соединен с управляющим входом второго преобразователя прямого кода в дополнительный второго, четвертого, шестого и восьмого итерационных блоков, управляющий вход сдвигателя итерационных блоков с первого по четвертый соединен с первым входом сдвига устройства, первый вход записи которого соединен с входами записи сдвигателя и регистра итерационных блоков с первого по четвертьй, входы записи регистра, сдвигателя и управляющий вход сдвигателя итерационных блоков с пятого по восьмой соединены соответственно с вторым входом записи и вторым входом сдвига устройства, причем в каждом итерационном блоке вторые входы элементов ИЛИ группы соединены с выходом знака первого сумматора-вычитатёля, выходы элементов ИЛИ группы соединены с информационным входом регистра, выход которого соединен с вторым информационным входом первого сумматора-вычитатёля, выход знака первого сумматора-вычитатёля соединен .с информационным входом третьего преобразователя прямого кода в дополнительныйj выход которого соединен с первым информационным входом второго сумматораг-вычитателя, второй информационный вход и выход которого соединены соответственно с вькодом первого преобразователя прямого кода в дополнительный и первым информационным входом третьего сумматора-вычитатёля, второй информационный вход и выход которого соединены соответственно с вькодом второго преобразователя прямого -код k в дополнительный и информационным входом сдвигателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU780004A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1370653A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Цифровой функциональный преобразователь | 1979 |

|

SU922733A2 |

| Устройство для вычисления синусно- косинусных функций | 1978 |

|

SU750495A1 |

| Цифровое устройство для вычисления синусно-косинусных функций | 1980 |

|

SU868753A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАПРАВЛЯИЦИХ КОСИНУСОВ ВЕКТОРА В ПРОСТРАНСТВЕ, содержащее восемь итерационных блоков, причем каждый итерационный блок содержит три сумнатора-вычитателя, отличающее- с я тем, что, с целью расширения области применения за счет возможности дополнительного вычисления направляющих косинусов вектора в четьфехмерном пространстве, в каждый итерационный блок введены группа элементов ИЛИ, регистр, три преобразователя прямого кода в дополнительный и сдвигатель, первый информационный вход первого сумматора-вычитателя i-ro и (i + 4)-го (i 1, 2, 3)итерационных блоков соединены с выходами сдвигателя соответственно (i + 1)-го и (i + 5)-го итерационных блоков, информационный вход первого преобразователя прямого кода в дополнительный j-ro и. (j 1+ )-го (J 1, 2) итерационных блоков соединены с выходом первого сумматор а-вычитателя соответственно (j + 1)-го и (j + 5)-го итерационных блоков, выход сдвигателя первого и пятого итерационных блоков соединены с первыми информационными входами первых сумматоров-вычитателей соответственно четвертого и восьмого итерационных блоков, выход знака первого сумматора-вычитателя ко- торых соединен с информационным входом .второго преобразовйтеля прямогокода в дополнительный соответственно второго и шестого итерационных блоков, выход знака первого сумматора-вычитателя первого и пятого ятерационньЕх блоков соединен с информационным входом первого преобразователя прямого кода в дополнительный (Л соответственно третьего, четвертого, седьмого и восьмого итерационш)К блоков, выход знака первого сумматор а-вьиитате ля второго и шестого итерационных блоков соединен с ин,формационным входом второго преобразователя прямого кода в.дополнительный соответственно четвертого и восьО) мого итерационных блоков, выход ка первого сумматора-вычитателя ко торых соединен с информационным входом второго преобразователя прямого кода в дополнительный соответственно третьего и седьмого итерационных блоков, выход знака первого суммато ра-вычитателя которых соединен с информационнь1м входом второго преобразователя прямого кода в дополнительный соответственно первого и пятого итерационных блоков, первые входы элементов ИЛИ группы К-го (К 1, 2, 3, 4, 5) итерационного блока соединены с К-м информационным входом

I

Изобретение относится к цифровой вычислительной технике и может быть использовано в быстродействующих процессорах и специализированных вычислительных устройствах,

Известноустройство для вычисления тригонометрических функций, со

держащее сумматоры-вычитатели, регистры, сдвигатели, группы элементов И и ИЛИ и реализующее известный алгоритм Волдера l j ,

Недостатком известного устройства является невозможность его непол 53ования для вычисления функции в четьфехмерном пространстве. . Наиболее близким к предлагаемому является устройство для реализации алгоритма Волдера, содержащее h последовательно соединенных итерационных блоков,, каждый из. которых содержит три сумматора-вычитателя и коммутатор , Недостатком известного устройства являются ограниченные возможности, так как устройство не позволяет вычислять направляющие косинусы век тора в четьфехмерном пространстве. Цель изобретения - распшрение об- 5 ласти применения за счет возможности дополнительного вычисления направляющих косинусов вектора в четырехмерном евклидовом пространстве. Поставленная цель достигается тем, что в устройство для вычисления направляю1цих косинусов векторов в пространстве, содержащее восемь итерационных блоков, причем каждьм итерационный блок содержит три сумматора-вычитателя, в каждый итерационный блок дополнительно введены группа элементов ИЛИ, регистр, три преобразователя прямого кода в дополнитель ный и сдвигатель, первый информацион ный вход первого сумматора-вычислителя i-ro и (i + 4)-го (i 1, 2, 3) итерационных блоков соединены с выхо дами сдвигателя соответственно (i + . + 1}то и (i. + 5)-го итерационных бло ков, информационный вход первого преобразователя прямого кода в допол нительный j-ro и (j 4)-го (J 1,2) итерационных блоков соединены с выходом первого сумматрра-вычитателя соответственно (j + 1)-го и (j + + 5)-го итерационных блоков, выход сдвигателя первого и пятого итерацио ных блоков соединены с первыми инфор мационными входами первых сумматоров вычитателей соответственно четверто-го и восьмого итерационных блоков, выход знака первого сумматора-вычйтателя которых соединен с информацио ными входом второго преобразователя прямого кода в дополнительный соответственно второго и шестого итерационных блоков, выход знака первогосумматора-вычитателя первого и пятого итера ционных блоков соединен с информационным входом первого преобразователя прямого кода в дополнительный соответственно третьего. 004 четЕГертого, седьмого и .восьмого итерационных блоков, выход знака первого сумматора-вычитателя второго и шестого итерационных блоков соединен с информационным входом второго преобразователя прямого кода в дополнительный соответственно четвертого и восьмого итерационных блоков выход знака первого сумматора-вычита- .теля которых соединен с информационным входом второго преобразователя прямого кода в дополнительный соответственно третьего и седьмого итерационных блоков, выход первого сумматора-вычитателя которых соединен с информационным входом второго преобразователя прямого кода- в дополг I нительный соответственно первого и пятого итерационных блоков, первые входы элементов ИЛИ группы К-го (к 1, 2, 3, 4, 5) итерационного блока соединены с К-м информационным входом устройства, выход первого сумматора-вычитателя f-ro ( 5-, 6, 7, 8) итерационного блока соединен с. (1 - 4)-м выходом устройства, управляющие входы с первого по третий сумматоров-вычитателей ,всех итерационных блоков соединены с соответствующими входами задания режима устройства, управлякнцие входы третьего, первого и второго преобразователей прямого кода в дополнительный второго, четвертого, шесто ° восьмого итерационных блоков соединены с выходом знака первого сумматора-вычитателя соответственно второго, третьего и четвертого итерационного блока, управляющий вход третьего преобразователя прямого кода в дополнительный первого, третьего, пятого и седьмого итерационных блоков соединен с выходом знака первого сумматора-вычитателя четвертого итерационного блока, управлякщий вход первого преобразователя прямого кода,в дополнительньй первого и пятого итерационных блоков соединены с выходом знака первого сумматора-вычитателя третьего итерационного блока, управляющий вход второго преобразрвателя прямого кода в дополнительный первого и пятого итерационных блоков и управляющий вход первого преобразователя прямого кода в дополнитель-; ный третьего и седьмого итерационных блоков соединень с выходом знака первого сумматора-вычитателя второго итерационного блока, выход знака первого сумматора-выч.итателя третьего итерационного блока соединен с управляющим входом второго йреобразователя лрямого кода в до- . полнительный .третьего и седьмого итерацион.ных блоков, выход знака первого сумматора-вычитателя четвер- того итерационного блока соединен с управлякицим входом второго преобразователя прямого кода в дополнительньй второго, четвертого, шестого и восьмого итерационных блоков, управлякщий вход сдвигателя итера- , ционных блоков.с первого по четвертый соединен с первь м входом сдвига устройства, первьй вход записи которого соединен с входами записи сдвигателя и регистра итерационных блоков с первого по четвертый, входы записи регистра, сдвигателя и управляющий вход сдвигателя итерационных блоков с пятого по восьмой соединены соответственно с вторым входом записи и вторым входом сдвига устрой ства, причем в каждом итерационном блоке вторые входы элементов ИЛИ группы соединены с выходом знака пер вого сумматора-вычитателя, выходы элементов ИЖ группы соединены с информационным входом регистра, выход которого соединен с вторым информационным входом первого сумматора-вычитателя, выход знака первого сумма.тора-вычитателя соединен с информационным входом третьего преобразователя прямого кода в дополнительный, выход которого соединен с первым информационным. входом второго сумматора-вычитателя, второй информационный вход и выход которого соединены соответственно с выходом.первого преобразователя прямого кода в дополнительный и первым информационным входом третьего сумматора-вычитателя, второ информационньй вход и выход которого соединены соответственно с выходом второго преобразователя прямого кода в дополнительный н информационным входом сдвигателя.

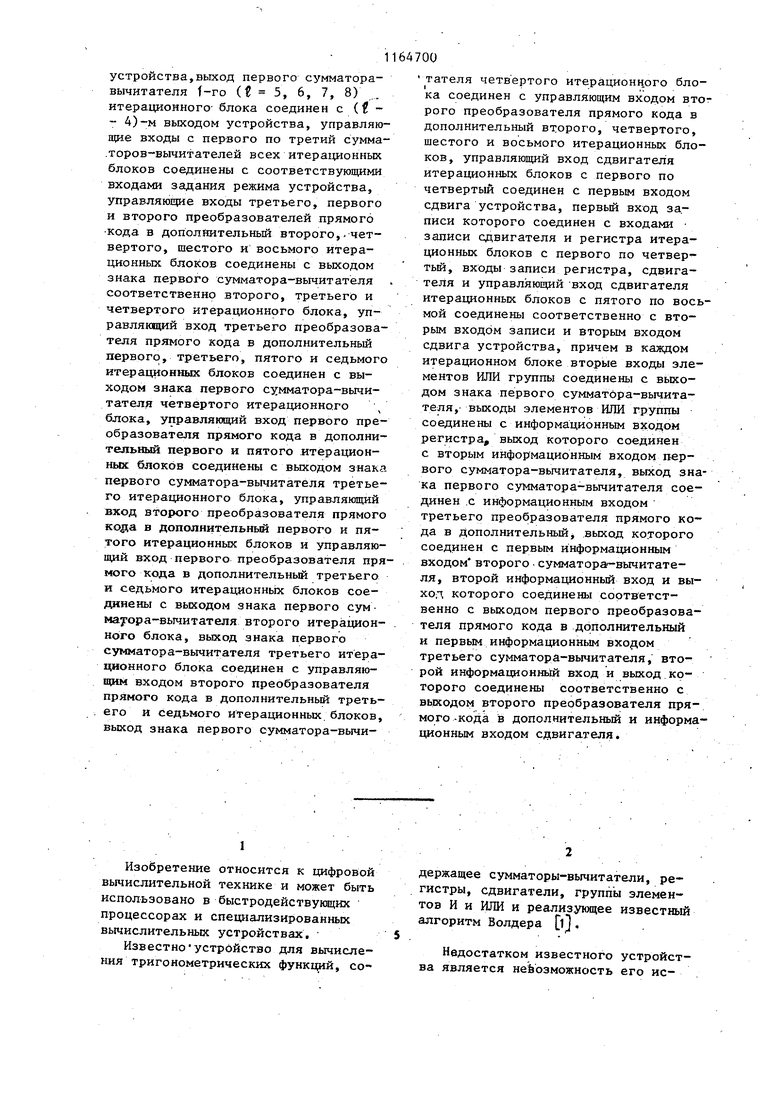

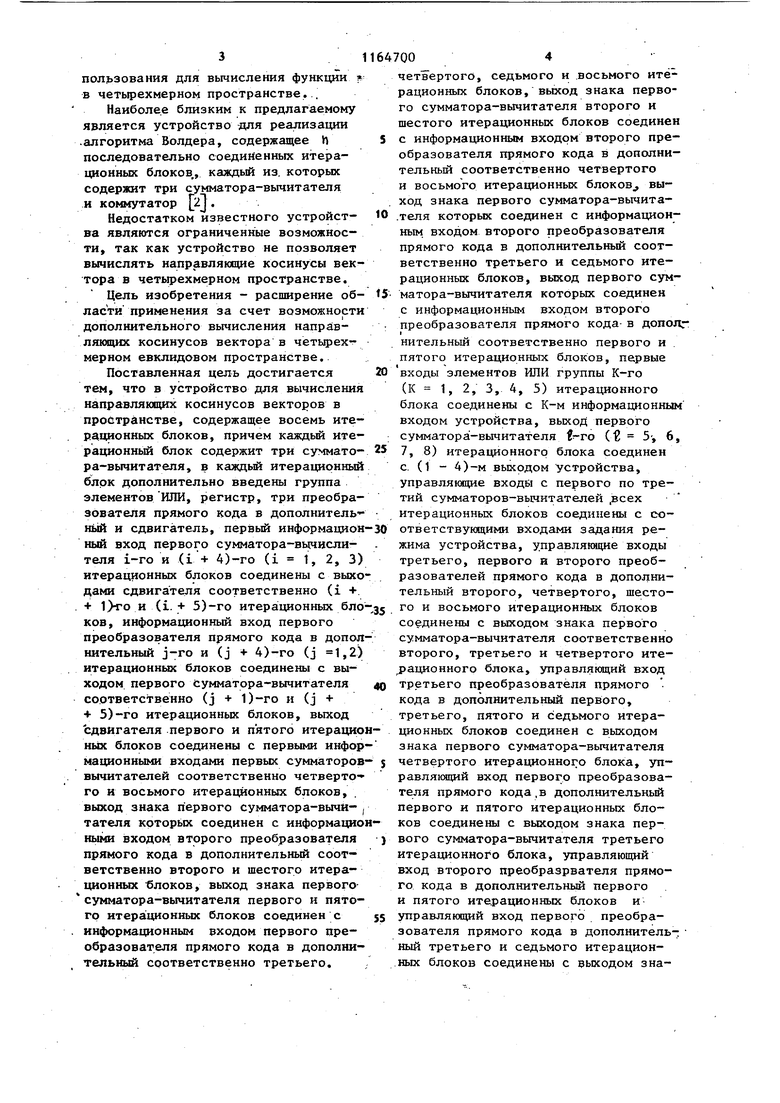

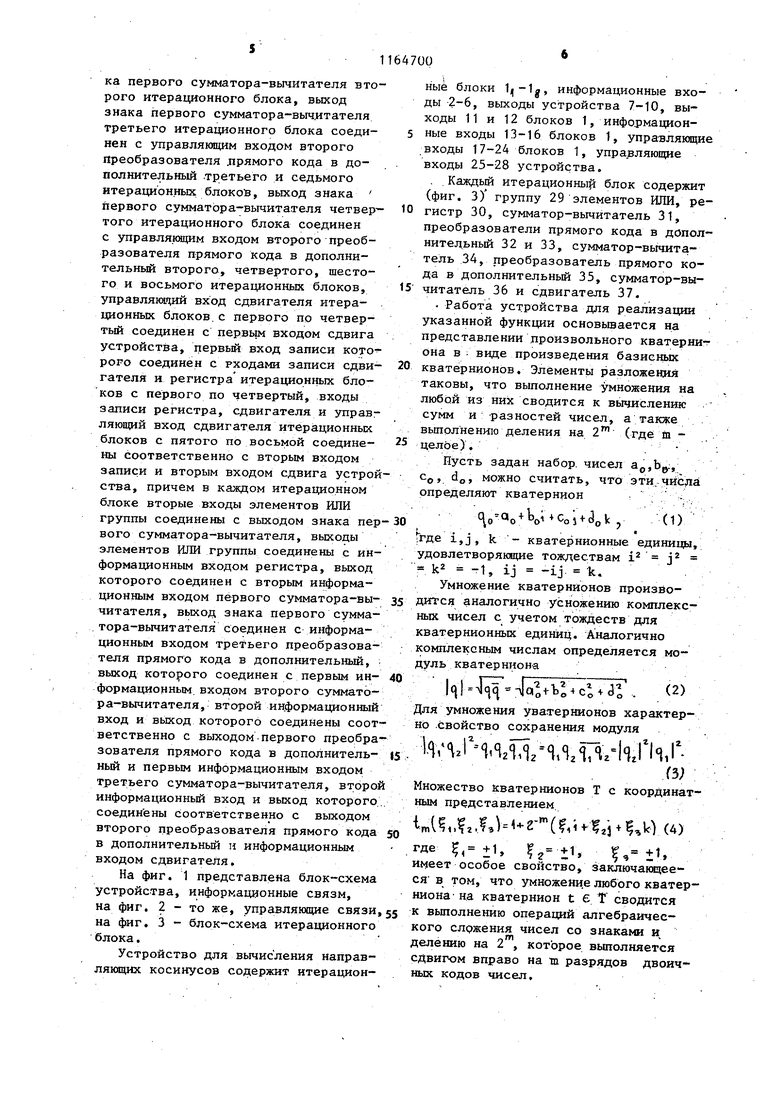

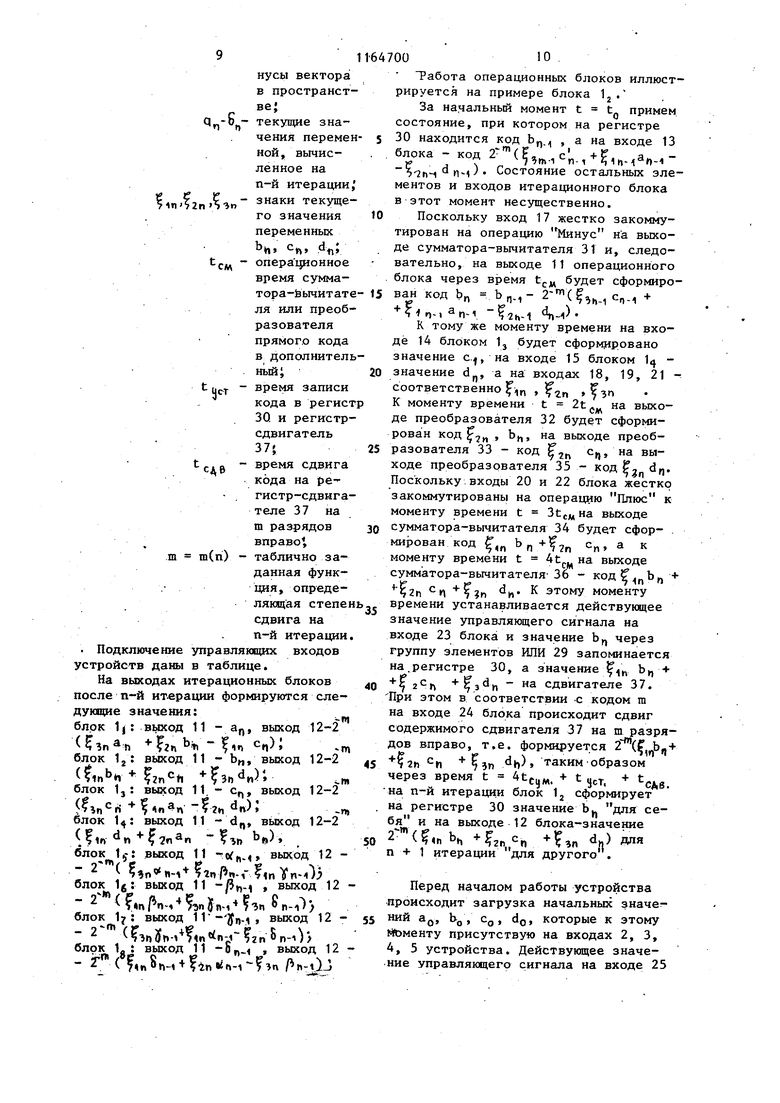

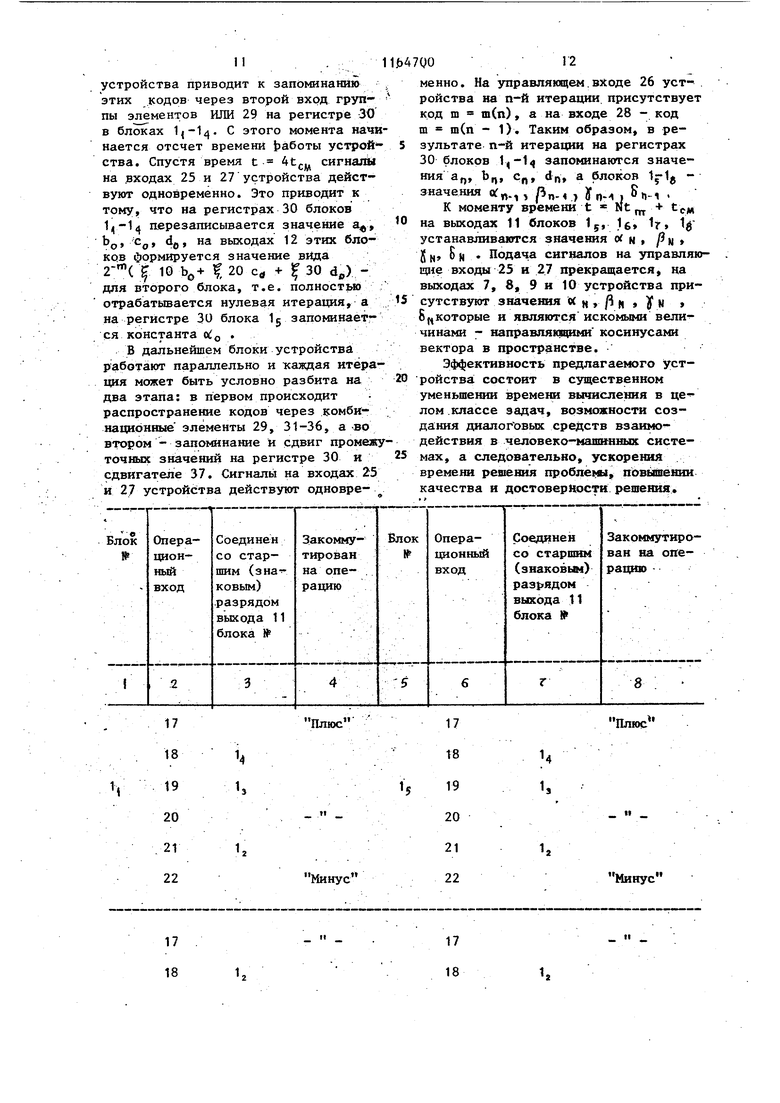

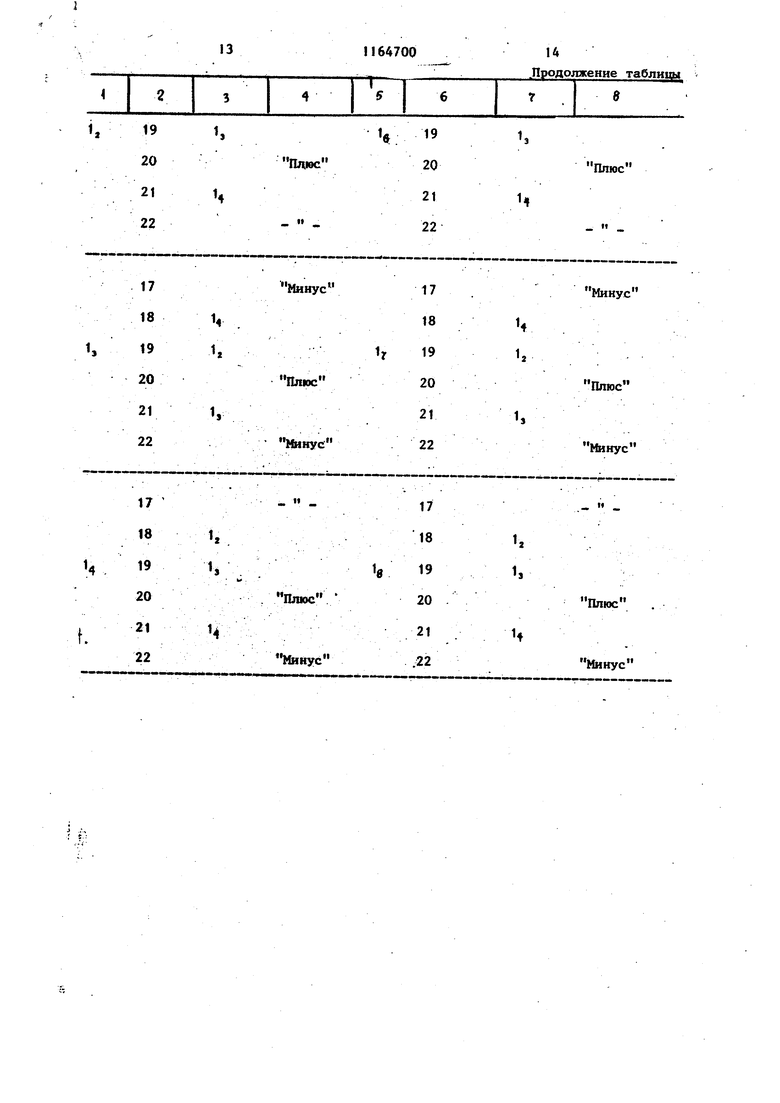

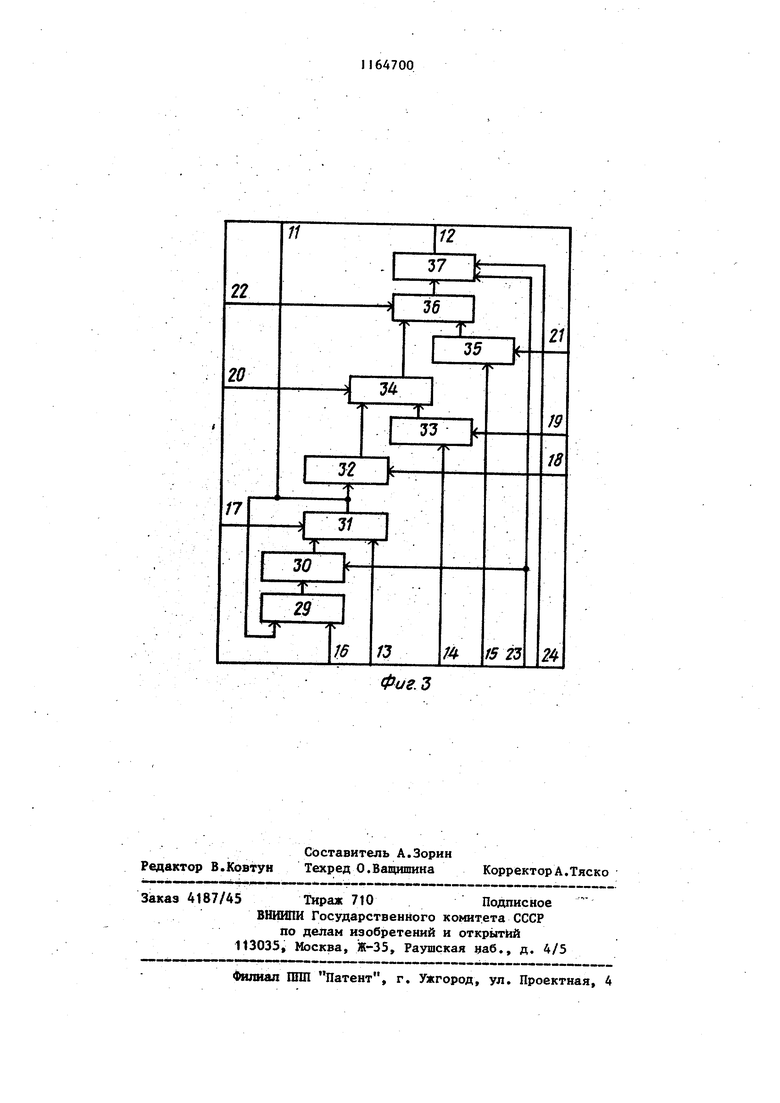

На фиг. 1 представлена блок-схема устройства, информационные связм, на фиг, 2 - то же, управляюсцие связи на фиг, 3 - блок-схема итерационного блока,

Устройство для вычисления направляющих косинусов содержит итерационные блоки 1|(-1jj информационные входы 2-6, вькоды устройства 7-10, выходы 11 и 12 блоков 1, информационные входы 13-16 блоков 1, управляющи входы 17-24 блоков 1, управляющие входы 25-28 устройства, . . Каждьгй итерационньщ блок содержит (фиг, 3) группу 29 элементов ИЛИ, регистр 30, сумматор-вычитатель 31, преобразователи прямого кода в дополнитедьньй 32 и 33, сумматор-вычитатель 34, преобразователь прямого кода в дополнительньй 35, сумматор-вычитатель 36 и сдвигатель 37,

Работа устройства для реализации указанной функции основьшается на представлении произвольного кватерни она в виде произведения базисных кватернионов. Элементы разложения таковы, что вьтолнение умножения на любой из них сводится к вычислению сумм и : -разностей чисел, а также выполнению деления на. 2 (где m целое),.

Пусть задан набор, чисел ад,Ъ, Cf,, do, можно считать, что зти:. числа определяют кватернион : :аг, + Ь„;+с„

o«o: + Coi+4k,

(1)

Ггде i,j , k - кватернионные единицы, удовлетворяющие тождествам i j k -1, ij -ij. -k.

Умножение кватернионов производится аналогично усножению комплексных чисел с учетом тождеств для кватернионных единиц. Аналогично комплексным числам определяется модуль кватерниона

|(). (2)

Для умножения уватернионов характерно .свойство сохранения модуля

Нл.1 1Н2Й/Н,ЙЛ 19гГИ,1гз;

Множество кватернионов Т с координатным представлением.

imUi.z..(,U1f,j + ,k) (4)

где , i1, г 11 Ь ib имеет особое свойство, заключанидееся в том, что умножение любого кватерниона- на кватернион t 6 Т сводится к выполнению операций алгебраического сложения чисел со знаками и

„пп делению на 2 , которое выполняется

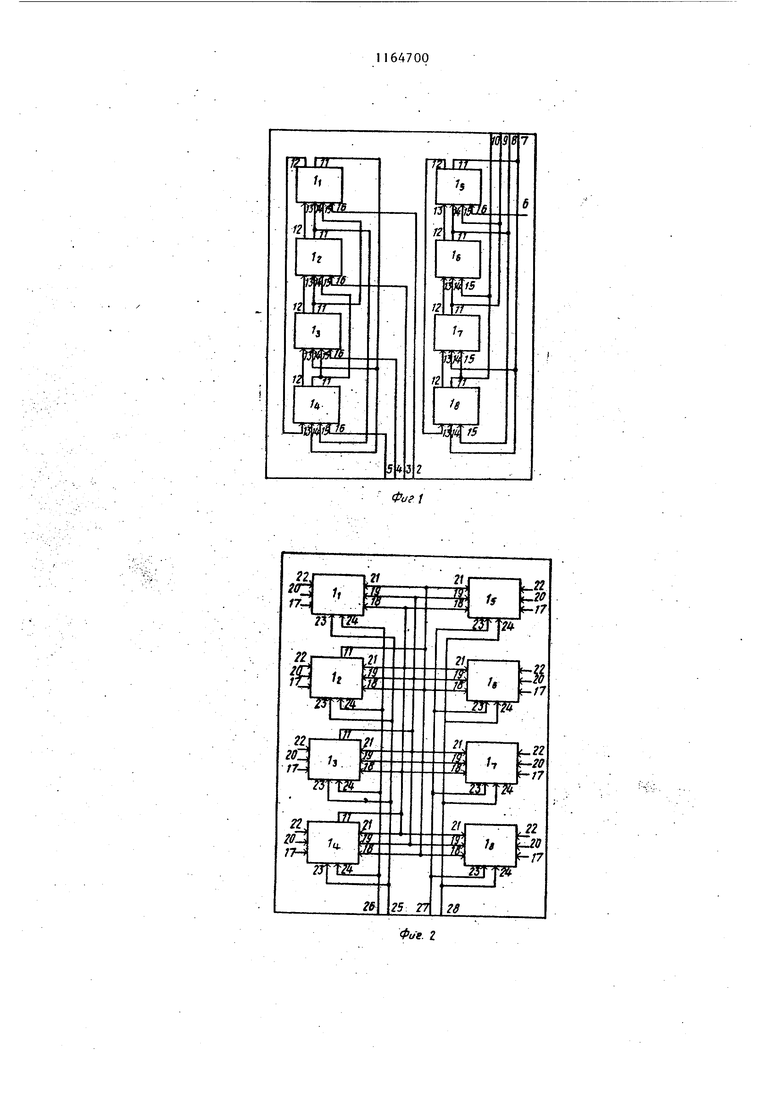

сдвигом вправо на та разрядов двоичных кодов чисел. Пользуясь элементами t ( i а j)fcT построим итерационный процесс начинающийся с q . n.. где , 1, 2, ...,га m(n), Знаки , , 1| J, 3 и функции m m{n) выберем такими, чтобы обеспечивалась сходимость в смысле О при п- схз (6 Для этого необходимо ,„ - sign Ь„, г211 - sign Сп, Ьп - sign tJn. тогда лыбор зависимости m m(n) мо жет обеспечить неравенстБ 5 Ь + с где R - const. С уче том свойства нормированности (3), такая сходимость означает c - anto; + oi+0ic , Sn-i ol-U.oUt.b.... Нормы всех кватернионов из Т извест rad (t) ЧГ7., следовательно 01„-Цо1 « С другой стороны, в силу того, что множители при кватернионных единицах (мнимая часть кватерниона стремятся к нулю, произведение .П t.,(i) . стремится к кватерниону, пропорциональному q , а именно: (иЛаЬ зО-ТГГ п Координатное представление этого произведения таково: .(;v-K(ci«+i +i f«vkB), , (to -Со о -00 biN Ю 1чо1 Ю при п - 00 Полученные выражения являются нап равлянщими косинусами вектора {а, bjj, с„, d в четырехмерном евклидо вом пространстве. Таким образом, в итерационном пр цессе (5) может быть вычислен модул четьфехмерного вектора двух- и трех ерного). Одновременно-может вычисяться произведение кватернионов tm(i) (,. f 2 jj) на 1/k + О- + 01 + 0,j в процессе, аналогичном (5). Окончательно способ вычисления аправляющих косинусов вектора в ространстве для аппаратной реализаии таков: I.Начальные данные ,, ,p . , II.Итера1щя fn m(n) ,5;gol),, .,(,„.Х,.,.;.«,„,а,.,). Ь„-V-,(-,„-,o „ + 2n-1Зn-t- зno n-,V . Ичп-|ап-Г 2пи г м Эп ) j«-a«.,2-™i,,c«.rW,bn-.- 3h-v°h.;v . Ill Итерация .,,,f4«.,+ ,,t,,6n-0; . .,г-(-,«.«п.1-1г.Б«-1- зЛ«-1У, Ь-Уп.И2-(-и8„..М Вп Vr2- U.nYn-r 2,f. « «-ОIV.Если п N, то п п + 1 и осуествляется переход к II в другом V. V.Стоп. Приняты слёдукщие обозначения: п 0, 1, 2i...,N - порядковый-но,мер итерации, а, Ьд, Сд, d - начальные условия-проекции вектора на оси координат X, у, Z, tj m ш(п) - таблично заданная функция, определяющая степень сдвига на п-й Итера- п-т J- ЦИИ1 . + З. константа}. конечные значения-направляющие косинусы вектора в пространстве. q -о - текущие значения перемен ной, вычисленное на п-й итерации, .n- знаки текущего значения переменных h. tp - операционное время сумма- тора-йычитате ля или преобразователяпрямого кода в дополнител ньй; t црт - время записи . кода в регист 30 и регистрсдвигатель37} t.g - время сдвига кода на регистр-сдвигателе 37 на m разрядов вправо m in(n) - таблично заданная функция, определяющая степе сдвига на п-й итерации . Подключение управляющих входов устройств даны в таблице. На выходах итерационных блоков после п-й итерации формируются сле дующие значения: блок 1|: выход 11 - а, выход 12-2 ( Ч - fin m блок выход 11 - Ьм, выход 12-2 1пЬи + .г блок 1j : выход 11. - с,,, выход 12-2 г.п v)J -п блок Ц: выход 11 - d, выход 12-2 fin п f . блок выход 11 .,, выход 12 - ( f n n-i+finN-rfinYn-i) блок 1j: выход 11 -/5,н выход 12 .nN-n.nj nf3nen.,v, блок ly : выход ir-Jn-.,, выход 12 S3nJn-i f n n r zn п-ч) t J9t V I I С - Г г f блок 1.: выход 11 -Ьп-1 выход 12 - (%.8,.-i-bn/ h-a Работа операционных блоков иллюстрируется на примере блока l. За начальный момент t t- примем состояние, при котором на регистре 30 находится код Ь., , а на входе 13 блока - код 2(5,.,с;., + ,„.а., Mn-i П5 ) Состояние остальных элементов и входов итерационного блока в этот момент несущественно. Поскольку вход 17 жестко закоммутирован на операцию Минус на выходе сумматора-вьгчитателя 31 и, следовательно, на выходе 11 операционного блока через время , будет сформирован код Ь„ Ьп.,- 2-(f,, с.1 + П-. П-1 2h-1 к тому же моменту времени на входе 14 блоком 1j будет сформировано значение с., на входе 15 блоком Ц значение d , а на входах 18, 19, 21 соответственно 1п , „ , j ,п К моменту времени t 2tg на выходе преобразователя 32 будет оформи- poBaiH код „ , bf,, на выходе преобразователя 33 - код 2 с, на выходе преобразователя 35 - код d. Поскольку.входы 20 и 22 блока жестко закоммутированы на операцию Плюс к моменту времени t 3tc/y, на выходе сумматора-вычитателя 34 будет сфор- . мирован код , к моменту времени t выходе сумматора-вычитателя-36 - + 2г п этому моменту времени устанавливается действукхцее значение управляющего сигнала на входе 23 блока и значение Ь, через группу элементов ИЛИ 29 запоминается на.регистре 30, а значение , Ь,, + 2 п 3 п 3 сдвигателе 37. При этом в соответствии с кодом m на входе 24 блока происходит сдвиг содержимого сдвигателя 37 на m разрядов вправо, т.е. формируется 2(, гл п зп таким образом через время t 4tcy,. + t уст. + на n-й итерации блок Ц сформирует на регистре 30 значение bjj для себя и на выходе 12 блока-зкачение (4г,Ь, .п Ьп lh) дая п + 1 итерации для другого . Перед началом работы устройства происходит загрузка начальных значе ний ад, Ьд, Сд, do, которые к этому Моменту присутствую на входах 2, 3, 4, 5 устройства. Действующее значение управляющего сигнала на входе 25 II . устройства приводит к запоминанию этих кодов через второй вход труппы элементов ИЛИ 29 на регистре 30 в блоках 1{-14- С этого момента нач нается отсчет времени работы устрой ства. Спустя время t ctf, сигналы на .входах 25 и 27 устройства действуют одновременно. Это приводит к тому, что на регистрах 30 блоков перезаписывается значение а, Ьр, Сд, dfj, на выходах 12 этих блоков формируется значение вида ( I 10 Ь(,+ 20 Си + f 30 dp) для второго блока, т.е. полностью отрабатывается нулевая итерация, а на регистре 30 блока Ig запоминается константа oi; . В дальнейшем блоки устройства работают параллельно и каждая итера ция может быть условно разбита на два этапа: в первом происходит распространение кодов через комбинационные элементы 29, 31-36, а -во втором - запоминание и сдвиг промеж точных значений на регистре 30 и сдвигателе 37. Сигналы на входах 25 и 27 устройства действуют одновре17 18

12

17 18 УО12 менно. На управляющем.входе 26 устройства на п-й итерации, присутствует код ш m(n), а на входе 28 - код m m(n - 1), Таким образом, в результате п-й итерации на регистрах 30 блоков 1(-Ц запоминаются значения а , Ьц, с„, dn, а блоков 1-1 значения of«., , р„., , J „. К моменту времени t « Nt + на выходах 11 блоков ly 1б г устанавливаются значения (Х н /щ S N Подача сигналов на управляюnpie входы 25 и 27 прекращается, на выходах 7, 8, 9 и 10 устройства присутствуют значения М , |) н , f N , Б (которые и являются искомыми величинами - направляющими косинусами вектора в пространстве. Эффективность предлагаемого устройства; состоит в существенном уменьшении времехш вычисления в це- лом .классе задач, возможности создания диалоговых средств взаимодействия в человеко-машинных системах, а следовательно, ускорения времени решения проблема, повшвении качества и достоверности решения.

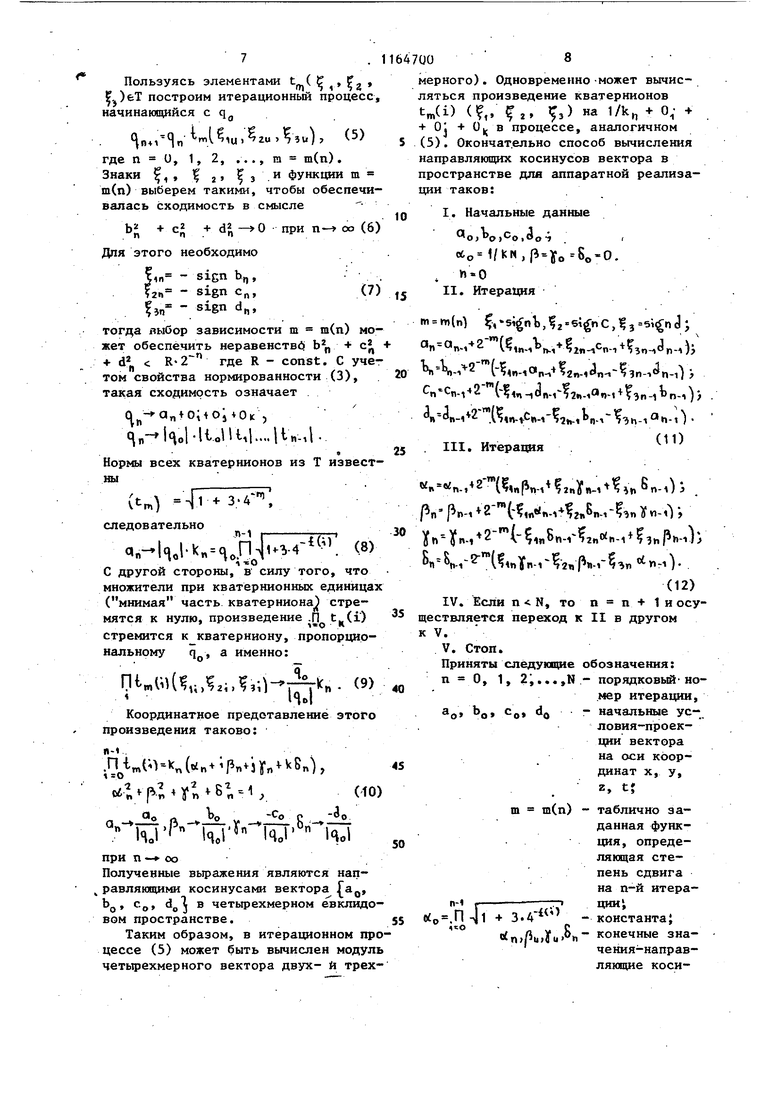

19 20 21 22

1,

Ь

Пдюс

Минус

17 18 19 20

1,

Плюс

21 22

1,

Минус

17 18 19 20 21 22

Ь

Плюс

tfaHyc

19 20 21 22

1э

Плюс

Ч

Минус

Плюс

Минус

t, 1э

Плюс

Минус

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления тригоно-МЕТРичЕСКиХ фуНКций | 1979 |

|

SU832555A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для реализации алгоритмаВОлдЕРА | 1978 |

|

SU813421A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-30—Публикация

1982-08-17—Подача