второго регистра состояния и схемы cpaвt eния, выход второго регистра состояния соединен с вторым входом сразкения и с первым входом блока управления, первый выход которого соединен с третьим входом блока приоритетов, второй вход блока управления соединен с третьим входом первого регистра состояния, выход блока приоритетов соединен с вторым входом блока управления, выходы первого и второго выходных регистров соединены соответственно с первым и вторым входами блока выдачи информации , первый и второй выходы которого являются соответственно первым и вторым выходами устройства, заедены третий и четвертый регистры состояния дополнительная схема сравнения и два коммутатора, причем выход первого коммутатора соединен с первым вхо- дом блока приема информации и с первым выходом устройства, выход второг коммутатора соединен с вторым входом блока приема информации и с вторым выходом устройства, первые входы первого и второго коммутаторов соединены соответственно с первым и вторым входами устройства, вторые входы первого и второго коммутаторов соединены соответственно с третьим и четвертым входами устройства,третьи входы первого и второго коммутаторов соединены с третьим выходом блока управления, первый вход третьего регистра состояния соединен с первьм выходом блока приема информации,второй вход третьего регистра состояния соединен со вторым выходом блока приема информации, третий вход третьего регистра состояния соединен с вторым входом второго регистра состояния, с первым входом четвертого регистра состояния, с первым выходом блока управления и с третьим входом блока выдачи информации, четвертый выход блока управления соединен с четвертым входом третьего регистра состояния, третий и четвертый входы блока управления соединены с выходами соответственно основной и дополнительной схем сравнения, пятый вход блока управления соединен с выходом четвертого регистра состояния и с первы входом до.полнительной схемы сравнения, выход третьего регистра состояния соединен с вторыми входами четвертого регистра состояния, первого и второго выходных регистров и дополнительной схемы сравнения, третьи входы Первого и второго выходных регистров соединены с выходом первого регистра состояний.

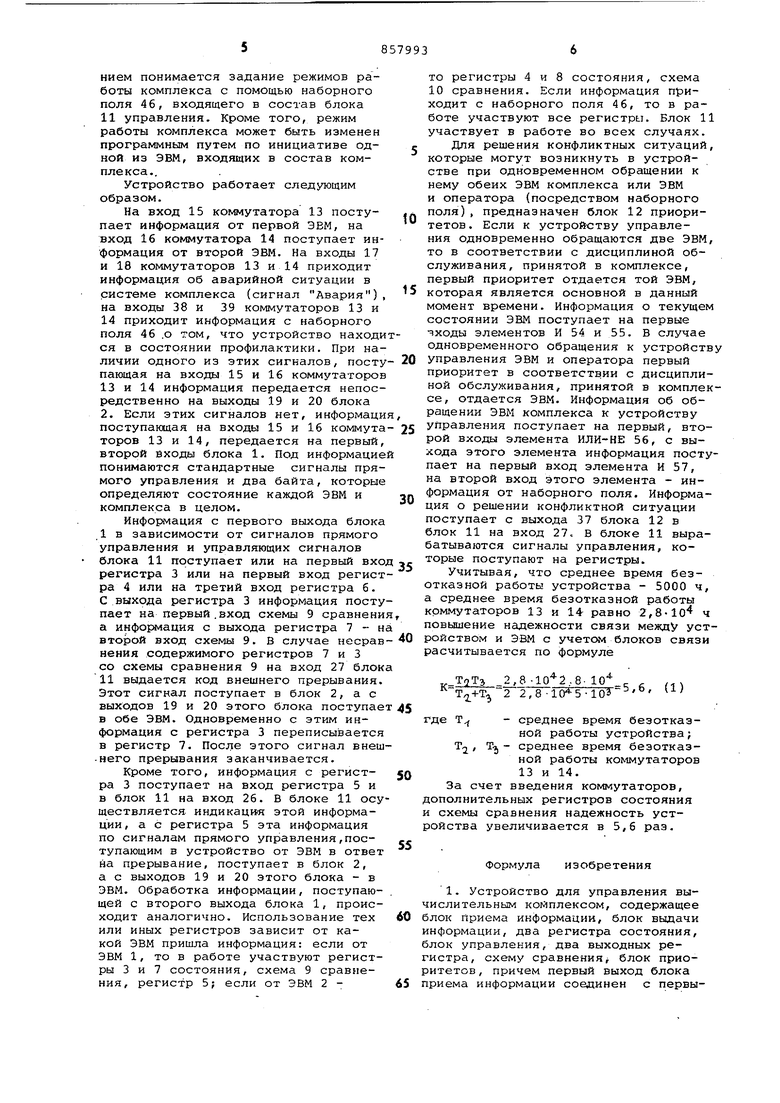

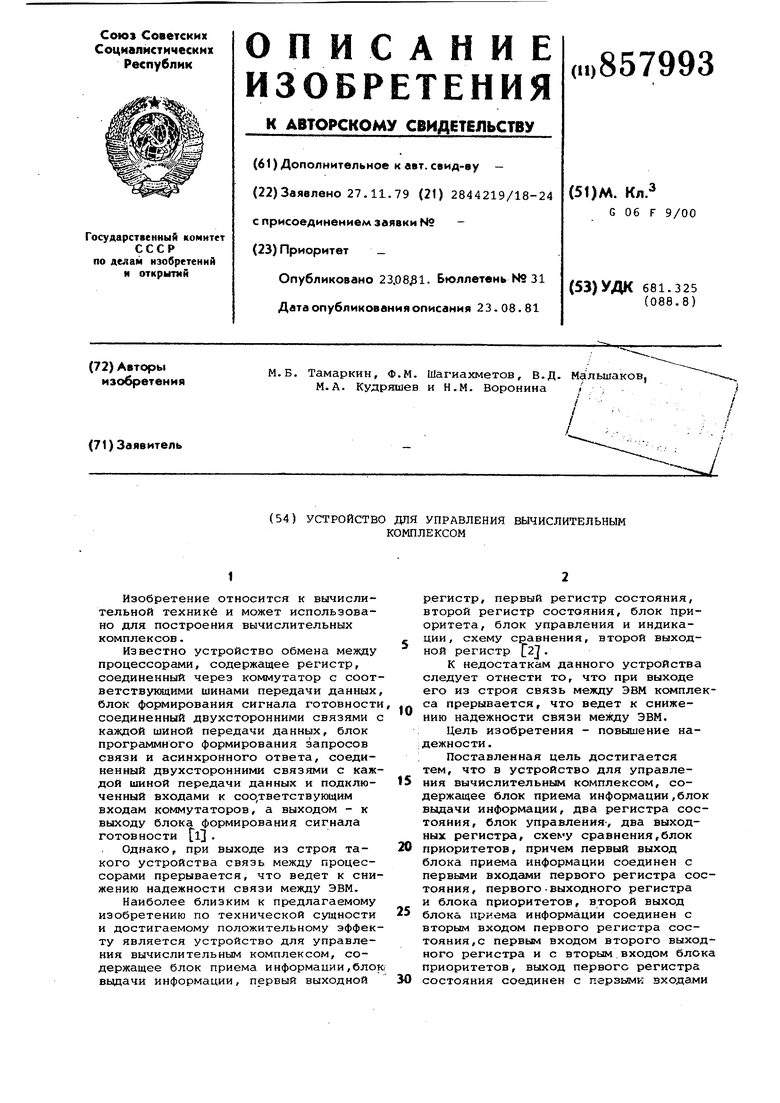

Кроме того, блок управления содержит дешифраторы, триггеры, элементы И, ИЛИ и наборное поле,причем вход первого дешифратора соединен с первым входом первого элемента ИЛИ и является пятым входом блока, выход первого дешифратора соедгнен с первым входом первого элемента И,выход которого соединен с входом первого триггера, выход которого является четвертым выходом блока, вход второг дешифратора соединен.с вторым входом первого элемента ИЛИ и является первым входом блока, выход второго дшифратора соединен с первым входом второго элемента И, выход которого соединен с входом второго триггера, выход которого является вторым выходом блока, вторые входы первого и второго элементов и и первый вход третьего дешифратора объединены между собой и являются вторым входом блока, третий и четвертый входы и выход первого элемента ИЛИ соединены соответственно с выходом дешифратора выходом второго элемента ИЛИ и входо триггера, выход которого является первым выходом блока, первый и второй входы второго элемента ИЛИ являются соответственно третьим и четвертым входами блока, выход наборного поля соединен с вторым входом третьего дешифратора и является третьим выходом блока.

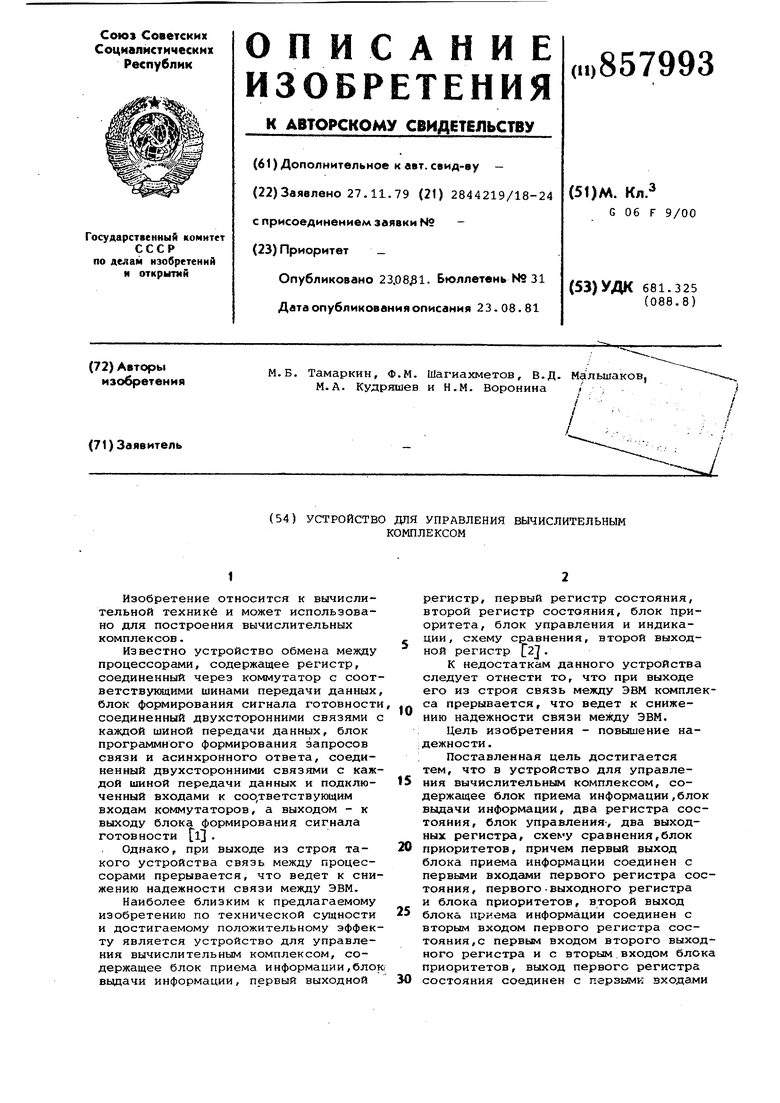

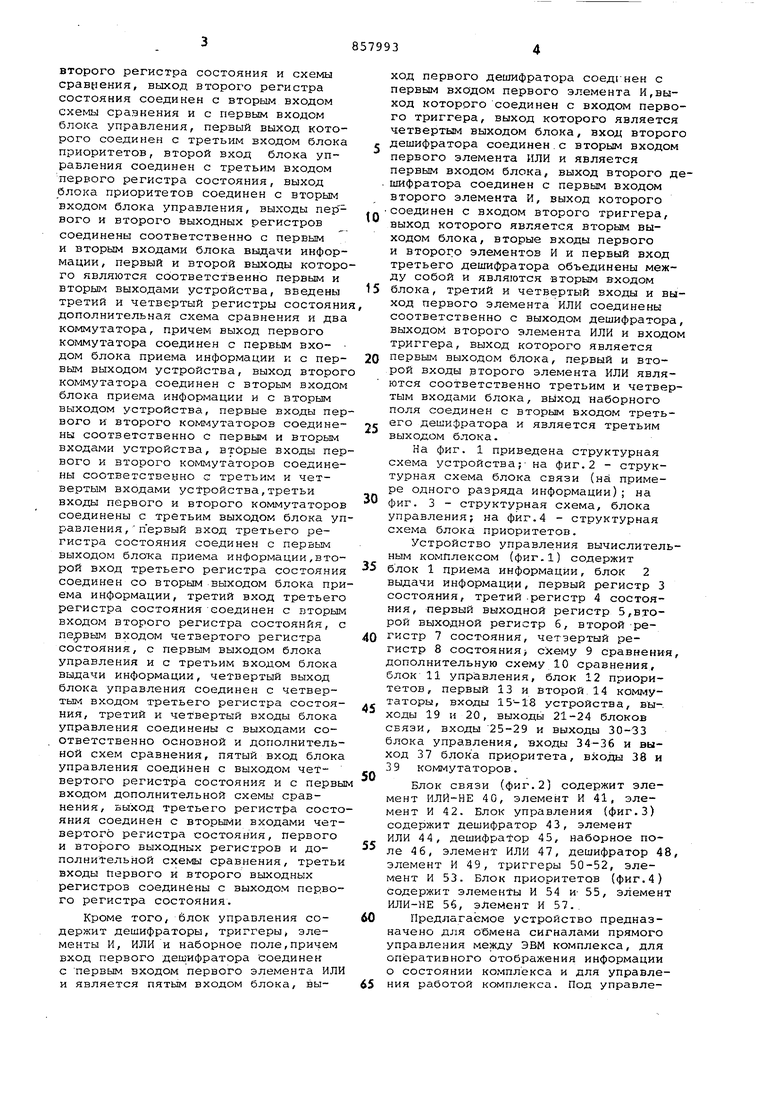

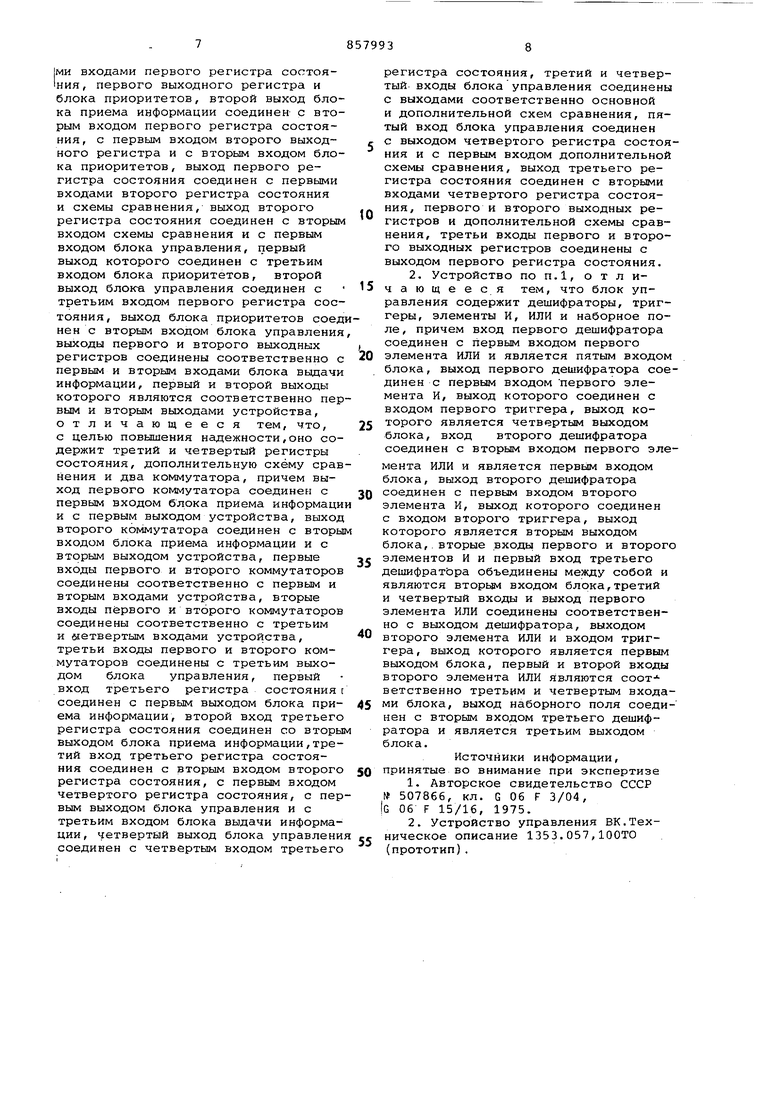

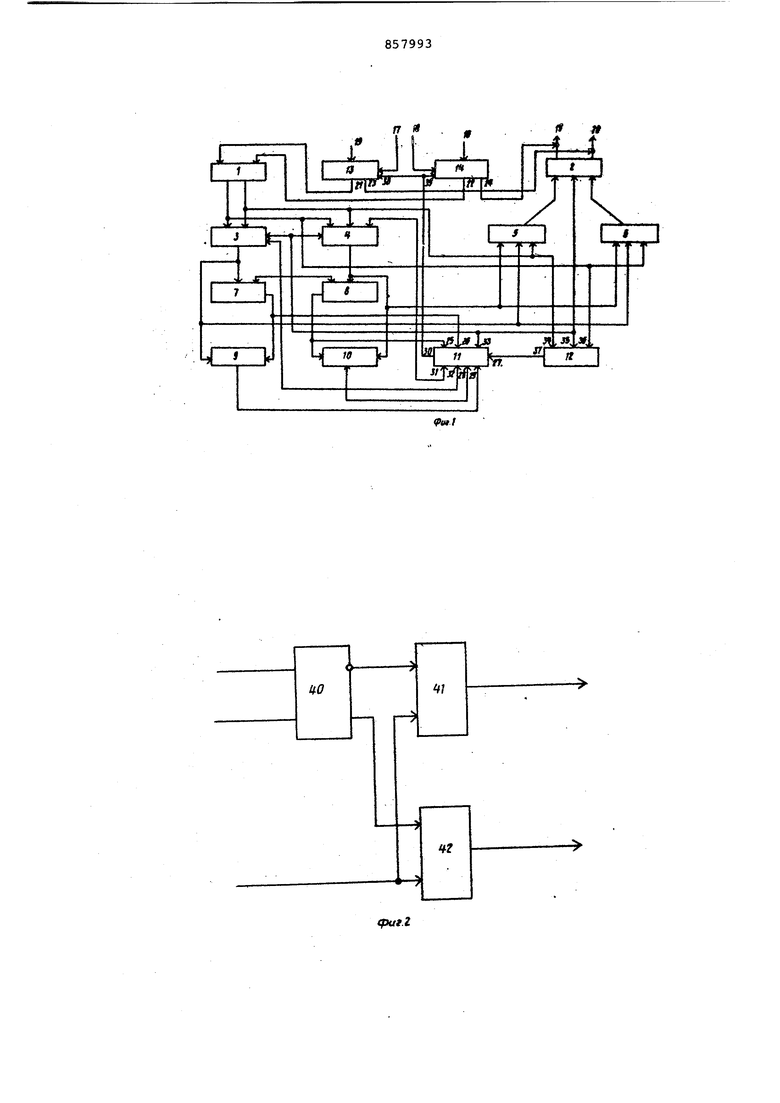

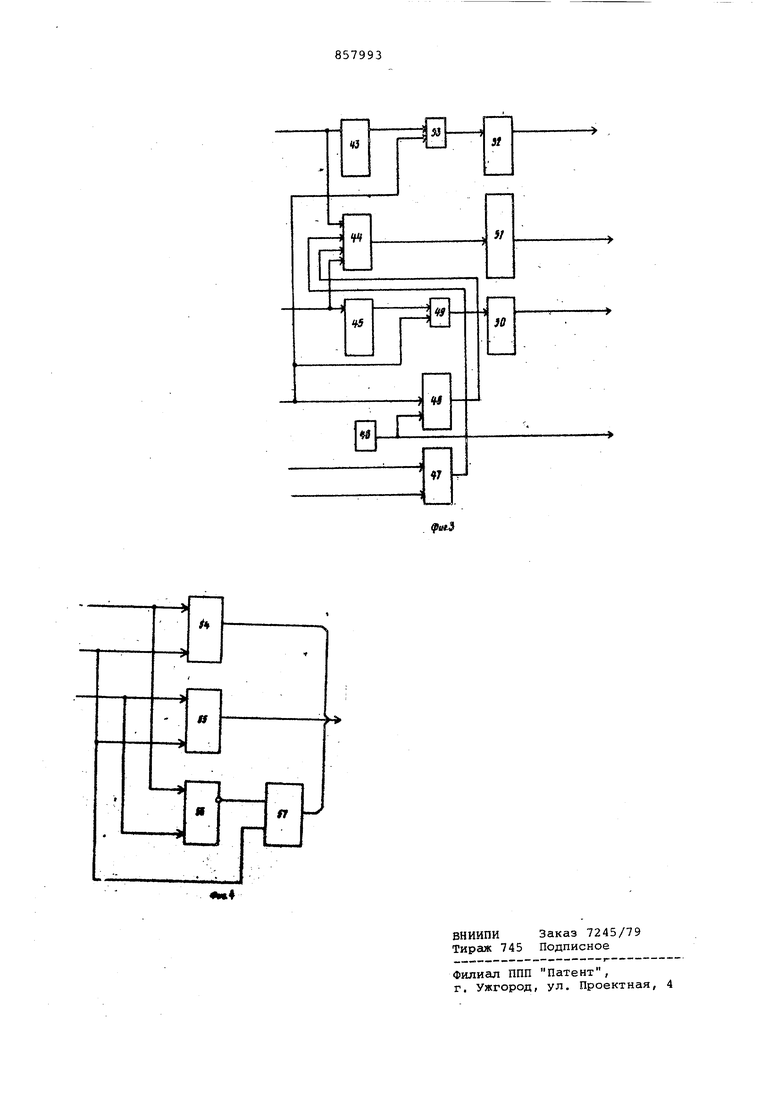

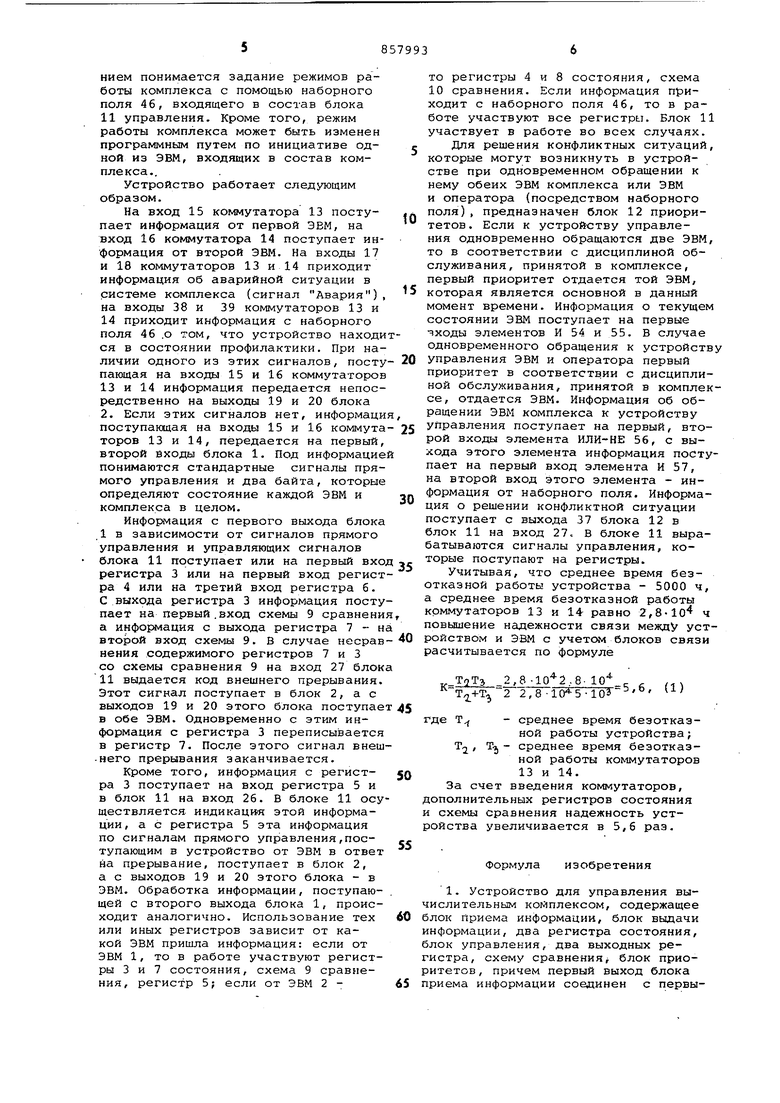

На фиг. 1 приведена структурная схема устройства; на фиг.2 - структурная схема блока связи (на примере одного разряда информации); на фиг. 3 - структурная схема, блока управления; на фиг.4 - структурная схема блока приоритетов.

Устройство управления вычислительным комплексом (фиг.1) содержит блок 1 приема информации, блок 2 выдачи информации, первый регистр 3 состояния, третий .регистр 4 состояния, первый выходной регистр 5,второй выходной регистр б, второй -регистр 7 состояния, четвертый регистр 8 СОСТОЯНИЯ) схему 9 сравнения дополнительную схему 10 сравнения, блок 11 управления, блок 12 приоритетов, первый 13 и второй.14 коммутаторы, входы 15-18 устройства, вы-, ходы 19 и 20, выходы 21-24 блоков связи, входы 25-29 и выходы 30-33 блока управления, входы 34-36 и выход 37 блока приоритета, входы 38 и 39 коммутаторов.

Блок связи (фиг.2) содержит элемент ИЛЙ-НЕ 40, элемент И 41, элемент И 42. Блок управления (фиг.З) содержит дешифратор 43, элемент ИЛИ 44, дешифратор 45, наборное поле 46, элемент ИЛИ 47, дешифратор 48 элемент И 49, триггеры 50-52, элемент И 53. Блок приоритетов (фиг.4) содержит элементы И 54 и- 55, элемент ИЛИ-НЕ 56, элемент И 57..

Предлагаемое устройство предназначено для обмена сигналами прямого управления между ЭВМ комплекса, для оперативного отображения информации о состоянии комплекса и для управления работой комплекса. Под управлением понимается задание режимов работы комплекса с помощью наборного поля 46, входящего в состав блока 11 управления. Кроме того, режим работы комплекса может быть изменен программным путем по инициативе одной из ЭВМ, входящих в состав комплекса..

Устройство работает следующим образом.

На вход 15 коммутатора 13 поступает информация от первой ЭВМ, на вход 16 коммутатора 14 поступает информация от второй ЭВМ. На входы 17 и 18 коммутаторов 13 и 14 приходит информация об аварийной ситуации в системе комплекса (сигнал Авария), на входы 38 и 39 коммутаторов 13 и 14 приходит информация с наборного поля 46 .о том, что устройство находится в состоянии профилактики. При наличии одного из этих сигналов, поступающая на входы 15 и 16 коммутаторов 13 и 14 информация передается непосредственно на выходы 19 и 20 блока 2. Если этих сигналов нет, информация поступающая на входы 15 и 16 коммутаторов 13 и 14, передается на первый, второй входы блока 1. Под информацией понимаются стандартные сигналы прямого управления и два байта, которые определяют состояние каждой ЭВМ и комплекса в целом.

Информация с первого выхода блока

Iв зависимости от сигналов прямого управления и управляющих сигналов блока 11 поступает или на первый вход регистра 3 или на первый вход регистра 4 или на третий вход регистра 6.

С выхода регистра 3 информация поступает на первый.вход схемы 9 сравнения а информация с выхода регистра 7 - на второй вход схемы 9. В случае несравнения содержимого регистров 7 и 3 со схемы сравнения 9 на вход 27 блока

IIвыдается код внешнего прерывания. Этот сигнал поступает в блок 2, а с выходов 19 и 20 этого блока поступает в обе ЭВМ. Одновременно с этим информация с регистра 3 переписывается

в регистр 7. После этого сигнал внеш-него прерывания заканчивается.

Кроме того, информация с регистpa 3 поступает на вход регистра 5 и в блок 11 на вход 26. В блоке 11 осуществляется индикация этой информации, а с регистра 5 эта информация по сигналам прямого управления,поступающим в устройство от ЭВМ в ответ на прерывание, поступает в блок 2, а с выходов 19 и 20 этого блока - в ЭВМ. Обработка информации, поступающей с второго выхода блока 1, происходит аналогично. Использование тех или иных регистров зависит от какой ЭВМ пришла информация: если от ЭВМ 1, то в работе участвуют регистры 3 и 7 состояния, схема 9 сравнения, регистр 5; если от ЭВМ 2 то регистры 4 и 8 состояния, схема 10 сравнения. Если информация приходит с наборного поля 46, то в работе участвуют все регистры. Блок 11 участвует в работе во всех случаях.

Для решения конфликтных ситуаций, которые могут возникнуть в устройстве при одновременном обращении к нему обеих ЭВМ комплекса или ЭВМ и оператора (посредством наборного поля), предназначен блок 12 приоритетов. Если к устройству управления одновременно обращаются две ЭВМ, то в соответствии с дисциплиной обслуживания, принятой в комплексе, первый приоритет отдается той ЭВМ, которая является основной в данный момент времени. Информация о текущем состоянии ЭВМ поступает на первые чходы элементов И 54 и 55. В случае одновременного обращения к устройств управления ЭВМ и оператора первый приоритет в соответстзэии с дисциплиной обслуживания, принятой в комплексе, отдается ЭВМ. Информация об обращении ЭВМ комплекса к устройству управления поступает на первый, второй входы элемента ИЛИ-НЕ 56, с выхода этого элемента информация поступает на первый вход элемента И 57, на второй вход этого элемента - информация от наборного поля. Информация о решении конфликтной ситуации поступает с выхода 37 блока 12 в блок 11 на вход 27. В блоке 11 вырабатываются сигналы управления, которые поступают на регистры.

Учитывая, что среднее время безотказной работы устройства - 5000 ч, а среднее время безотказной работы коммутаторов 13 и 14 равно 2,8-10 ч повышение надежности связи между устройством и ЭВМ с учетом блоков связи расчитывается по формуле

2,8 10-2.8- 10

(1) 2 2,8-10 5-103

где Т

- среднее время безотказной работы устройства; Т, T-J - среднее время безотказной работы коммутаторов 13 и 14.

За счет введения коммутаторов, дополнительных регистров состояния и схемы сравнения надежность устройства увеличивается в 5,6 раз.

изобретения

Формула

1. Устройство для управления вычислительным комплексом, содержащее блок Приема информации, блок выдачи информации, два регистра состояния, блок управления, два выходных регистра, схему сравненияj блок приоритетов , причем первый выход блока приема информации соединен с первыми входами первого регистра состояния, первого выходного регистра и блока приоритетов, второй выход блока приема информации соединен с вторым входом первого регистра состояния, с первым входом второго выходного регистра и с вторым входом блока приоритетов, выход первого регистра состояния соединен с первыми входами второго регистра состояния и схемы сравнения, выход второго регистра состояния соединен с вторым входом схемы сравнения и с первым входом блока управления, первый выход которого соединен с третьим входом блока приоритетов, второй выход блока управления соединен с третьим входом первого регистра состояния, выход блока приоритетов соеднен с вторым входом блока управления выходы первого и второго выходных регистров соединены соответственно с первым и вторым входами блока выдачи информации, первый и второй выходы которого являются соответственно первым и вторым выходами устройства, отличающееся тем, что, с целью повышения надежности,оно содержит третий и четвертый регистры состояния, дополнительную схему сравнения и два коммутатора, причем выход первого коммутатора соединен с первым входом блока приема информаци и с первым выходом устройства, выход второго коммутатора соединен с вторы входом блока приема информации и с вторым выходом устройства, первые входы первого и второго коммутаторов соединены соответственно с первым и вторым входами устройства, вторые входы первого и второго коммутаторов соединены соответственно с третьим и четвертым входами устройства, третьи входы первого и второго коммутаторов соединены с третьим выходом блока управления, первый вход третьего регистра состоянияt соединен с первым выходом блока приема информации, второй вход третьего регистра состояния соединен со вторы выходом блока приема информации,третий вход третьего регистра состояния соединен с вторым входом второго регистра состояния, с первым входом четвертого регистра состояния, с первым выходом блока управления и с третьим входом блока выдачи информации, четвертый выход блока управлени соединен с четвертым входом третьего

регистра состояния, третий и четвертый входы блока управления соединены с выходами соответственно основной и дополнительной схем сравнения, пятый вход блока управления соединен с выходом четвертого регистра состояния и с первым входом дополнительной схемы сравнения, выход третьего регистра состояния соединен с вторыми входами четвертого регистра состояния, первого и второго выходных регистров и дополнительной схемы сравнения, третьи входы первого и второго выходных регистров соединены с выходом первого регистра состояния.

2. Устройство по П.1, отличающееся тем, что блок управления содержит дешифраторы, триггеры, элементы И, ИЛИ и наборное поле , причем вход первого дешифратора соединен с первым входом первого элемента ИЛИ и является пятым входом блока, выход первого дешифратора соединен с первым входом первого элемента И, выход которого соединен с входом первого триггера, выход которого является четвертым выходом блока, вход второго дешифратора соединен с вторым входом первого элемента ИЛИ и является первым входом блока, выход второго дешифратора соединен с первым входом второго элемента И, выход которого соединен с входом второго триггера, выход которого является вторым выходом блока,. вторые входы первого и второг элементов И и первый вход третьего дешифратЬра объединены между собой и являются вторЕФ ВХОДОМ блока,третий и четвертый входы и выход первого элемента ИЛИ соединены соответственно с выходом дешифратора, выходом второго элемента ИЛИ и входом триггера , выход которого является первым выходом блока, первый и второй входы второго элемента ИЛИ являются соответственно третьим и четвертым входами блока, выход наборного поля соединен с вторым входом третьего дешифратора и является третьим выходом блока.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 507866, кл. G 06 F 3/04,

JG 06 F 15/16, 1975.

2.Устройство управления ВК.Техническое описание 1353.057,100ТО (прототип).

Ц-0

;

S3

it

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения | 1980 |

|

SU888098A1 |

| Устройство для обмена информацией | 1986 |

|

SU1336017A1 |

| Устройство сопряжения | 1981 |

|

SU993240A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство для сопряжения датчиков с ЭВМ | 1983 |

|

SU1129600A1 |

| Устройство для сопряжения каналовВВОдА-ВыВОдА C уСТРОйСТВОМ упРАВлЕНияОпЕРАТиВНОй пАМяТью МНОгОпРОцЕССОР-НОй ВычиСлиТЕльНОй МАшиНы | 1979 |

|

SU822168A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1985 |

|

SU1272336A2 |

| УСТРОЙСТВО ИДЕНТИФИКАЦИИ ТЕРМИНАЛЬНОГО ПОЛЬЗОВАТЕЛЯ | 1994 |

|

RU2111530C1 |

w

w

Jfl

Авторы

Даты

1981-08-23—Публикация

1979-11-27—Подача