(54) СЛЕДЯЩИЙ АНАЛОГО-иИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий аналого-цифровой преобразова-ТЕль | 1979 |

|

SU828401A1 |

| Цифровой коррелятор | 1979 |

|

SU842768A1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Преобразователь напряжения в код | 1973 |

|

SU486471A2 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| Цифровой коррелятор | 1980 |

|

SU894719A1 |

| Аналого-цифровое интегрирующее устройство | 1985 |

|

SU1275483A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU797064A1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

| Преобразователь напряжения в код | 1976 |

|

SU577669A1 |

I

Изобретение относится к облйсти аналого-цифровых преобразователей и может быть исаюльзовано в области связи, вы- числительной и ка 1ерительной техники, а также- в автоматизированных системах ущэавления технологическими процессами и системах автоматизации научных иоследований.

По основному авт. св. № 8284О1 вэвестен слецяший аналого-цифровой преобразователь, содержащий блок сравнения, первый вход которого соединен с датчиком входного сигнала, а второй - с выходом цифро-аналогового преобразователя порядка, вход которого соединен с выходом цифро-аналогового преобразователя мантиссы, вход которого соединен с выходом источника опорного сигнала, цифровые входы ци(} о-аналогового преобразователя порядка соединены с ы 1хоаами деши(|)ратора, входы которого соединены с выходами соответствующих разрядов счетчика мантиссы и блока ({)qpм1фoвaния шага, выход блока сравнения соединен

с первым входом блока управления, второй вход которого соединен с выходом генератора тактовых импульсов, а тре тий - с eднничньвv( выходом триггера йереполнения счетчика поряшса, первый в второй выходы блока управления 9 соединены с входами установки режима работы реве1 сивных счетчиков порядка и мантиссы, третий - с первыми входами грутшы элементов И, вторые входы которых ссн единены с соответствующими выходами блока ({юрмирсвания шага, четвертый и пятый выходы блока управления соединены соответственно с первым и вторым . управляющими входами блока ({юрмировання шага, третий и четвертый управляющие вхооы которого соединены с выходами цепей переноса счетчика мантиссы и с соответствующими входами счетчика порядка.

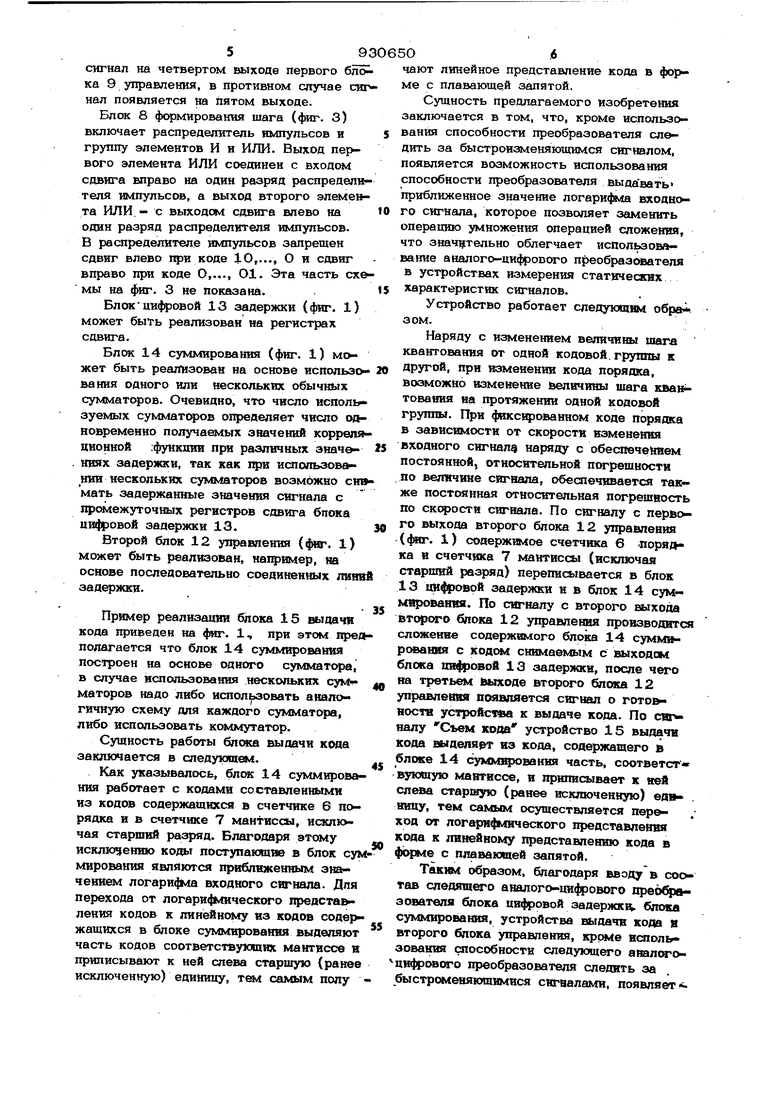

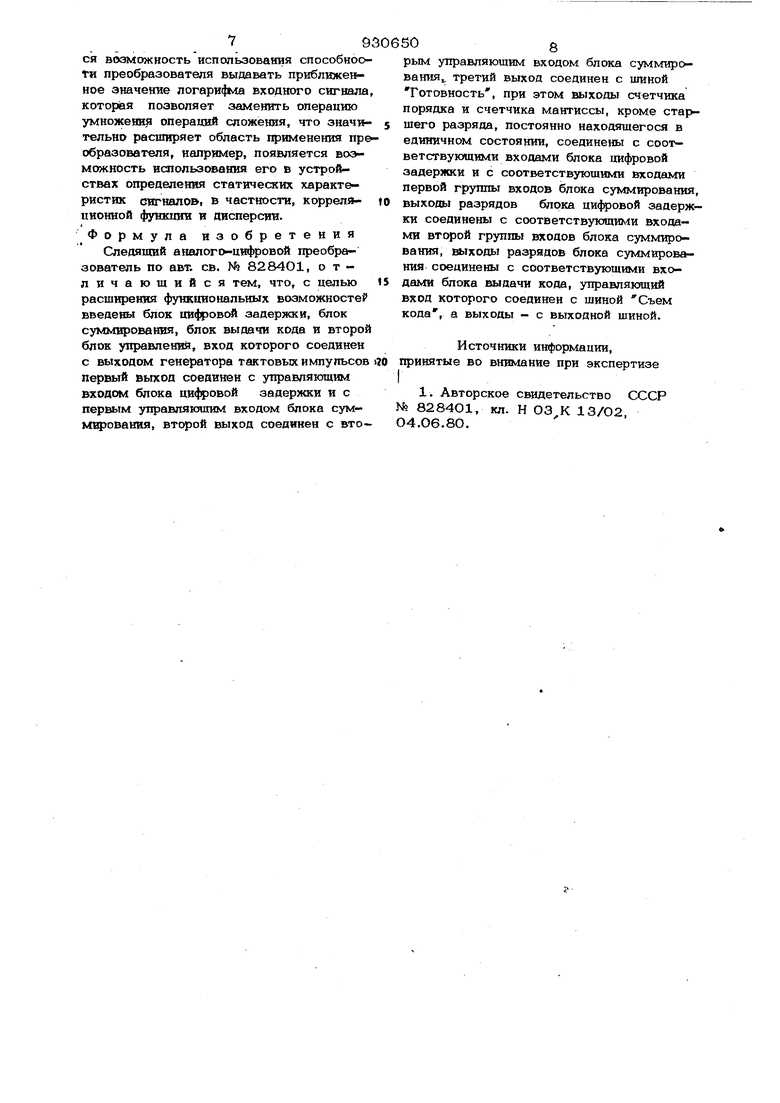

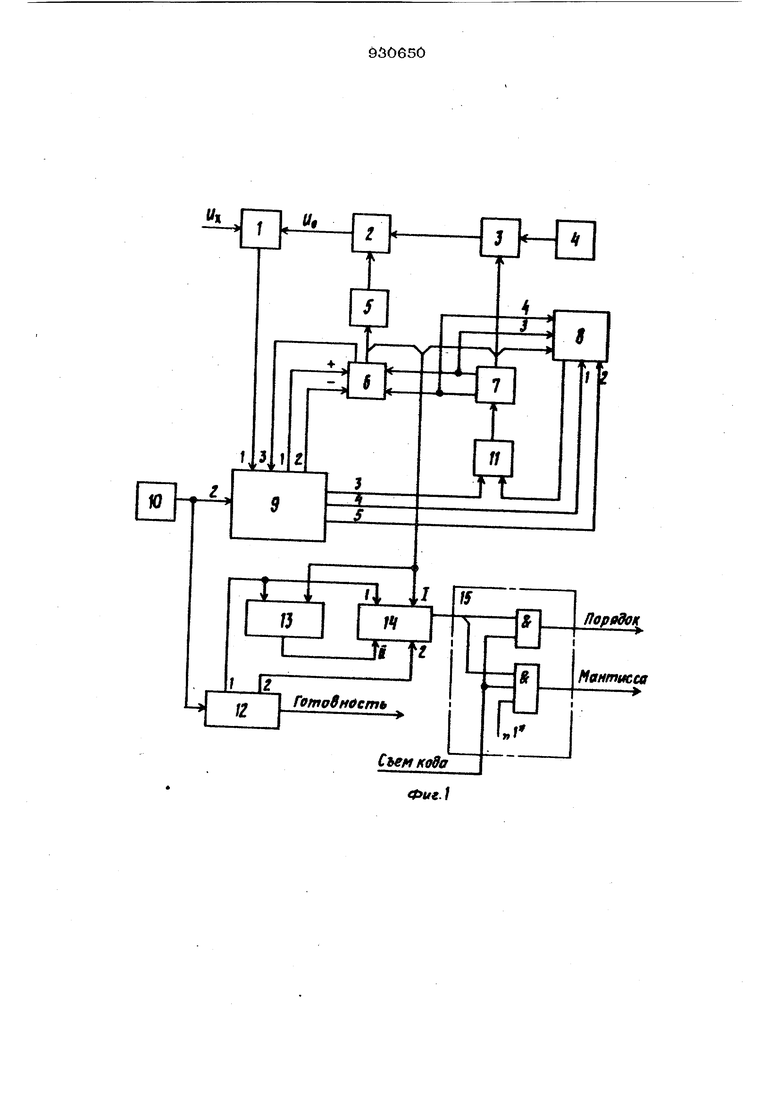

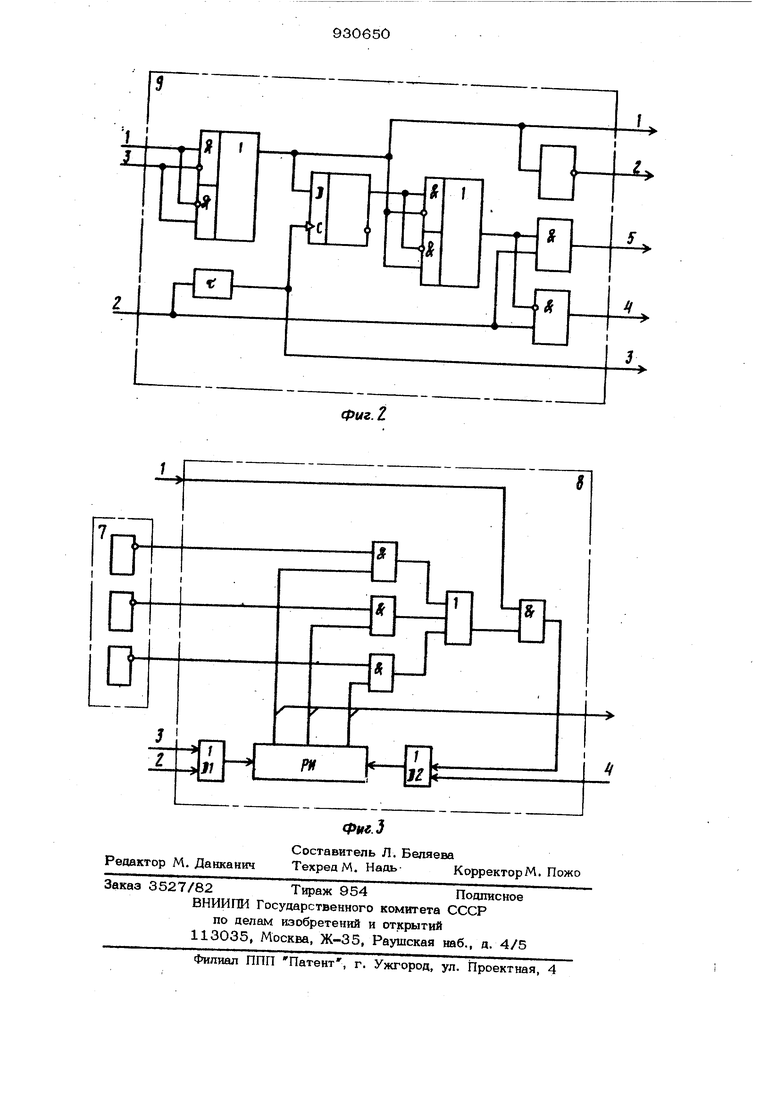

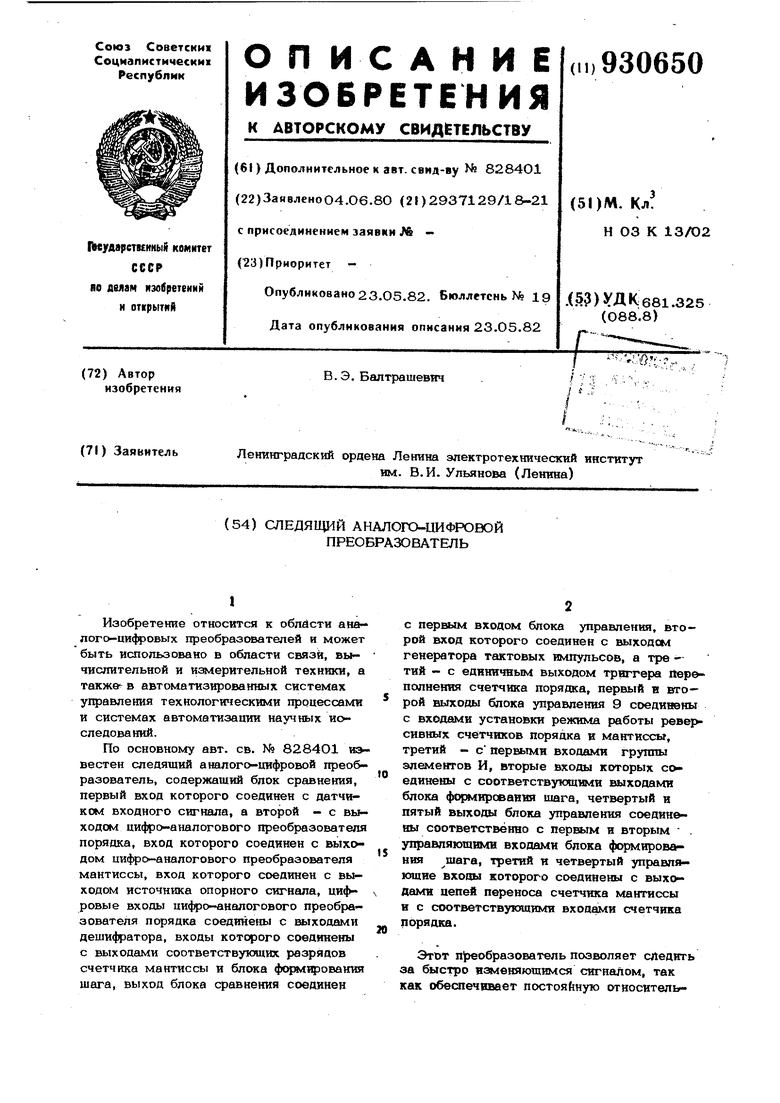

Этот п)реобразователь позволяет следить за быстро изменяющимся сигналом, так как обеспечивает постоянную относительную погрешность квантования сигнала как по величине, так и по скорости. Кроме того, из-за постоянно относительной погрешности квантования величины сигнала и представления выходного кода в форме с плавающей запятой с это го АЦП можно получить логари4мический код значения входного гшгнала, если из рассмотрения убрать старший, постоянно находящийся в единичном состоянии разряд счетчика мантиссы С -ЗОднако этот преобразователь нельзя использовать при измерении корреляционных функций:, так как он не имеет функциональных возможностей для сложения логари4мических кодов двух задержанных друг относительно друга значений сигнала и перевода полученного значения из логарифмического масштаба в линейньтй. Таким образом, недостатком извесрного устройства являются ограниченные функциональные возможности. Цель изобретения - расширение функпи ональиых возможностей. Поставленная цель достигается т&л, что в следяший аналого- ци4ровой преобра зователь, содержащий блок сравнения, первый вход которото соединен с яатчИком входного , а второй - с ци4) налогового преобразователя порядка, вход которого сое{шнен с выходсоь цифро-аналогового преобразователя мантиссы, вход которого соединен с выхоаам источника спорного -сигнала, шфровые входьт ц ро аналогового преофазова теля порядка соединеш 1 с ззыходами дешифратора, входы которого соединены с вь1ходами соответствующих разрядов счетчика порядка, а цифровые входы цифр аналогового 1феобразователя мантиссы со ед{тены непосредственно с выходами соот;ветствуюших разрядов счетчика ман тиссы и блока фс ялирования шага, вь&ход блока сравнения соединен с первым входс«4 первого блока управления, второй вход которого соединен с выходом генератора тактовых ш спульсов, а третаЛ с единичным выходом триггера переполнения счетчика порядка, первый и второй выходы соединеш 1 с входами установки режима работы реверсивного счетчика порядка и мантиссы, третий выход соединен с первыми входами группы элементов И, вторые входы которых соед иены с соответствующими выходами блока фогмирования шага, а четвертый д пятый выходы первиго блока управления соединены соответственно с первым и вторым управляющими входами блока формирования шага, третий и четвертый управляющие входы которого соединены с выходами цепей переноса счетчика мантиссы и с соответствующими входами счетчика порядка, введены блок ци эовой задержки, блок суммирования, блок . выдачи кода и второй бпок упра.вления, вход которого соединен с выходом генератора тактовых импульсов, первый выход соединен с управляющим входом блока цифровой задержки и с первым управляющим входом блока суммирования, второй выход соединен с вторым управляющим входил блока суммирования, третий выход соединен с шиной Готовность, при этом 1ходы счетчика порядка и счеПчика мантиссы, кроме старшего разряда постоянного находящегося в единичном состоянии, соединены с соответствутошими входами блока цифровой задержки я с соответствующими входами первой группы входов блока суммирования, входы разрядов блока цифровой задержки соед1Ь- . нены с соответствующими входами второй группы входов блока суммирования, вььхо/и 1 разрядов блсжа суммирования соеш некы с соответствующими входами блока выдачи кода, управляющий вход которого соединен с шиной.Съем кода , а выходы - с выходной шиной. На фиг. 1 представлена функциональная схема следящего аналого-цифрового преобразсжателя; на фиг. 2 - один из вариантов реализации первого блока управле{ |1я; |ш фиг. 3 - вариант реализации блока формирования шага. Следяший аналого-цифровой преобразователь содержит блок 1 сравнения, циф ро-аналоговые преобразователи порядка 2 И мантиссы 3, источник 4 опорного напряжения, деш(|фратор 5, счетчики порядка 6 и мантисол 7, бл(Ж 8 формирования шага, первый блок 9 у1д)авления, генератор 10 тактовых импульсов, группа элементов И 11, второй бпок 12 управления, блок 13 цифровой задерхоси, блок 14 cyivn mpoвавия, блок 15 выдачи кода. Первый блок 9 управления (фиг. 2) содерткит триггер, который служит для запоминания ответа блока сравнения на предыдущем такте. Сигнал на первом выходе первого блока 9 управления появляются, если блок 1 сравнения выдает сигнал Vj( V ,в противном случае сигнал появляется на втором выходе. Если ответы блока 1 сравнения на предыдущем и в текущем такте совпадают, то появляется сигнал на четвертом вьтходе первого бпока 9 управления, в противном случае сиг нал появляется на пятом выходе. Блок 8 формирования шага (фиг. 3) включает распределитель импульсов и группу элементов И и ИЛИ. Выход nei вого элемента ИЛИ соединен с входе сдвига вправо на один разряд распределителя импульсов, а выход второго элеме та ИЛИ,- с выходом сдвига влево на один разряд распределителя импульсов. В распределителе импульсов запрещен сдвиг влево тфи коде 1О,..., О и сдвиг вправо при коде О,..., О1. Эта часть схе мы на фиг. 3 не показана. Блокцифровой 13 задержки (фиг. 1) может быть реализован на регистрах сдвига. Блок 14 суммирования (фиг. 1) может быть реализован на основе использования одного или нескольких обычных сумматоров. Очевидно, что число испол зуемых сумматоров определяет число одновременно получаемых значений корреля ционной .функшга при различных . киях задержки, так как при использовании нескольких сумматоров возможно сни мать задержанные значения сигнала с промежуточных регистров сдвига бпока цифровой задержки 13. Второй блок 12 управления (ф«г. 1) может быть реализован, на1фимер, на основе последовательно соединенных пякк задержки. Пример реализашш блока 15 выдачи кода приведен на фиг. 1., при этом пред полагается что блок 14 суммирования nocipoeH на основе одного суммйтора, в случае использования нескольких сум маторов надо либо использовать аналогичную схему для каждого сумматора, либо использовать коммутатор. Сущность работы блсжа выдачи кода заключается в следукяцем. Как указывалось, блсж 14 суммирования работает с кодами составленными из кодов содержащихся в счетчике 6 порядка и в счетчике 7 мантиссы, исключая старший разряд. Благодаря этскму исклю 9ению коды посгупаюшие в блок сум мирования являются приближенным значением логари4ма входного сигнала. Для перехода от логари4мического представления кодов к линейному из кодов соде{ жащихся в блоке суммирования выделяют часть кодов соответствующих мантиссе и приписывают к ней слева старшую (ранее исключенную) единицу, тем самым полу ают линейное представление кода в форе с плавающей запятой. Сущность предлагаемого изобретения аключается в том, что, кроме использоания способности преобразователя слеить за быстроизменяющимся сигналом, оявляется возможность использования пособности преобразователя выдавать риближенное значение логарифма входноо сигнала, которое позволяет заменить операшпо умножения операцией сложения, что 3 Ч1|:тельво облегчает использова- ание аналого-цифрового преобразешателя в устройствах измерения статических характеристик сигналов. Устройство работает следующим обре зом. Наряду с пзменеааем. величины шага квантования от одной кодовой.группы к другой, при изменении кода порядка, возможно изменение величины шага кван товашш на гфотяжении одной кодовой rpymw. При фиксированном коде порядка в зависимости от скорости изменения входного сигналу наряду с o6eciie4etmeM постоянной, относительной погрешности по величине сигнала, обеспечивается также постоянная относительная погрешность по скорости сигнала. По сигналу с первого выхода второго блока 12 управления (фиг. 1) содержимое счетчика 6 .порядка и счетчшса 7 мантиссы (исключая старший разряд) переписывается в блок 13 дафровой задержки и в блок 14 суммирования. По сигналу с второго выхода блока 12 у1фавле|шя производится сложение содержимого блока 14 суммирсжания с кодом снимаемым с выходом блока цифровой 13 задержки, после чего на третьем Ьадходе второго блока 12 управлетсг появляется сигюл о гото НОСТ8 устройс1«)а к выдаче кода. По свг налу Съем хойа устройство 15 выдачи кода выделяет из кода, содержащего в блоке 14 суммирования часть, соответст вующую мантиссе, и приписывает к ней слева старшую (ранее исключенную) ед . шшу, тем самым осуществляется переход от логарифмического представления кода к линейному представлению кода в форме с пшвающей запятой. Так1А образом, благодаря вводу в соатав следящего аналого-цифрового предах зователя блока цифровой задержку, блока суммщ ования, устройства выдачи кода н второго блока управления, кроме использования способности следующего авалсягоЦИФР1ЖОГО преобразователя следить за быстроменяющимися сигналами, появляет-. ся возможность использования способности преобразователя выдавать приближет ное значение логарифма входного сигнала, котор1ая позволяет заменить операцию умножения операций сложения, что знач тельно раснпфяет область применения пр& образователя, например, появляется воэMcwcHocTb использсдаашга его в устройствах определения статических характеристик сигналов, в частности, корреляиконной функции и дисперсии. Формула изобретения Следяишй аналого-цифровой преобразователь по авт, св. N9 8284О1, отличающийся тем, что, с целью расширения функциональных возможностей введены блок цифровой задержки, блок суммирования, блок выдачи кода и второй блок управлений, вход которого соединен с выходом генератора тактовых импупьсов первый выход соединен с управляющим входом блока задержки и с первым управляющим входом блока сумкгарования, второй выход соединен с вто9so рым управляющим входом блока суммирования,, третий выход соединен с шиной Готовность, при этом выходы счетчика порядка и счетчика мантиссы, кроме старншего разряда, постоянно находящегося в единичном состоянии, соединены с соответствующими входами блока цифровой задержки и с соответствующими входами первой группы входов блока суммирования, выходы разрядов блока ци }чровой задержки соединены с соответствующими входами втсфой группы входов блока суммирования, выходь разрядов блока суммирования соединены с соответствующими входами блока выдачи кода, управляющий вход которого соединен с шиной Съем кода , а выходы - с выходной шиной. Источники информации. принятые во внимание при экспертизе 1. Авторское свидетельство СССР 8284О1, кл. Н ОЗ К 13/О2, 4.О6.80.

Wi

L tf

l

Ю

il .1 1

4

fy

Фиг.1

фиг.2

I I

Авторы

Даты

1982-05-23—Публикация

1980-06-04—Подача