Изобретение относится к вычислительной технике н оискретной автоматике и может быть использовано при построении цифровой аппаратуры повышенной надежнос ти. Известен резервируемый совигаюишй регистр, содержащий реэерв;ируемые ре, гистры, элементы И, элементы ИЛИ, выхоаы которых подключены к первым входам вторых элементов ИЛИ, цополнитель ные элементы И и аналИ:заторы, входы ко торых подключены к выходам контрольных триггеров реэервируемьк регистров, а прямой выход - к входам первых допотите ных элементов И, вторые входы соединены с выходами оснсаных и резерв ных разряде резервируемых регистре, а выход - со вторыми входами вторых элементе ИЛИ, при этом инверсный выход анализатора подключен к вторым входам первых элементов Ник входам вторых дополнительных элементов И, выходы которых подключены к входам первых элементов . Недостатком устройства 5ШЛ51ется го,, что для его построения требуются инте1 ральные схемы, имеющие большое количество внешних выводов. Натфимер, для реализации яетырехг разрядного сдвигающего регистра требуются интегральные схемы, имеющие не менее 19 внешних выводов. Наиболее бжзким техническим решением к предлагаемому изофетению является регистр сдвига, содержащий N разряде, выполненных на статических триггерах, выходные элементы И по числу разрядсе, цепи входной и У1фавл$пощей сдвигом информации, счетчик с И1ипульсами, Генератор заторможенных импульсов, два элемента И, элемент НЕ, ячейки памяти, геервые выходы которых подсоединены к вьрсодам регистра сдвига, первую группу элементов И, по числу ячеек памяти, одни из входов которых соединены со вторыми выходами соответствующих ячеек памяти, генератор тестовых сигнале.

первый и второй элементы И, первый элемент НЕ и тактовую шину ЗНедостаток устройство - его сложность Цель изобретения - упрощение регистра за счет уменьшения числа внешних вьшоцов.

Поставленная цель достигается тем, что регистр сдвига содержит дешифратор, первый и второй элементы НЕ, вторую группу элементов И, элементы И-НЕ,

третью и четвертую группы элементов И, причем входы дешифратора соединены с первым и вторым выходами генератора тестовых сигналов, третий выход которого подключен к первым входам первого и

второго элементов И, вторые входы которых соединены соответственно с первым и вторым выходами аеши4ратора, выход первого элемента И соединен с первыми входами первого и второго элементов ИЛИ вторые входы которых соединены соответственно со вторым и третьим выходами цещифратора, третий вход второго элемента ИЛИ подключен к выходу второго элемента И, первый и четвертый выходы де- шифратора и выходы элементов ИЛИ сое- цинены с первыми входами элементов И второй и третьей группы и с первыми входами элементов И-НЕ, вторые входы элементов И второй группы соединены с выходом первого элемента НЕ, вход которого подключен к четвертому выходу Генератора тестовых сигнале и вторым входам элементов И-НЕ, выходы элементов И второй группы соединены с первы- ми вхооами элементов И четвертой группь, вторью входы которых подключены к выхооу второго элемента НЕ, вход которого соеаинен со вторыми входами элементов И третьей группы и с пятым выходом генератора тестовых сигналов, первые входы ячеек памяти соединены с тактовой шиной, выходы элементов И третьей и четвертой групп подключены соответственно к вторым и третьим входам соответст- вующих ячеек памяти, выход каждого элемента И, кроме последнего,, первой груп:пы соединен с четверть1м входом последующей ячейки памяти, выход последнего элемента И первой группы соединен с четвертым входом первой ячейки памяти.

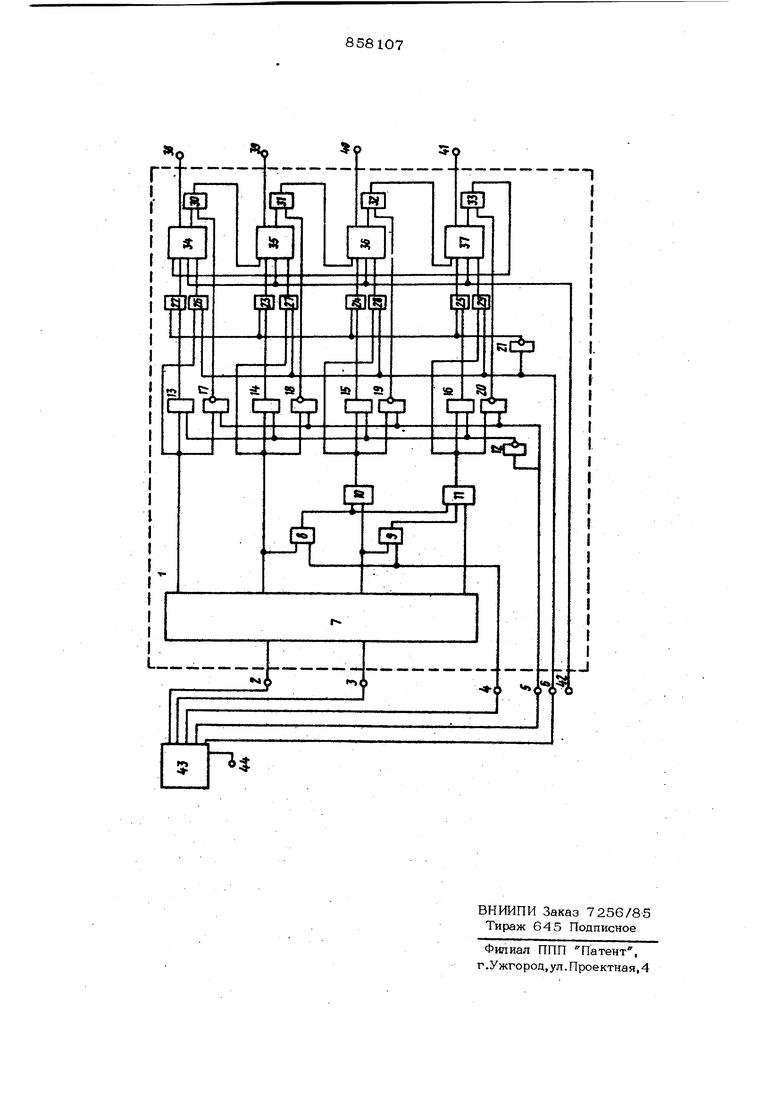

На чертеже представлена ) структурная схема регистра сдвига.

Регистр .сдвига содержит сдвигающие регистры 1 (в виде отдельной интегральной схемы), внешние выводы 2-6 интегралной схемы, дешифратор 7, первыйи второ элементы И 8 и 9, первый и второй элэменты ИЛИ 10 и 11, первый элемент НЕ 12, вторую группу элементов И 13-16, элементы И-НЕ 17-20, второй элемент НЕ 2 1 четвертую группу элементов И 22-25, третью группу элементов И 26-2 элементы И 28 и 29, первую группу элементов И ЗО-ЗЗ, ячейки 34-37 памяти, внешние вьюоды 38-41 интегральной схемы, тактовую шину 42, генератор 43 тестовых сигналов и шину 44 входной информации.

- Каждый из сдвигающих регистров соответствует одному разряду регистра сдвигз Для сдвигающего регистра, соответствующего старшему четвертому разряду, ячейка 34 5шляется основной (рабочей), а ячейки 35-37 - контрольными. Для сдвигающего регистра, соответствующего третьему разряду, ячейка 34 является основной, ячейка 35 является резервной, а ячейки 36,37 - контрольными. Для сдвигающего , соответствующего второму разряду, ячейка 34 является основной, ячейки 35,36 являются резервными, а ячейка 37 - контрольной. Для сдвигающего регистра, соответствующего первому разряду, ячейка 34 является основной, а ячейки 35-37 - резервными. Вьгооды2-6 подключены к первому, второму, третьему, четвертому и пятому выходу 43 генератора тестовых сигналов, первью входы элементов И 8 и 9 подключены к входному выводу 4, вторые выходы элементов И 8 и 9 подключены к первому и второму выходу дешифратора 7, при этом выход элемента И 8 подключен к первым входам элементов ИЛИ 10 и 1 вторью входы которых подключены соответственно ко второму и третьему выходу дешифратора 7, а выход элемента И 9 подключен к третьему входу элемента ИЛИ 11, Входной вывод 5 подключен ко входу элемента НЕ 12 и ко вторым входам элементов И-НЕ 17-2О, а выход элемента НЕ 12 соединен со вторыми входами элементов И 13-16. Входной вьюод 6 подключен ко входу элемента НЕ 21 и ко вторым входам элементов И 26-29, при этом выход элемента НЕ 21 соедишн со вторыми входами элементов И 2225. Тактовая шина 42 подключена к первым входам ячеек 34-37 памяти. Четвертый выход дешифратора 7 подключен к первым входам элементов И 13 и 26 и к первому входу элемента И-НЕ 17, первый выход дешифратора 7 подключен также к первым входам элементов И 14 и 27, а также к первому входу элемента И-НР

18,выход элемента ИЛИ 1О подключен к первым входам элементов И 15 и 28, а также к первому входу элемента И-НЕ

19,выход элемента ИЛИ 11 подключен

к первым входам элементов И 16 и 29, а также к первому входу элемента И-НЕ

20,причем выходы элементов И 13-16 подключены соответственно к первым входам элементов И 22-25, а выходы элементов И-НЕ 17-2О поцключены соогвет венно к одним из входов элементов И 3033, другие входы которых подключены соответственно к выходам ячеек 34-37 памяти. Выходы элементов И 22-25 подключены к третьим входам, а выходы эле ментов И 26-29 подключены ко вторым входам ячеек 34-37 памяти, при этом

Выходы элементов И ЗО-33 подключены соответственно к четвертым входам ячеек 34-37 памяти.

Регистр сдвига работает следующим офазом.

Входная информация поступает независимо в каждый из сдвигающих регистров. С этой целью на внешние выводы 2-6 сдвигающих регистров с выходов генератора 43 тестовых сигналов подаются слэдуюшне сигналы : для сдвигающего регистра, с которого снимается старший 4-й разряд, на выводы 2,4,5,6 подается О, На вывод 3 подается I, для CGJBHгаюшего регистра, с которого снимается 3-й разряд,на выводы 3-6 подается О , на вывод 2 подается 1,для сдвигающего регистра, с которого снимается 2-и разряд, на выводы 4-6 подается О, на выводы 2,3 подается . Указанные сигналы подаются на внешние выводы сдвигающих регистров тогда, когда через шину 44 входной информации поступают импульсы, пошюжащие записи в регистр сдвига.

Для разрыва цепи сдвига от старшего к младшему разряду сдвигающих регистро на выводы 2-6 с выходов генератс эа 43 подаются следующие сигналы: для сдвигающего регистра, с которого снимается старший 4 и разряд, на выводы 2,4,6 подается О, на выводы 3,5 подается 1 для сдвигающего регистра, с которого снимается 3-й разряд, на выводы 3,4,6 подается О , на выводы 2,5 подается 1, для сдвигающего регистра, с которого снимается разряд, на выводы 4,6 подается О, на выводы 2,3,5 подается I.

В режиме контроля на выводы 2-6 сдвигающих регистров с выходов генератора 43 подаются с/коующие сигналы : для сдвигающего регистра, с которого снимае ся старший 4-й разряд, на выводы 2,6 подается О, на выводы 3-5 подается для сдвигающего регистра, с которого снимается 3-Л разряд, на выводы 3,6 подается О, на выводы 2,4,5 подается I для сдвигающего регистра, с которого снимается 2-й разряд, на вывод 6 подается О, на выводы 2-5 подается .

В режиме ксщтроля, с целью установки контро/ьных ячеек сдвигающих регистров О , на выводы 2-6 сдвигающих регистров с выходов генератора 43 подаются следующие сигналы: для сдвигающего регистра, с которого снимается 4-и старший разряд, на выводы 2,5 подается О на выводы 3,4,6 подается I, для сдвигающего регистра, с которого снимается 3-й разряд, на выводы 3,5 подается О, на выводы 2,4,6 подается , для сдвигающего регистра, с которого снимается 2-й разряд, на вывод 5 подается О, на выводы 2,3,4,6 подается .

В режиме кстстроля, с це/ью установки контрольных ячеек сдвигающих регистров в на выводы 2-6 сдвигакяцих регистров с выходов генератора 43 подаются следующие сигналы: для сшигающего регистра, с которого снимается 4-й старший разряд, на выводы 2,5,6 подается О, на вывощы 3,4 подается I, для сдвигающего регистра, с которого снимается 3-и разряд, на выводы 3,5,6 подается О, на выводы ,4 подается 1, для сдвигающего регистра, с которого снимается 2-и разряд, на выводы 5,6 подается О, на выводы 2-4 подается 1.

В режиме ксжтроля с помощью такой последовате/ьности импульсов реализуются переходы контрольных ячеек из состояния ноль в состояние единица и из состояния единица в состояние ноль. Предлагаемый резервированный регистр сохраняет работоспособность при отказах ложный ноль и ложная единица .

Технико-эк«1 омический эффект изобретения состоит в том, что с помошью введения в сдвигающие регистры дешифратора и дополнительных элементов И,ИЛИ, И-НЕ, НЕ число внешних выводов этих регистре в интегральном исполнении сократится. В рлучае N - разрядного регистра без дешифратора и дополнительных э/ементов И, ИЛИ, И-НЕ, НЕ необходимое число внешних выводов каждого сдвигающего регистра равно 4N + 4 а в слу-

чае, когда в сдвигающие регистры в интегральном исполнении вводятся деши(|ратор и дополнительные элементы И, И-НЕ, ИЛИ, НЕ, число внешних выводов каждого сдвигающего регистра равно Н+&ол.М+7.

Например, для реализации 16-раарядного сдвигающего регистра с дешифратором и дополнительными элементами потребуются микросхеМЫ, имеющие в 2,5 раза меньше внещних выродов, чем-у микросхем, требуемых для построения сдвигающего регистра без дешифратора и дополнительИых элементов, а при реализации 32 -разрядного регистра потребуются микросхемы имеющие в 3 раза меньше внешних вывоДОВ.

Меньшее количество внешних выводов сдвигающих регистров упрощает схему регистра сдвига и тем самым увеличивает его надежность.

Формула изобретения

Регистр сдвига, содержащий ячейки памяти, первые входы которых подсоединены к выходам регистра сдвига, первую группу элементов И по числу ячеек , одни из входш которых соединены со вторыми выходами соответствующих ячеек памяти, генератор тестовых сигналов, первый и второй элементы И, первы элемент НЕ и тактовую шину, отличающийся тем, что, с целью упрощения регистра сдвига за счетуменьщения числа внешних выводе, в него введены цеши(|рагор, первый и второй элементы ИЛИ, второй элемент НЕ, вторая группа элементов И, элементы И-НЕ, третья и четвертая группа элементов И, причем входы дешифратора соединены с первым и вторым выходами Генератора тестовых сигналов, третий выход которого подключен к первым входам первого и второго

элементов И, вторые входы которых соединены соответственно.- с первым и вторык выходами дешифратора, выход первого элемента И соединен с первыми входами первого и второго элементов ИЛИ, вторые входы которых соединены соответствено со вторым и третьим выходами дешифратора, третий вход втфого элемента ИЛИ подключен к выходу второго элемента И, первый и четвертый выходы дешифратора и выходы элементов ИЛИ соединены с первыми входами элементов И второй и третьей групп и с первыми входами элементов И-НЕ, вторые входы элементов И второй группы соединены с вькодом первого элемента НЕ, вход которого подключен к четвертому выходу генератора тестовых сигналов и втсрым входам элементов И-НЕ, выходы элементов И второй группы соединены с первыми входами элементов И четвертой группы, вторые входы которых подключены к выходу второго элемента НЕ, вход которого соединен со вторыми входами элементов И третьей группы и с Пятым выходом Генератора тестовых сигналов, первые входы ячеек памяти соединены с тактсюой шиной, выходы элементов И третьей и четвертой групп подключены соответственно ко вторым и третьим входам соответствующих ячеек памяти, выход каждого элемента И, кроме последнего, первой группы соединен с четвертым входом последующей ячейки памяти, выход последнего элемента И первой группы соединен с четвертым входом первой ячейки памяти.

Источники информации, принятью во внимание при экспертизе :

1.Авторское свидетельство СССР по заявке N 2647402, кл. Q 11 С 19/ОО, 1978.

2.Авторское свидетельство СССР по заявке N 2.7ОО914/24, кл. Q 11С 19/ОО 1978 (прототип).., Эр

Sio

Ж

o

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для проверки электрического монтажа | 1986 |

|

SU1336035A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Информационное устройство | 1987 |

|

SU1564066A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Устройство для вывода информации | 1991 |

|

SU1833857A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЧАСТОТНЫХ ХАРАКТЕРИСТИК ЗВЕНЬЕВ ДИНАМИЧЕСКИХ СИСТЕМ | 1990 |

|

RU2068576C1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

Авторы

Даты

1981-08-23—Публикация

1979-07-26—Подача