1

Изобретение относится к автоматике, телемеханике и вычислительной технике и может быть использовано, в частности в преобразователях аналоговых сиг- j налов в цифровой код.

Известно устройство управления преобразователем, содержащее триггер запуска, формирователь задержанных импульсов, элементы И,. И-НЕ , схему JQ стробирования выходного сигнала элемента сравнения, регистр, каждый разряд которого содержит управляющий элемент И-НЕ и два триггера, состоящие из одного элемента И-ИЛИ-НЕ с входами триггерной связи и установки, Э элемента И-НЕ для первого триггера и элемента НЕ для второго триггера, шину тактируь-вдих импульсов и шину начальной установки l.

Недостатком данной схемы является низкая надежность и малое быстродействие преобразования.

Цель изобретения - повышение надежности и увеличение Сыстродействия при сохранении точности преобразования.

Поставленная цель достигается тем, что в известном устройстве управления преобразователем аналог-код последовательного прибли;хения, содержапее 30

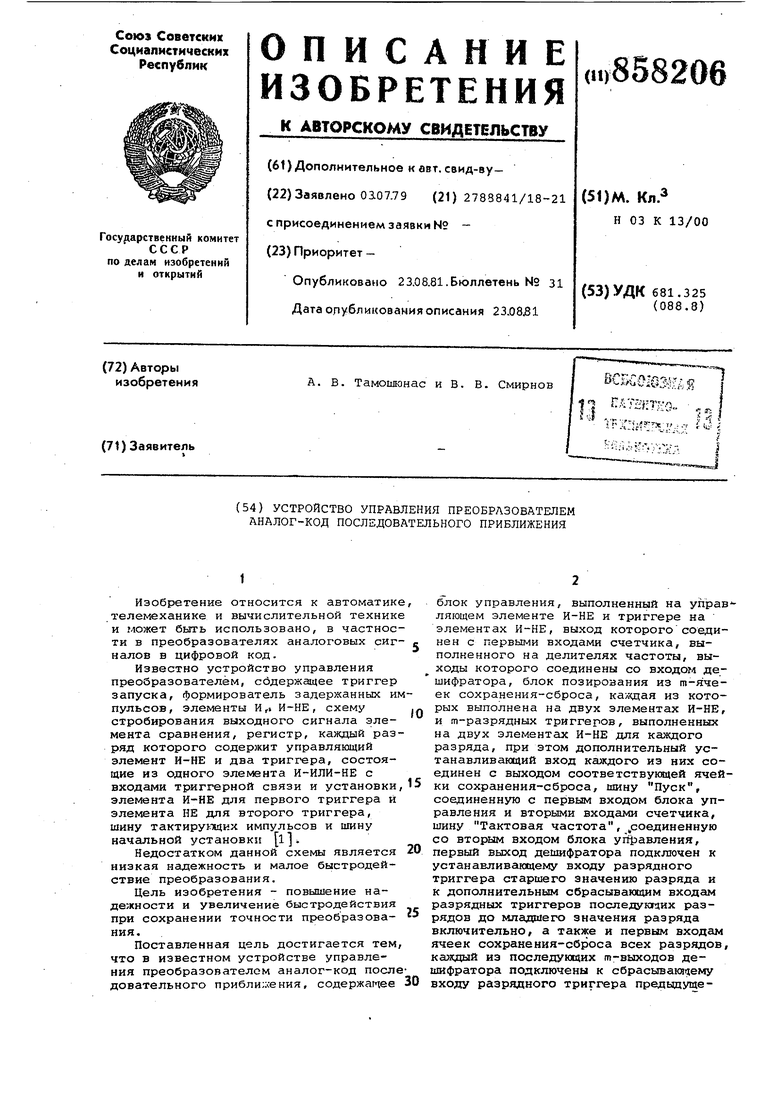

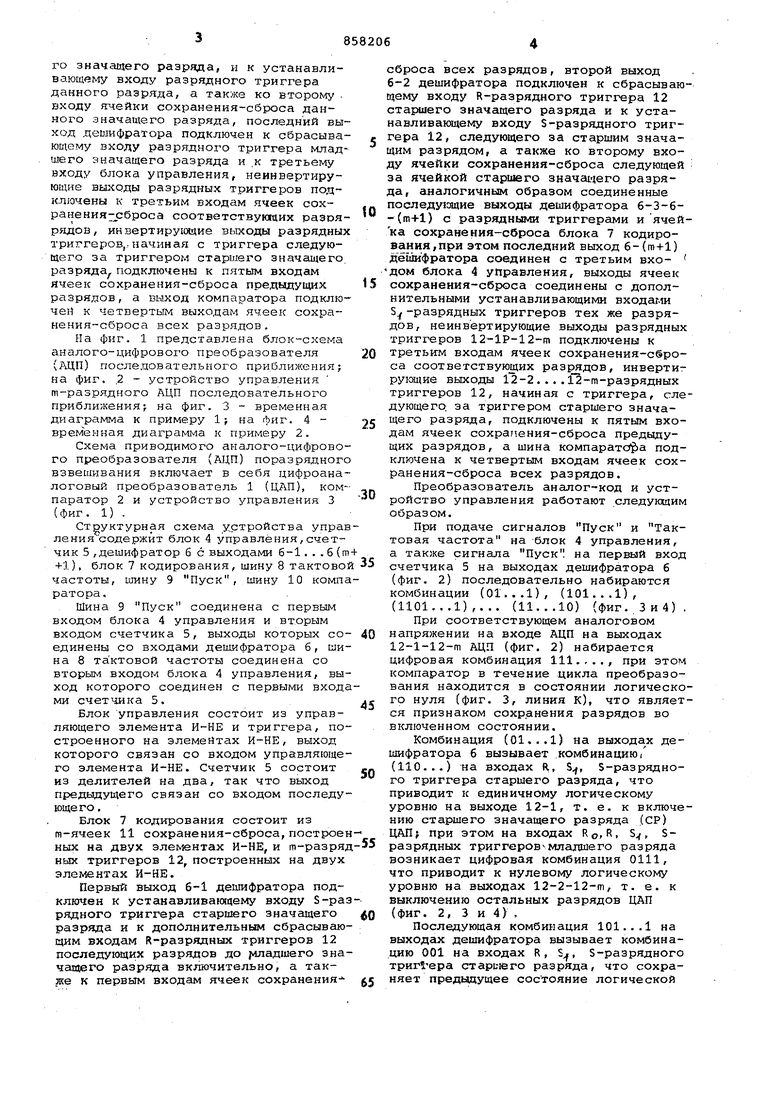

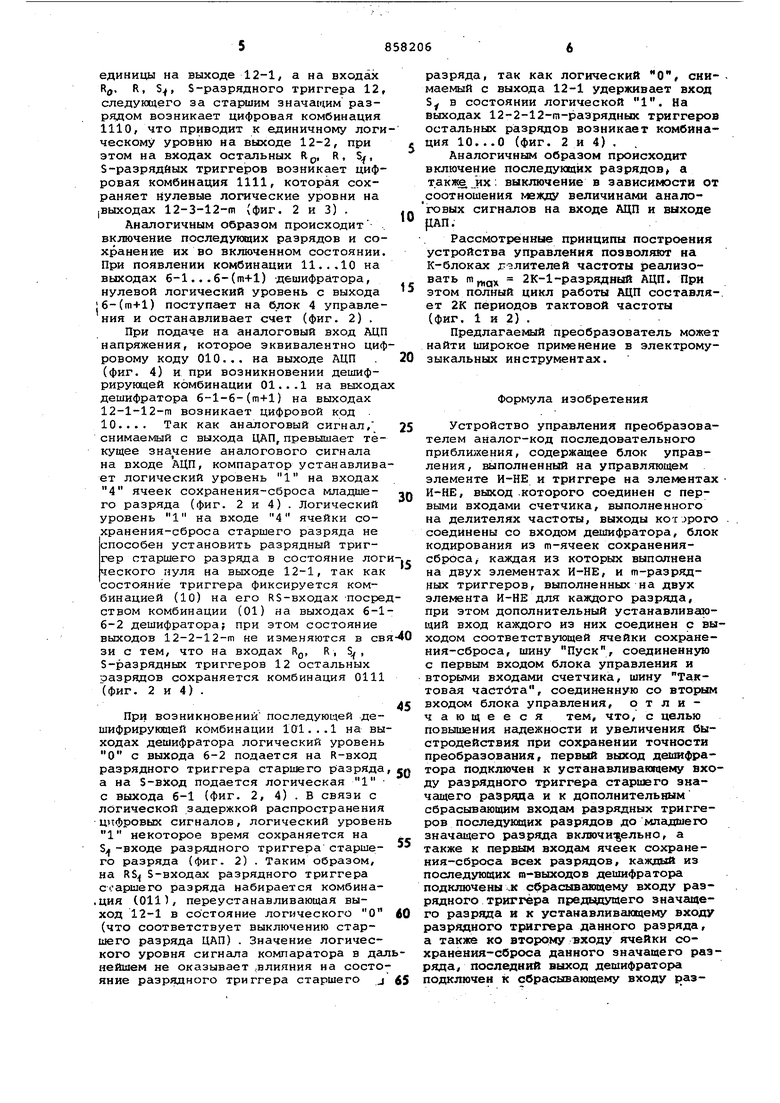

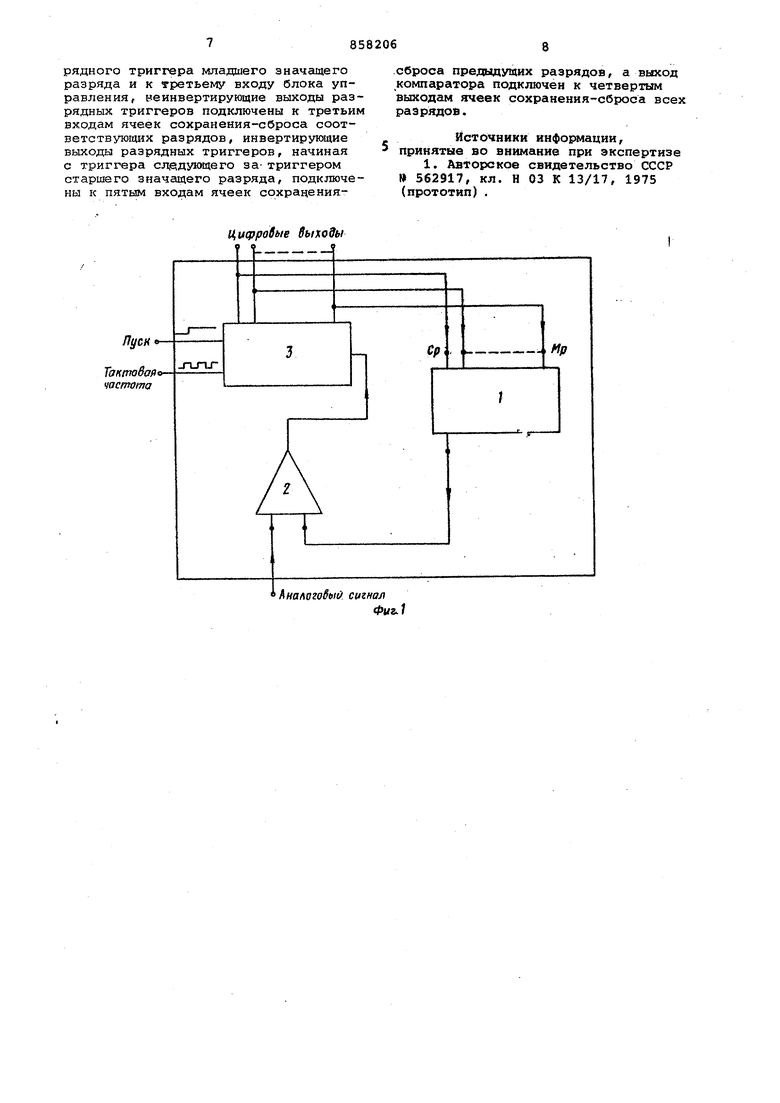

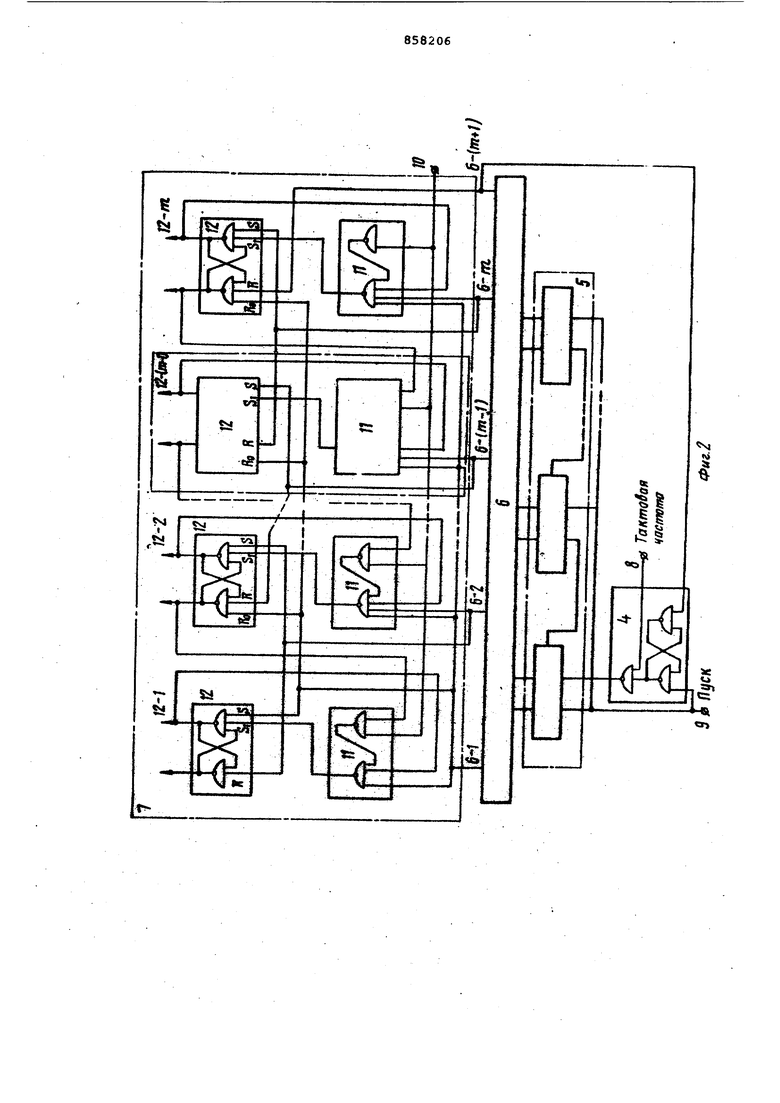

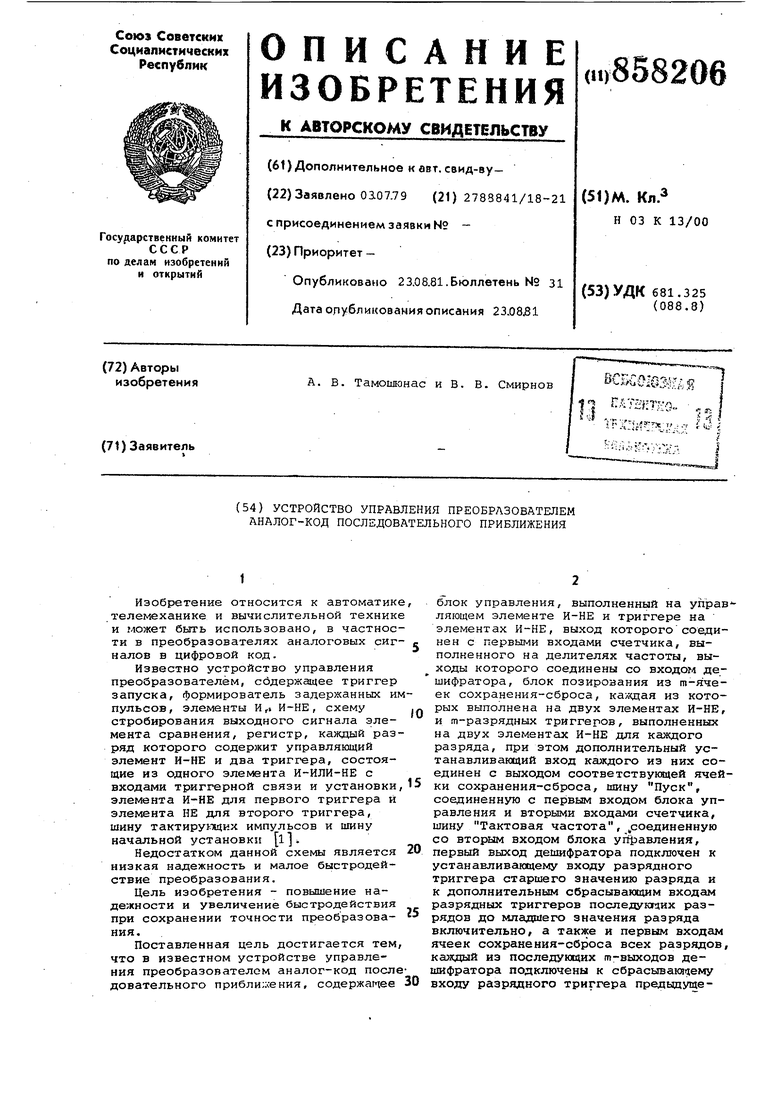

блок управления, выполненный на управ-ляющем элементе И-НЕ и триггере на элементах И-НЕ, выход которого соединен с первыми входами счетчика, выполненного на делителях частоты, выходы которого соединены со входом дешифратора, блок позирования из т-ячеек сохранения-сброса, из которых выполнена на двух элементах И-НЕ, и т-разрядных триггеров, выполненных на двух элементах И-НЕ для каждого разряда, при этом дополнительный устанавливающий вход каждого из них соединен с выходом соответствующей ячейки сохранения-сброса, шину Пуск, соединенную с первым входом блока управления и вторыми входами счетчика, шину Тактовая частота, .соединенную со вторым входом блока уйЬавлення, первый выход дешифратора подк.гаочен к устанавливающему входу разрядного триггера старшего значению разряда и к дополнительным сбрасывающим входам разрядных триггеров последуюгчих разрядов до младшего значения разряда включительно, а также и первым входам ячеек сохранения-сброса всех разрядов, из последующих т-выходов дешифратора подключены к сбрасывакядему входу разр}щного триггера предыдущего значащего разряда, и к устанавливающему входу разрядного триггера данного разряда, а также ко второму . входу ячейки сохранения-сброса данного значащего разряда, последний выход дешифратора подключен к сбрасывающему входу разрядного триггера младшего значащего разряда и .к третьему входу блока управления, неинвертирующие выходы разрядных триггеров подключены к третьим входам ячеек сохранения7,сброса соответствунхцих разояр щов, инвертирующие выходы разрядных триггеров,, начиная с триггера следующего за триггером старшего значащего разряда, подключены к пятым входам ячеек сохранения-сброса предыдущих разрядов, а выход компаратора подключен к Четвертым выходам ячеек сохранения-сброса всех разрядов. На фиг. 1 представлена блок-схема аналого-цифрового преобразователя (АЦП) последовательного приближения; на фиг. .2 устройство управления т-разрядного АЦП последовательного приближения; на фиг. 3 - временная диаграмма к примеру 1 на фиг. 4 временная диаграмма к примеру 2. Схема приводимого аналого-цифрово го преобразователя (АЦП) поразрядного взвешивания включает в себя цифроана логовый преобразователь 1 (ЦАП), ком паратор 2 и устройство управления 3 (фиг. 1) . Структурная схема устройства упра ления содержит блок 4 управления,счетчик 5 , дешифратор 6 с выходами 6-1. . . 6 (ш +1), блок 7 кодирования, шину 8 тактово частоты, ишну 9 Пуск, шину 10 комп ратора. Шина 9 Пуск соединена с первым входом блока 4 управления и вторым входом счетчика 5, выходы которых со единены со входами дешифратора б, ши на 8 тактовой частоты соединена со вторым входом блока 4 управления, вы ход которого соединен с первыми вход ми счетчика 5, Блок управления состоит из управляющего элемента И-НЕ и триггера, по строенного на элементах И-НЕ, выход которого связан со входом управляюще го элемента И-НЕ. Счетчик 5 состоит из делителей на два, так что выход предыдущего связан со входом последу ющего , Блок 7 кодирования состоит из га-ячеек 11 сохранения-сброса, построе ных на двух элe юнтax И-НЕ, и т-разря ных триггеров 12, построенных на двух элементах И-НЕ. Первый выход 6-1 дешифратора подключен к устанавливакхцему входу S-ра рядного триггера старшего значащего разряда и к дополнительным сбрасываю щим входам R-разрядных триггеров 12 последующих разрядов до улладшего зна чащего разряда включительно, а также к первым входам ячеек сохранения- броса всех разрядов, второй выход -2 дешифратора подключен к сбрасываюему входу R-разрядного триггера 12 таршего значащего разряда и к устаавливающему входу S-разрядного тригера 12, следующего за старшим значаим разрядом, а также ко второму вхоу ячейки сохранения-сброса следующей а ячейкой старшего значащего разряа, аналогичным образом соединенные последу эдие выходы дешифратора 6-3-6(т+1) с разрядными триггерами и ячейка сохранения-сброса блока 7 кодирования,при этом последний выход 6-{m+l) дЪшифратора соединен с третьим вхоДОМ блока 4 управления, выходы ячеек сохранения-сброса соединены с дополнительными устанавливающими входами S -разрядных триггеров тех же разрядов, неинвертирующие выходы разрядных триггеров 12-lP-12-m подключены к третьи-м входам ячеек сохранения-сброса соответствующих разрядов, инвертирующие выходы l2-2. .. .12-т-разрядных триггеров 12, начиная с триггера, следующего за триггером старшего значащего разряда, подключены к пятым входам ячеек сохранения-сброса предыдущих разрядов, а шина компаратора подключена к четвертым входам ячеек сохранения-сброса всех разрядов. Преобразователь аналог-код и устройство управления работают следующим образом. При подаче сигналов Пуск и Тактовая частота на блок 4 управления, а также сигнала Пуск, на первый вход счетчика 5 на выходах дешифратора 6 (фиг. 2) последовательно набираются комбинации (01...1), (101... 1), (1101...),... (11...10) (фиг. Зи4). При соответствующем аналоговом напряжении на входе АЦП на выходах 12-1-12-т АЦП (фиг. 2) набирается цифровая комбинация 111.,.., при этом компаратор в течение цикла преобразования находится в состоянии логического нуля (фиг. 3, линкя к), что является признаком сохранения разрядов во включенном состоянии. Комбинация (01... 1) на выхода х дешифратора 6 вызывает .комбинацию/ (110...) на входах R, S, S-разрядного триггера старшего разряда, что приводит к единичному логическому уровню на выходе 12-1, т. е. к включению старшего значащего разряда (СР) ЦАП; при этом на входах RO, R, S, Sразрядных триггеров-младшего разряда возникает цифровая комбинация 0111, что приводит к нулевому логическому уровню на выходах 12-2-12-т, т. е. к выключению остальных разрядов ЦАП (фиг. 2, 3 и 4 , Последующая комбинация 101...1 на выходах дешифратора вызывает комбинацию 001 на входах R, S, S-разрядного триггера старцйго разряда, что сохраняет предыдущее состояние логической единицы на выходе 12-1, а на входах RO R. S, S-разрядного триггера 12, следующего за старшим значащим разрядом возникает цифровая комбинация 1110, что приводит к единичному логи ческому уровню на выходе 12-2, при этом на входах остальных Rp, R, S, S-разрядйых триггеров возникает цифровая комбинация 1111, которая сохраняет нулевые логические уровни на |выходах 12-3-12-01 (фиг. 2 и 3) , Аналогичным образом происходит включение последующих разрядов и сохранение их во включенном состоянии. При появлении комбинации 11.,.10 на выходах 6-1...б-(т+1) -дешифратора, нулевой логический уровень с выхода :6-(т+1) поступает на блок 4 управления и останавливает счет (фиг, 2) . При подаче на аналоговый вход АЦП напряжения, которое эквивалентно циф ровому коду 010,., на выходе АЦП . (фиг, 4) и при возникновении дешифрирующей комбинации 01,, . 1 на выхода дешифратора 6-1-6-(т+1) на выходах 12-1-12-т возникает цифровой код . 10.,,, Так как аналоговый сигнал/ снимаемый с выхода ЦАП, превышает текущее значение аналогового сигнала на входе АЦП, компаратор устанавлива ет логический уровень 1 на входах 4 ячеек сохранения-сброса младшего разряда (фиг, 2 и 4) . Логический уровень 1 на входе 4 ячейки сохранения-сброса старшего разряда не способен установить разрядный триггер старшего разряда в состояние лог ческого нуля на выходе 12-1, так как состояние триггера фиксируется комбинацией (10) на его RS-входах -посре ством комбинации (01) на выходах 6-1 6-2 дешифратора; при этом состояние выходов 12-2-12-т не изменяются в св зи с тем, что на входах Rg, R, S , S-разрядньк триггеров 12 остальных разрядов сохраняется комбинация 0111 (фиг. 2 и 4) . При возникновений последующей дешифрирующей комбинации 101,,, на вы ходах дешифратора логический уровень О с выхода 6-2 подается на R-вход разрядного триггера старшего р азряда а на S-вход подается логическая 1 с выхода 6-1 (фиг, 2, 4) . В связи с логической задержкой распространения цифровых сигналов, логический уровен 1 некоторое время сохраняется на S;f -входе разрядного триггера старшего разряда (фиг. 2) . Таким образом, на RS S-входах разрядного триггера соаршего разряда набирается комбина.ция (011), переустанавливающая выход 12-1 в состояние логического О (что соответствует выключению старшего разряда ЦАП) . Значение логического уровня сигнала компаратора в дал нейшем не оказывает .;влияния на состояние разрядного триггера старшего j разряда, так как логический О, снимаемый с выхода 12-1 удерживает вход S. в состоянии логической 1. На выходах 12-2-12-т-разрядных триггеров остальных разрядов возникает комбинация 10...0 (фиг. 2 и 4) , Аналогичным образом происходит включение последующих разрядов а также, их: выключение в эaБиcи 4Ocти от соотношения между величинами аналоговых сигналов на входе АЦП и выходе ЦАП. Рассмотренные принципы построения устройства управления позволяют иа К-блоках 1:элителей частоты реализовать 2К-1-разрядный АЦП. При этом полный цикл работы АЦП составляет 2К периодов тактовой частоты (фиг. 1 и 2) , Предлагаемый преобразователь может найти широкое применение в электромузыкальных инструментах. Формула изобретения Устройство управления преобразователем аналог-код последовательного приближения, содержащее блок управления, выполненный на управляющем элементе И-НЕ и триггере на элементах И-НЕ, выход .которого соединен с первыми входами счетчика, выполненного на делителях частоты, выходы котзрого соединены со входом дешифратора, блок кодирования из т-ячеек сохранениясброса/ каждая из которых выполнена на двух элементах И-НЕ, и т-разрядftbtx триггеров, выполненных на двух элемента И-НЕ для каждого разряда, при этом дополнительный устанавливающий вход каждого из них соединен с выходом соответствующей ячейки сохранения-сброса, шину Пуск, соединенную с первым входом блока управления и вторыми входами счетчика, шину Тактовая частбта, соединенную со BTOI«M входом блока управления, отличающееся тем, что, с целью повышения надежности и увеличения быстродействия при сохранении точиости преобразования, первый выход дешифратора подключен к устанавливающему входу разрядного триггера старшего значащего разряда и к дополнительным сбрасывающим входам разрядных триггеров последующих разрядов до младшего значащего разряда включи ельно, а также к первым входам ячеек сохранения-сброса всех разрядов, каждый из последующих т-выходов дешифратора подключены .к сбрасывающему входу разрядного триггера предьвдущего значащего разряда и к устанавливающему входу разрядного триггера данного разряда, а также ко второму входу ячейки сохранения-сброса данного значащего разряда, последний выход дешифратора подключен к сбрасывающему входу разрядного триггера младшего значащего разряда и к третьему входу блока управления, веинвертирунлцие выходы разрядных триггеров подключены к третьим входам ячеек сохранения-сброса соответствующих разрядов, инвертирукядие выходы разрядных триггеров, начиная с триггера сладующего за- триггером старшего значащего разряда, подключены к пятьам входам ячеек сохраценияЦисрровые выходы

Такгповойо частота

Лналоговый сигнал

.сброса предыдущих разрядов, а выход компаратора подключен к четвертым выходам ячеек сохранения-сброса всех разрядов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 562917, кл. Н 03 К 13/17, 1975 (прототип) ,

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Устройство для программного управления технологическим оборудованием | 1985 |

|

SU1325407A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Устройство для измерения погрешности аналого-цифрового преобразователя | 1982 |

|

SU1115219A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1522400A1 |

| Вероятностный преобразователь аналог-код | 1984 |

|

SU1236608A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕВИЗИОННЫХ СИГНАЛОВ | 1991 |

|

RU2014745C1 |

| Многоканальное устройство для регистрации сигналов | 1988 |

|

SU1560980A1 |

| Устройство для регистрации аналогового процесса | 1986 |

|

SU1429171A1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ И ДЕМУЛЬТИПЛЕКСИРОВАНИЯ КОМПОНЕНТНЫХ СИГНАЛОВ В ЦИФРОВЫХ ПОТОКАХ | 2012 |

|

RU2514092C2 |

Авторы

Даты

1981-08-23—Публикация

1979-07-03—Подача