1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в области автоматизации проектирования электронных схем.

Наиболее близким по технической сущности к предлагаемому является устройство для синтеза электронных схем, содержащее последовательно соединенные модель исходной схемы,блок измерения показателя качества, блок анализа показателя качества, блок выбора направления поиска и блок организации приращений, последовательно соединенные блок проверки экстремума и измеритель экстремума и последовательно соединенные блок управления и блок проверки ограничений,выход которого соединен со вторым входом блока анализа показателя качества, подключенного вторым выходом ко входу блока проверки экстремума, первым выходом - к второму входу измерителя экстремума, а третьим выходом - ко второму входу блока проверки ограничений, второй выход блока проверки экстремума соединен с первым входом блока управления, второй выход блока измерения показателя качества

соединен с первым входом модели исходной схемы l.

Однако известное устройство не может быть применено для решения Зсщачи структурного синтеза электронных схем, так ак данная задача требует совершенно иной постановки и, следовательно, другой технической реализад;ии. .

10

Постановка задачи в этом случае сводится к следукядему. Имеется упранляемая модель электронной схемы с заданным набором входных параметров, выполняющая определенную логическую 15 функцию. Необходимо получить модель схемы, выполняющую ту же логическую функцию, но с улучшенными относительно некоторых критериев (технических требований) выходными характеристи20ками.

Для решения поставленной задачи необходимо ввести понятие дискретной вычислительной среды (ДВС), которая Представляет собой совокупность то25чек, к каждой из которых подключены токоограничивающий резистор и источник питания. Если между данными точками включить выводы компонентов схемы, то получится управляемая модель исходной электрической схемы.

работа которой может быт{э описана системой Мдифференциальных уравнений, составленных по методу узловых потенциалов. Здесь М - число внутренни уэлор схзмы, т.е. узлов, не подключенных к источнику питания. Основываясь на понятии ЛВС, можно сделать вывод, что для заземленного узла схе1.И значения токоограничиваквдего ре- зистора и источника питания равны нулю. Для узла схемы, не подключенного к источнику питания, значение резистора стремится к бесконечности.

В этом пространстве узлов необходимо предусмотреть возможность расширения модели исходной схемы путем подключения между ее внутренними узлами резистивно-полупроводниковой структуры, имеющей N выводов, а также возможность вращения резистивнополупроводниковой структуры в пространстве внутренних узлов. Тогда задача параметрической оптимизации становится лишь частной задачей структурного синтеза.

Цель изобретения - расхаирение функциональных возможностей устройства.

Указанная цель достигается тем, что устройство содержи-т последовательно соединенные блок ограничения тока, блок набора базиснкгх структур, переключатель, блок памяти и блок сравнения, второй вход которого соединено выходом измерителя экстремума, а первый и второй выходы - со вторыми входами соответственно блока памяти и блока управления, выход которого соединен со вторым входом переключателя, вторыми выходами подключенного к соответствукядим вторы входш модели исходной схемы f причем выход блока организации приращений соединен со вторым входом блока набора базисных структур, вторым и третьим выходами подключенного к третьим входам соответственно измерителя экстремума и модели исходной схемы.

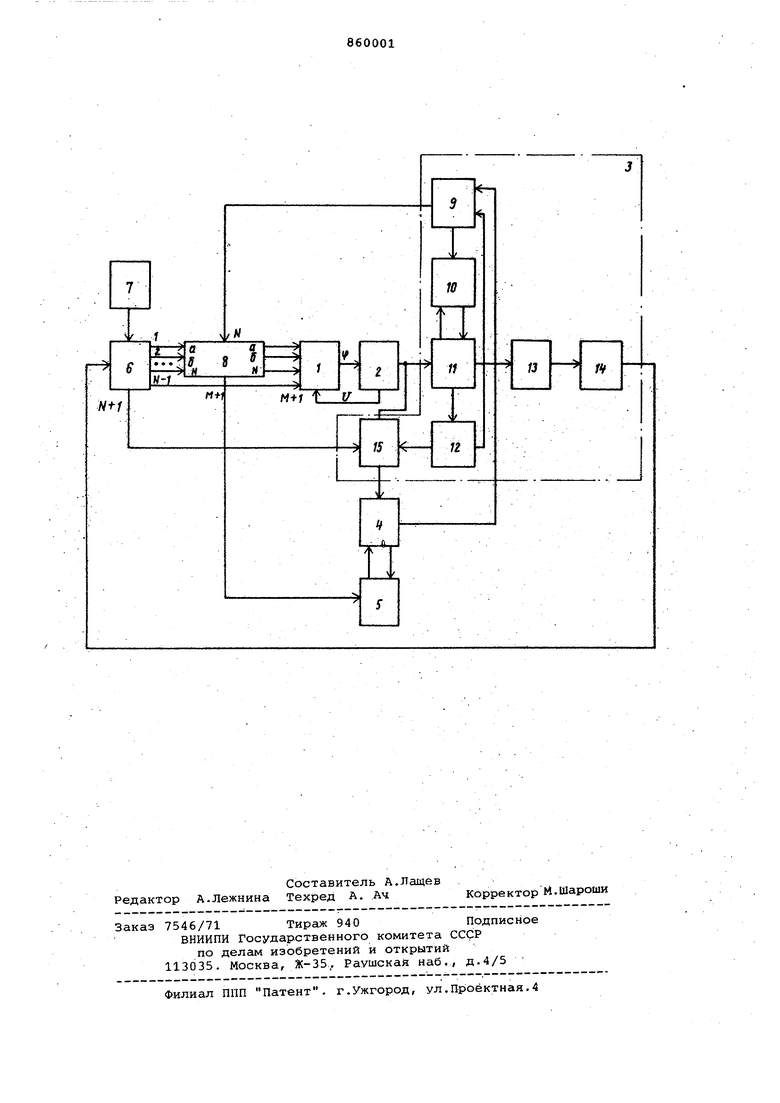

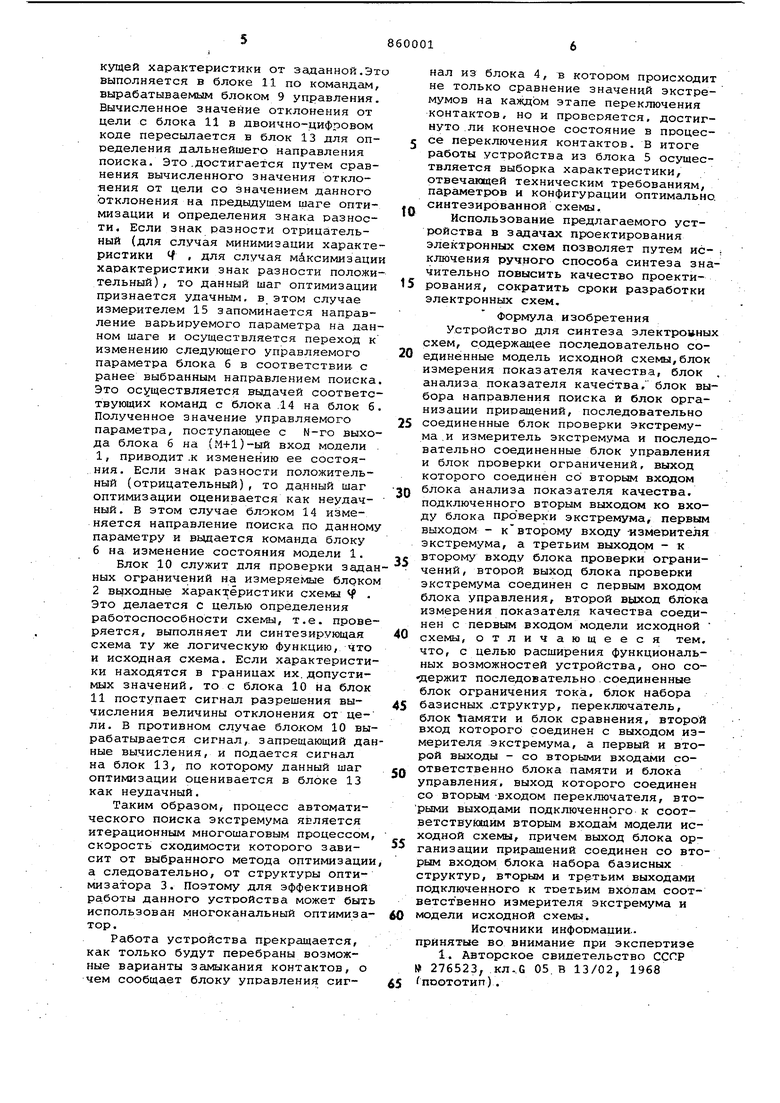

На чертеже представлена блок-схема устройства для синтеза электронных схем.

Устройство содержит модель, 1 исхоной схемы (модель схемы представлена аналоговой вычислительной машиной на которую набирается система М дифференциальных уравнений, где М - число внутренних узлов схемы), блок 2 измерения показателя качества, где вычисляются выходные характеристики схемы, оптимизатор 3, блок сравнения 4, блок 5 памяти, блок 6 набора базисных структур, состоящий из полупроводниковой структуры (диода,транзистора и т.д.) и N регулируемых резисторов, подключенных ,к KajfWOMy выводу полупроводниковой структуры, которые вместе с блоком 7 ограничени тока определяют способ, режим включения и тип полупроводниковой структуры. Блок 7 ограничения тока состоит из источника питания и переменного сопротивления, например потенциометра, служащего для задания тока, вырабатываемого блоком питания. Сведения о характере изменения параметров (резисторов) поступают в модель исходной схемы на (М-И)-ый вход. Переключением контактов в переключателе 8, который работает под действием сигнала, поступаквдего на его N-ый вход из блока управления, добиваются их различных сочетаний. В свою очередьоптимизатор содержит блок 9 управления, блок 10 проверки ограничений, блок 11 анализа показателя качества, блок 12 проверки экстремума, блок 13 выбора, направления поиска, блок 14 организации приращений и измеритель 15 экстремума.

Синтез схем осуществляется следующим образом.

Если известна система уравнений, описывающих работу схемы, то на АВМе, набирается модель 1 исходной схемы в виде системы М дифференциальных уравнений, составленных по методу узловы потенциалов для каждого из М внутренних узлов (внутренним узлом называется узел, к которому не подключен источник напряжения). На АВМ набираются также уравнения для узла, образованного подключением блока 7 ограничителя тока и одного из выводов полупроводниковой структуры. Чтобы иметь возможность изменять модель 1 исходной сгсемы путем подключения к внутренним узлам различных выводов полупроводниковой структуры, необ,ходимо в каждое уравнение расширенно таким образом системы добавить по, N слагаемых, соответствующих этим выводам.

в результате решения данной системы могут быть вычислены наиболее важные характеристики схемы: время переходных процессов, потребляемая схемой мощность, нагрузочная способность помехоустойчивость V , помехоустойчивость V и температурная

ПОЛЛ

стабильность.

В переключателе 8 контакты попарно замкнуты а-а, б-б,... соответствует начальному состоянию Синтезируемой схемы.После пуска устройства блок 2 формирует тест-сигнал КОТОРЫЙ подается на вход управляемой модели 1 исходной схемы, и сигнгшы управления поступают на блок 10 для проверки условий заданных ограничений (технических требований) на перечесленные ранее характеристики . В ответ на входной сигнал V решается система (M-i-l)-ro уравнения и вырабатывается выходная характеристика Ч которая автоматически измеряется блоком 2 и поступает на измеритель 15, а также на блок 11, где определяется сум«1арное отклонение текущей характеристики от заданной.Это выполняется в блоке 11 по командам, вырабатываемым блоком 9 управления. Вычисленное значение отклонения от цели с блока 11 в двоично-цифровом коде пересылается в блок 13 для определения дальнейшего направления поиска. Это.достигается путем сравнения вычисленного значения отклонения от цели со значением данного отклонения на предыдущем шаге оптимизации и определения знака разности. Если знак разности отрицательный (для случая минимизации характеристики tf , для случая максимизации характеристики знак разности положительный) , то данный шаг оптимизации признается удачным, в этом случае измерителем 15 запоминается направление варьируемого параметра на данном шаге и осуществляется переход к изменению следующего управляемого параметра блока 6 в соответствии с ранее выбранным направлением поиска. Это осуществляется выдачей соответствующих команд с блока ,14 на блок 6. Полученное значение управляемого параметра, поступающее с М-го выхода блока 6 на (М+1)-ьлй вход модели . 1, приводит .к изменению ее состояния. Если знак разности положительный (отрицательный) , то да.нный шаг оптимизации оценивается как неудачный. В этом случае блоком 14 изменяется направление поиска по данному параметру и вьщается команда блоку 6 на изменение состояния модели 1.

Блок 10 служит для проверки заданных ограничений на измеряемые блоком 2 выходные характеристики схегла . Это делается с целью определения работоспособности схемы, т.е. проверяется, выполняет ли синтезирующая схема ту же логическую функцию, что и исходная схема. Если характеристики находятся в границах их.допустимых значений, то с блока 10 на блок 11 поступает сигнал разрешения вычисления величины отклонения от цели. В противном случае блоком 10 вырабатывается сигнал, запрещающий данные вычисления, и подается сигнал на блок 13, по которому данный шаг оптимизации оценивается в блоке 13 как неудачный.

Таким образом, процесс автоматического поиска экстремума является итерационным многошаговым процессом, скорость сходимости которого зависит от выбранного метода оптимизации а следовательно, от структуры оптимизатора 3. Поэтому для эффективной работы данного устройства может быть использован многоканальный оптимизатор.

Работа устройства прекращается, как только будут перебраны возможные варианты замыкания контактов, о чем сообщает блоку управления сигнал из блока 4, в котором происходит не только сравнение значений экстремумов на каждом этапе переключения контактов, но и проверяется, достигнуто ли конечное состояние в процес j се переключения контактов. В итоге работы устройства из блока 5 осуществляется выборка характеристики, отвечающей техническим требованиям, параметров и конфигурации оптимально.

синтезированной схемы.

Использование предлагаемого устройства в задачах проектирования электронных схем позволяет путем ис- , ключения ручного способа синтеза значительно повысить качество проектирования, сократить сроки разработки электронных схем,

Формула изобретения Устройство для синтеза электродных схем, содержащее последовательно соединенные модель исходной схемы,блок измерения показателя качества, блок , анализа показателя качества, блок выбора направления поиска и блок организации приращений, последовательно

5 соединенные блок проверки экстремума, и измеритель экстремума и последовательно соединенные блок управления и блок проверки ограничений, выход которого соединен со вторым входом

Q блока анализа показателя качества, подключенного вторым выходом ко входу блока проверки экстремума, первым выходом - квторому входу -измерителя экстремума, а третьим выходом - к

- второму входу блока проверки ограничений, второй выход блока проверки экстремума соединен с первым входом блока управления, второй выход блЬк-а измерения показателя качества соединен с первым входом модели исходной

0 схемы, отличающееся тем, что, с целью расширения функциональных возможностей устройства, оно содержит последовательно.соединенные блок ограничения тока, блок набора

5 базисных .структур, переключатель,

блок памяти и блок сравнения, второй вход которого соединен с выходом измерителя экстремума, а первый и второй выходы - со вторыми входами соответственно блока памяти и блока

0

управления, выход которого соединен со вторым -входом переключателя, вторыми выходами подключенного к соответствующим вторым входам модели исходной схемы, причем выход блока ор5ганизации приращений соединен со вторым входом блока набора базисных структур, вторым и третьим выходами подключенного к тоетьим вхопам соответственно измерителя экстремума и

модели исходной схемы.

Источники информации.. принятые во внимание при экспертизе

1. Авторское свидетельство ССПР 276523, кл..С 05. В 13/02, 1968

поототип).

Авторы

Даты

1981-08-30—Публикация

1979-10-03—Подача