выход соединен со входом переноса первого разряда .третьего двухразрядного двоичного сумматора, первые входы разрядов которого подключены к выходу первого элемента задержки, вторые входы разрядов третьего двухразрядного двоичного сумматора подключены к выходу второго элемента задержки, выход первого разряда третьего двухразрядного двоичного сумматора через четвертый элемент задержки соединен с одним из входов второго блока формирования окончательного результата, другой вход которого соединен с выходбм второго разряда третьего двухразрядного двоичного сукматора, выходы второго блока формирования окончательного результата соединены с выходными шинами разности устройства.

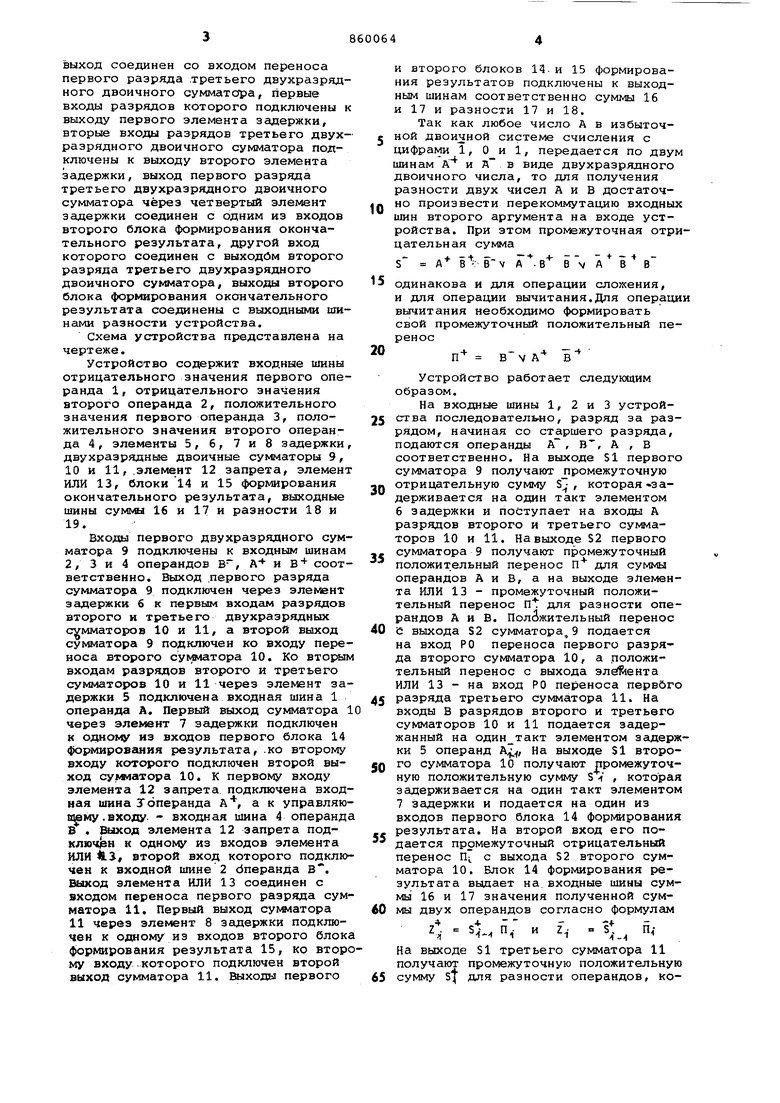

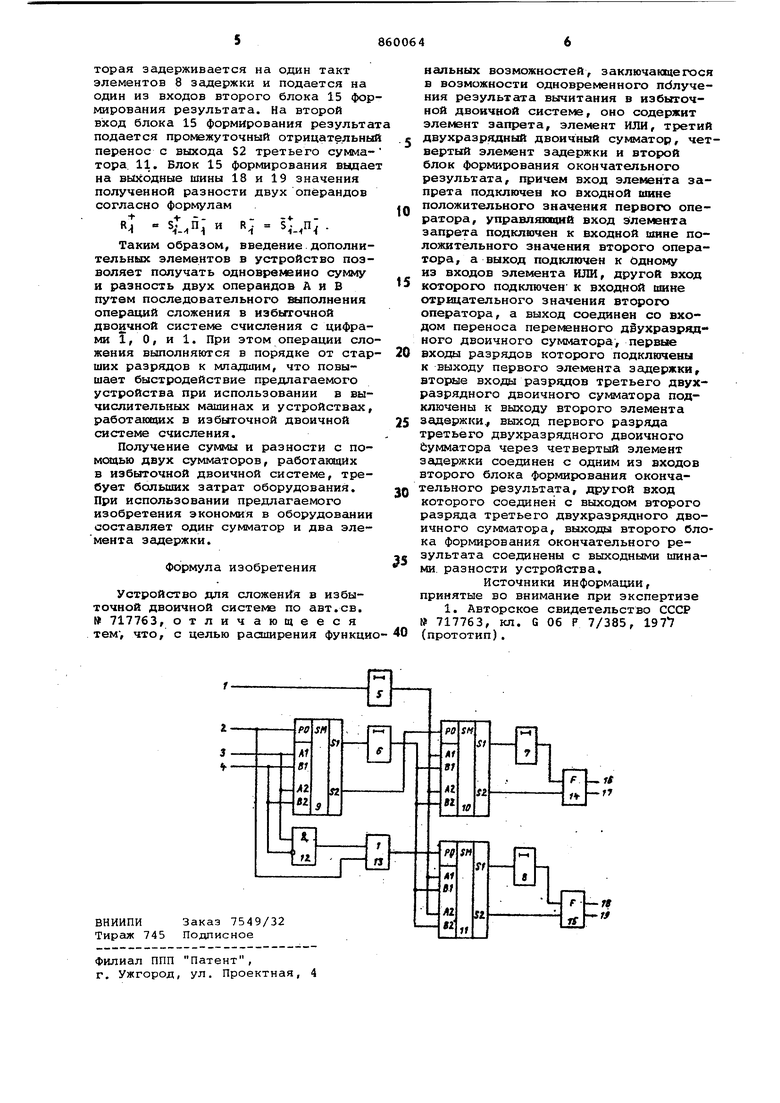

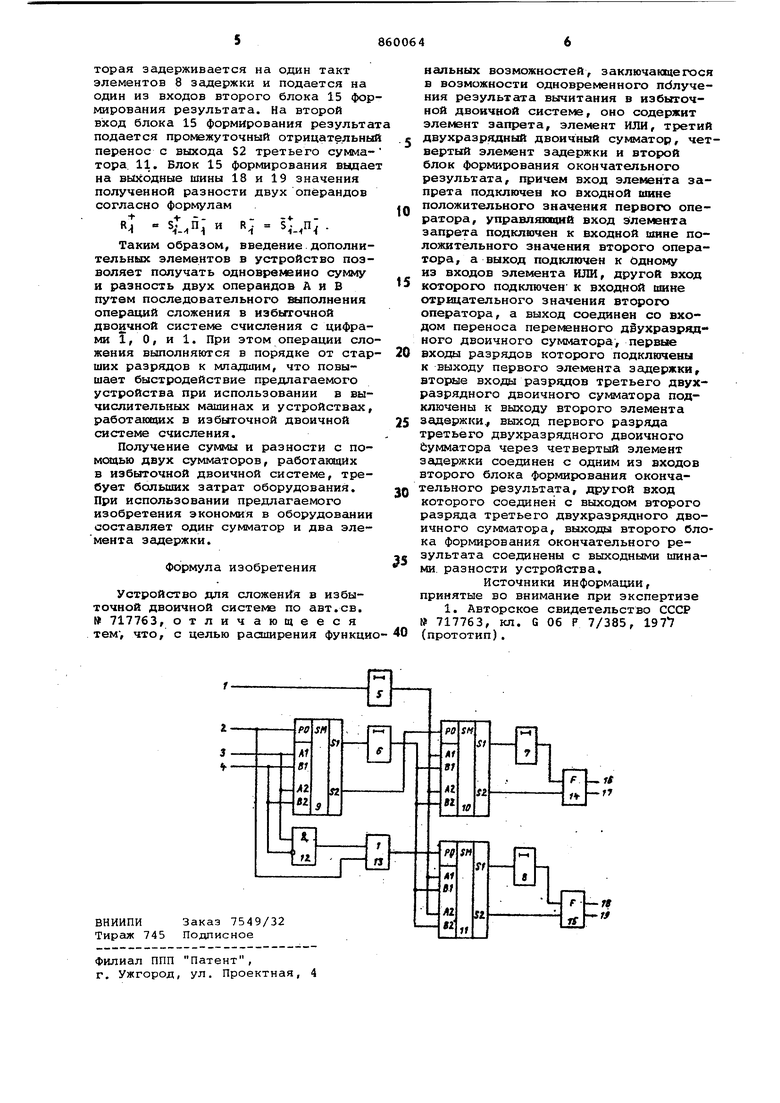

Схема устройства представлена на чертеже.

Устройство содержит входные шины отрицательного значения первого операнда 1, отрицательного значения второго операнда 2, положительного значения первого операнда 3, положительного значения второго операнда 4, элементы 5, 6, 7 и 8 задержки, двухразрядньае двоичные сумматоры 9, 10 и 11, .элемент 12 запрета, элемент ИЛИ 13, блоки 14 и 15 формирования окончательного результата, выходные шины суммы 16 и 17 и разности 18 и 19.

Входам первого двухразрядного сумматора 9 подключены к входным шинам 2, 3 и 4 операндов В, А и В соответственно. Выход первого разряда сумматора 9 подключен через элемент задержки 6 к первым входам разрядов второго и третьего двухразрядных сумматоров 10 и 11, а второй выход сумматора 9 подключен ко входу переноса второго сумматора 10. Ко вторым входам разрядов второго и третьего сумматоров 10 и 11 через элемент задержки 5 подключена входная шина 1 операнда А. Первый выход сумматора 1 через элемент 7 задержки подключен к OfSfioMy из входов первого блока 14 фОЕ 4ирования результата, .ко второму входу которого подключен второй выход сумматора 10. К первому входу элемента 12 запрета подключена входная шина Jоперанда А, а к управляюо вму.входу. - входная шина 4 операнда В . выход элемента 12 запрета подключ;эн к одному из входов элемента ИЛИ 11Э, второй вход которого подключен к входной шине 2 бперанда в. Шаход элемента ИЛИ 13 соединен с входом переноса первого разряда сумматора 11, Первый выход сулвлатора 11 через элемент 8 3 1держки подключен к одному из входов второго блока формирования результата 15, ко второму входу.которого подключен второй выход сумматора 11. Шлходы первого

и второго блоков 14. и 15 формирования результатов подключены к выходным шинам соответственно суммы 16 и 17 и разности 17 и 18.

Так как любое число А в избыточJ ной двоичной системе счисления с цифрами 1, О и 1, передается по двум шинам А и Д в виде двухразрядного двоичного числа, то для получения разности двух чисел А и В достаточQ но произвести перекоммутацию входных шин второго аргумента на входе устройства. При этом промежуточная отрицательная сумма

S А BV -В А В В

одинакова и для операции сложения, и для операции вычитания.Для операции вычитания необходимо формировать свой промежуточный положительный перенос

П В V А в

Устройство работает следукодим образом.

На входные шины 1, 2 и 3 устройства последователь«о, разряд за разрядом, начиная со старшего разряда, подаются операнды А, В , А , В соответственно. На выходе 51 первого сумматора 9 получают промежуточную

отрицательную сумму , которая «задерживается на один такт элементом

6задержки и поступает на входы А разрядов второго и третьего cyivwaторов 10 и 11. На выходе S2 первого

сумматора 9 получают промежуточный положительный перенос П для суммы операндов А и В, а на выходе элемента ИЛИ 13 - промежуточный положительный перенос П для разности операндов А и В. Положительный перенос

с выхода S2 сумматора 9 подается на вход РО переноса первого разряда второго сумматора 10, а положительный перенос с выхода элёК1ента ИЛИ 13 - на вход РО переноса первбго

разряда третьего сумматора 11. На входы В разрядов второго и третьего сумматоров 10 и 11 подается задержанный на элементом задержки 5 операнд h, На выходе S1 второго сумматора 10 получают промежуточную положительную сумму S -t , которая задерживается на один такт элементом

7задержки и подается на один из входов первого блока 14 формирования результата. На второй вход его подается промежуточный отрицательный перенос П с выхода S2 второго сумматора 10. Блок 14 формирования результата выдает на.входные шины суммы 16 и 17 значения полученной суммы двух операндов согласно формулеил

. П,- и

1

На выходе S1 третьего сумматора 11 получают промежуточную положительную 65 сумму st для разности операндов, которая задерживается на один такт элементов 8 задержки и подается на один из входов второго блока 15 фор мирования результата. На второй вход блока 15 формирования результа подается промежуточный отрицательны перенос с выхода 52 третьего сумматора 11. Блок 15 формирования вьвдае на выходные шины 18 и 19 значения полученной разности двух операндов согласно формулам «1 - sT-.П « Ь Таким образом, введение дополнительных элементов в устройство позволяет получать одновремеиио сумму и разность двух операндов А и В путем последовательного заполнения операций сложения в избыточной двоичной системе счисления с цифрами 1,0, и 1. При этом операции сло жения выполняются в порядке от стар ших разрядов к младшим, что повышает быстродействие предлагаемого устройства при использовании в вычислительных машинах и устройствах, работающих в избыточной двоичной системе счисления. Получение суммы и разности с помсэдью двух сумматоров, работакадйх в избыточной двоичной системе, требует больших затрат оборудования. При использовании предлагаемого изобретения экономия в оборудовании составляет один- сумматор и два элемента задержки. Формула изобретения Устройство для сложения в избыточной двоичной системе по авт.св. 717763, отличающееся тем , что, с целью расширения функци нальных возможностей, заключающегося в возможности одновременного п 5лучения результата вычитания в избыточной двоичной системе, оно содержит элемент запрета, элемент ИЛИ, двухразрядиый двоичный сумматор, четвертый элемент задержки и второй блок формирования окончательного результата, причем вход элемента запрета подключен ко входной шине положительного значения первого оператора, управляющий вход элемента запрета подключен к входной шине положительного значения второго оператора, а выход подключен к Одному из входов элемента ИЛИ, другой вход которого подключен к входной шине отрицательного значения второго оператора, а выход соединен со входом переноса nepeNffiHHoro дёухразряд- ного двоичного сумматора, первые входы разрядов которого подключегпл к выходу первого элемента задержки, вторые входы разрядов третьего двухразрядного двоичного сумматора подключены к выходу второго элемента задержки., выход первого разряда третьего двухразрядного двоичного йумматора через четвертый элемент задержки соединен с одним из входов второго блока формирования окончательного результата, другой вход которого соединен с выходом второго разряда третьего двухразрядного двоичного сумматора, выходы второго блока формирования окончательного результата соединены с выходными шинами, разности устройства. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 717763, кл. G 06 F 7/385, (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательное устройство для сложения в избыточной двоичной системе счисления | 1980 |

|

SU968807A1 |

| Устройство для сложения в избыточной двоичной системе | 1977 |

|

SU717763A1 |

| Устройство для алгебраического сложения в избыточной двоичной системе счисления | 1981 |

|

SU1003073A1 |

| Устройство для сложения и вычитания в избыточной двоичной системе счисления | 1980 |

|

SU1015371A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Двухразрядный сумматор в коде "М из N | 1981 |

|

SU980092A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

Авторы

Даты

1981-08-30—Публикация

1978-12-21—Подача