(5) ДВУХРАЗРЯДНЫЙ СУММАТОР В КОДЕ М ИЗ N

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухразрядный сумматор в коде"M из | 1978 |

|

SU798828A1 |

| Сумматор в коде "М из N | 1981 |

|

SU981992A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Сумматор в коде "М" из "N | 1981 |

|

SU983706A1 |

| Сумматор в коде "м из N | 1979 |

|

SU873238A1 |

| Сумматор в коде М из N | 1980 |

|

SU955037A1 |

| Сумматор в коде "М из N | 1981 |

|

SU985781A1 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для сложения и вычитания | 1978 |

|

SU842798A1 |

1

Изобретение относится к вычислительной технике и предназначено для сложения И вычитания чисел, представ.ленных в коде М из N, где N - количество позиций в кодовом .слове; М количество единиц в кодовом слове.

Известен двухразрядный сумматор в коде 2 из 5, содержащий блок местного управления, преобразователи кодов операндов, матрицы элементов И, блоки коррекции, блоки переноса, шифратор младшего разряда и блоки выдачи старшего разряда суммы t.

Недостатком этого устройства является низкое быстродействие вследствие преобразования кодов операндов перед подачей их на матрицы элементов И,

Наиболее близким к предлагаемому является двухразрядный сумматор в коде М из N, содержащий блок выдачи младшего разряда суммы, шифратор младшего разряда, блок контроля младшего разряда, матрицу сложения младшего разряда, блок переноса младшего разряда, блок переноса старшего разряда, матрицу сложения старшего разряда,) шифратор старшего разряда, блок контроля старшего разряда, блоки выдачи старшего разряда суммы Г2}.

Недостатком этого устройства является то, что оно предназначено для выполнения только одной арифметической операции - сложения.

Цель изобретения - расширение функ

10 циональных возможностей двухразрядного сумматора в коде М из N за счет выполнения операции вычитания.

Поставленная цель достигается тем, что двухразрядный сумматор в коде М

15 из N, содержащий матрицу сложения младшего разряда, шифратор младшего разряда, первый блок выдачи младшего разряда, блок контроля младшего раз-„ ряда, блок формирования /переноса, матрицу сложения старшего разряда, дэа шифратора старшего разряда, два блока выдачи старшего разряда, блок контроля старшего разряда, причем первый и второй входы матрицы сложения младшего разряда,являются соответственно входами младшего разряда первого и второго слагаемых устройства, ее первый выход подключен к входу шифратора младшего разряда, выход которого соединен с первым .входом первого блока выдачи младшего разряда, второй и третий входы которого подключены соответственно к пер- ю вому и второму выходам блока контроля

младшего разряда, первый и второй входы которого являются первым и вторым контрольными входами устройства, выход первого блока выдачи младше-|5 го разряда является выходом младшего разряда результата устройства, второй выход матрицы сложения младшего разряда подключен к первому входу блока формирования переноса, первый и второй входы матрицы сложения старшего разряда являются соответственно входами старшего разряда первого и второго слагаемых устройства, ее первый выход подключен к входам первого и второго шифраторов старшего разряда, выход первого шифратора старшего разряда подключен к первому входу первого блока выдачи старшего разряда, выход второго шифратора старшего разряда подключен к первому входу второго блока выдачи старшего разряда, вторые и третьи входы первого и второго блоков выдачи старшего разряда подключены соответственно к первому и второму выходам блока контроля старшего разряда, первый и второй входы которого являются третьим и четвертым контрольными входами устройства, второй выход матрицы сложения старшего разряда подключен к вто рому входу блока формирования переноса, первый и второй выходы которого подключены к первым управляющим входам первого и второго блоков выдачи старшего разряда соответственно, а выходь последних подключены к- выходу старшего разряда результата уст ройства, содержит блок формирования знака результата, второй блок выдачи младшего разряда, третий и четвертый блоки выдачи старшего разряда, причем входы младшего и старшего разрядов блока формирования знака результата подключены- соответственно к пер вому и второму входа блока переноса и к первому и второму информационным выходам устройства, информацио ный вход блока, формирования знака 9

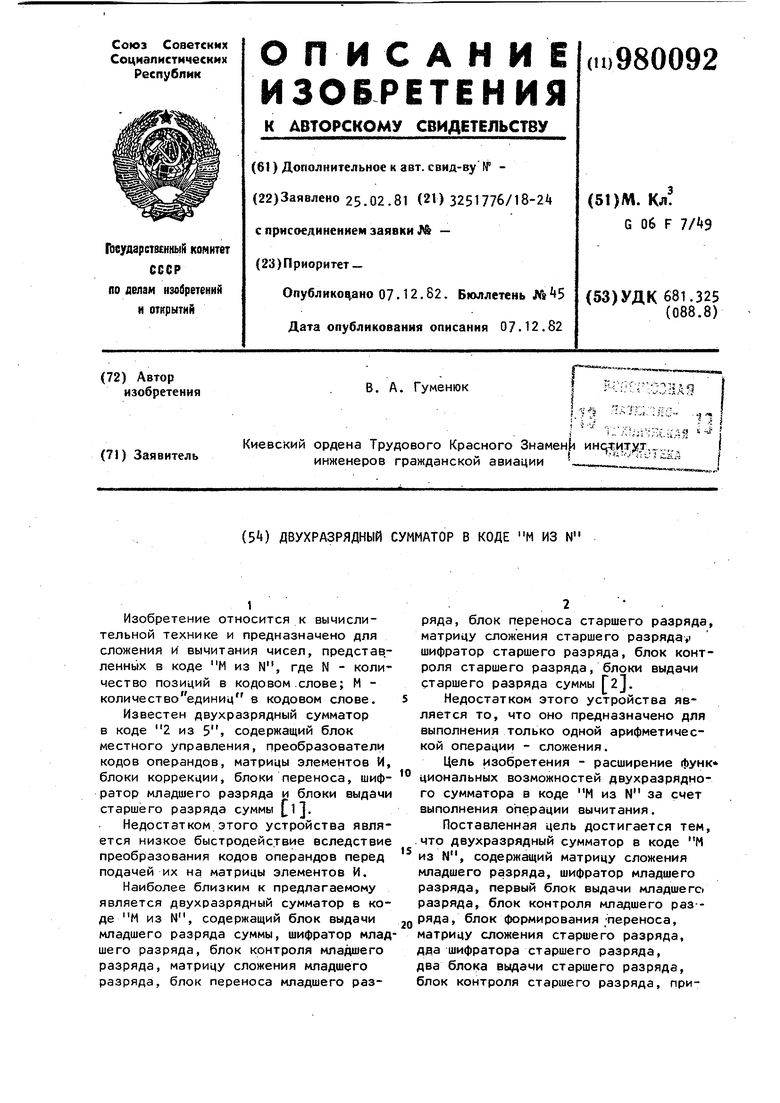

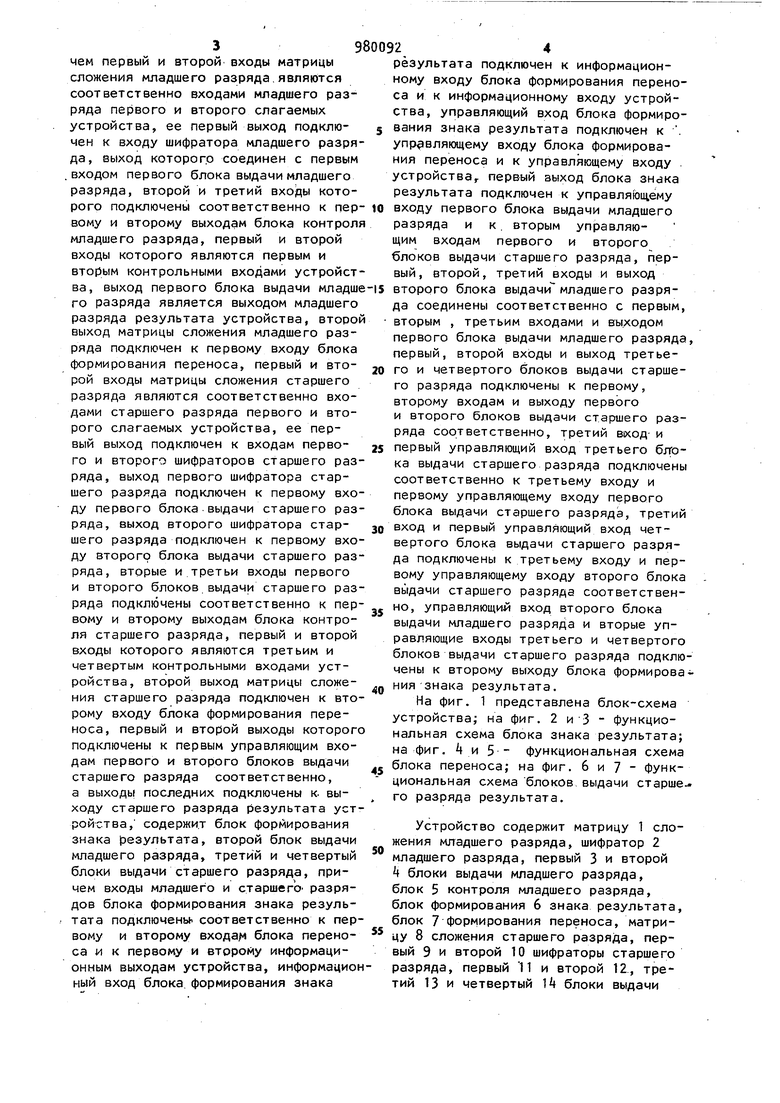

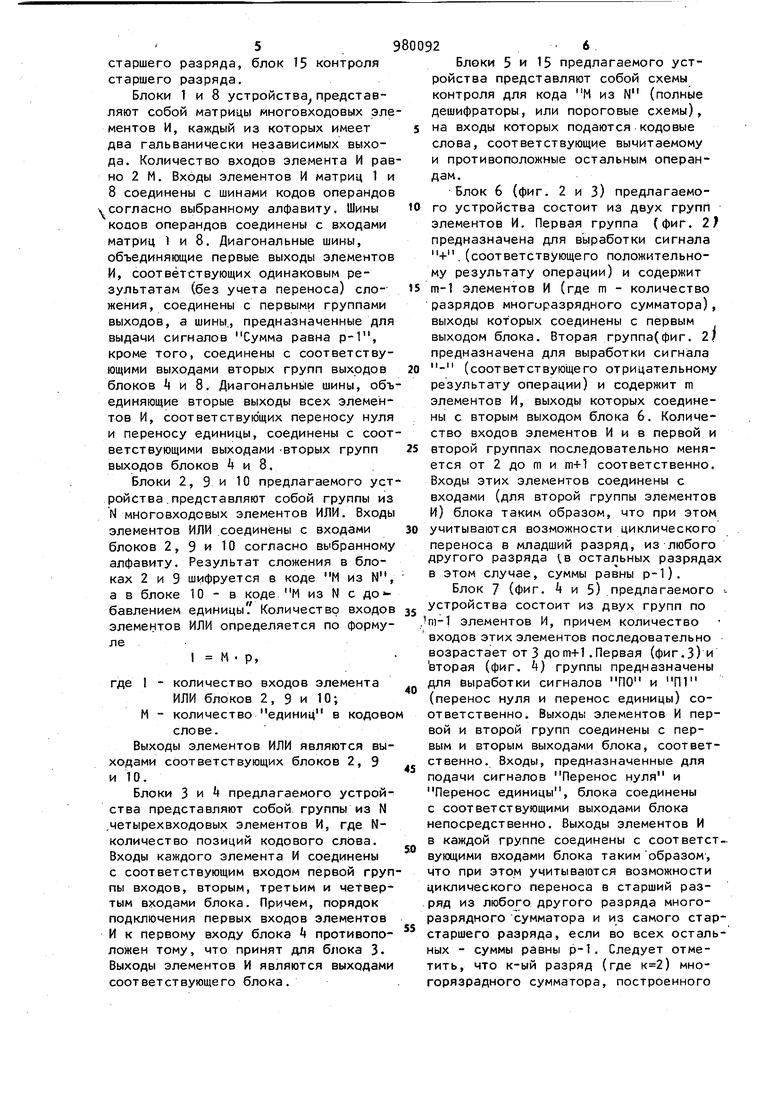

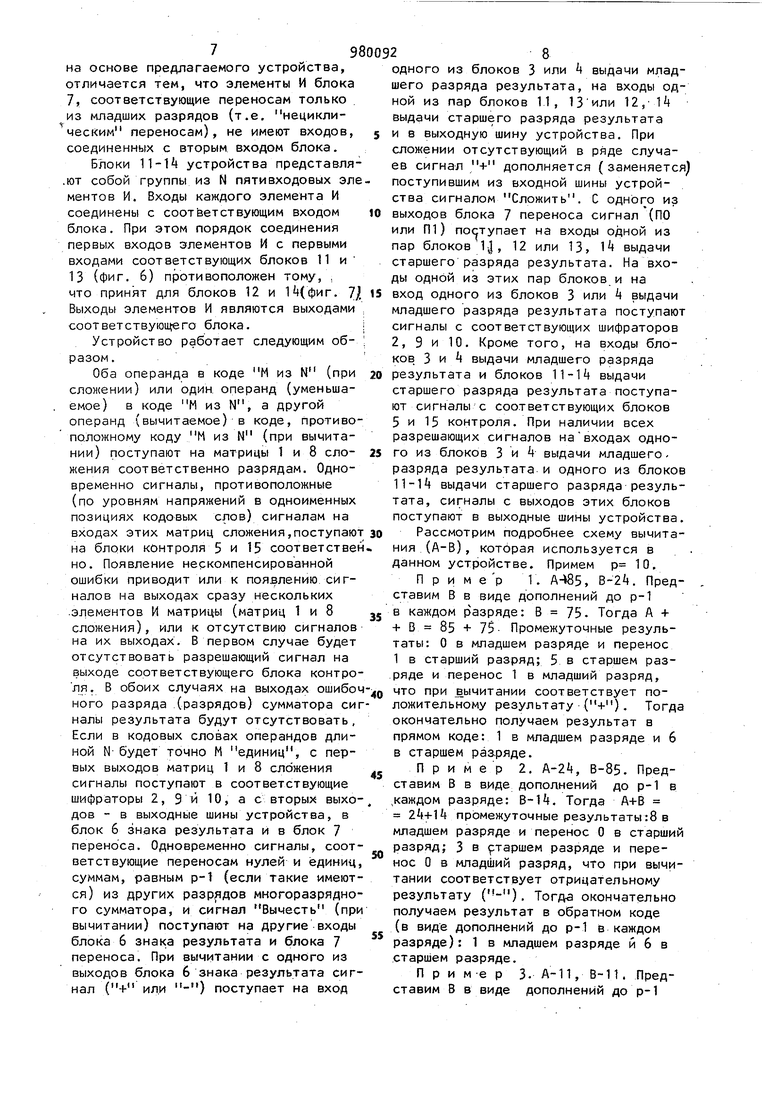

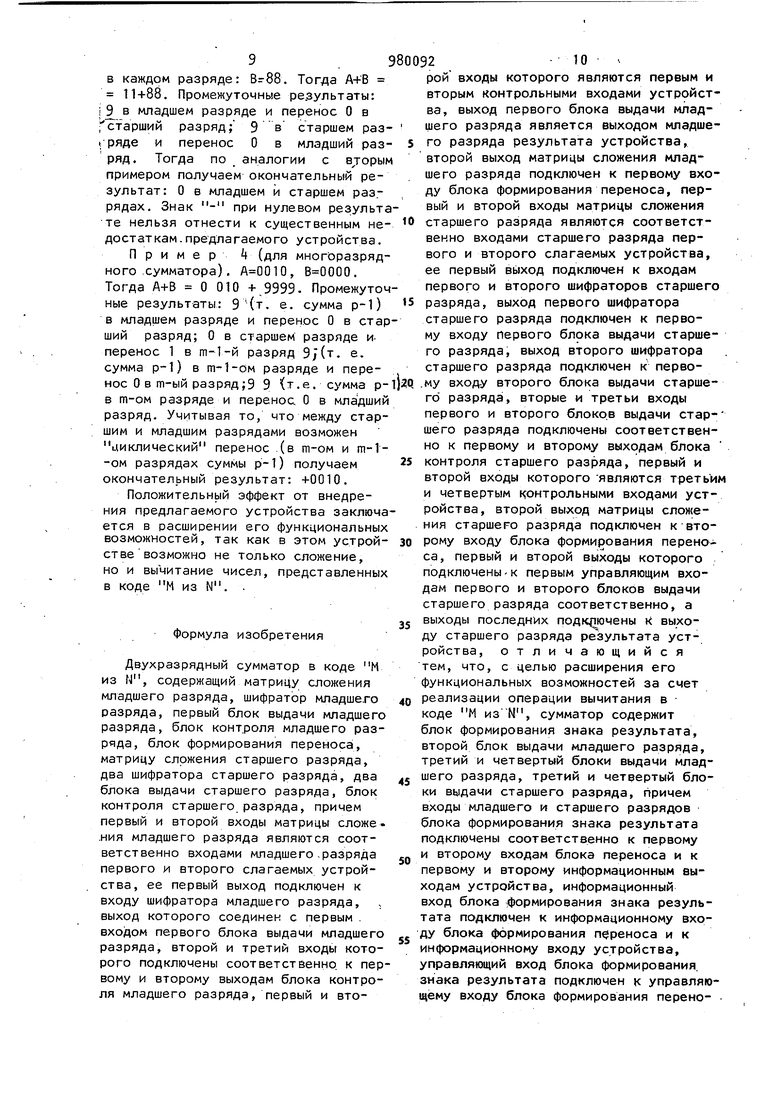

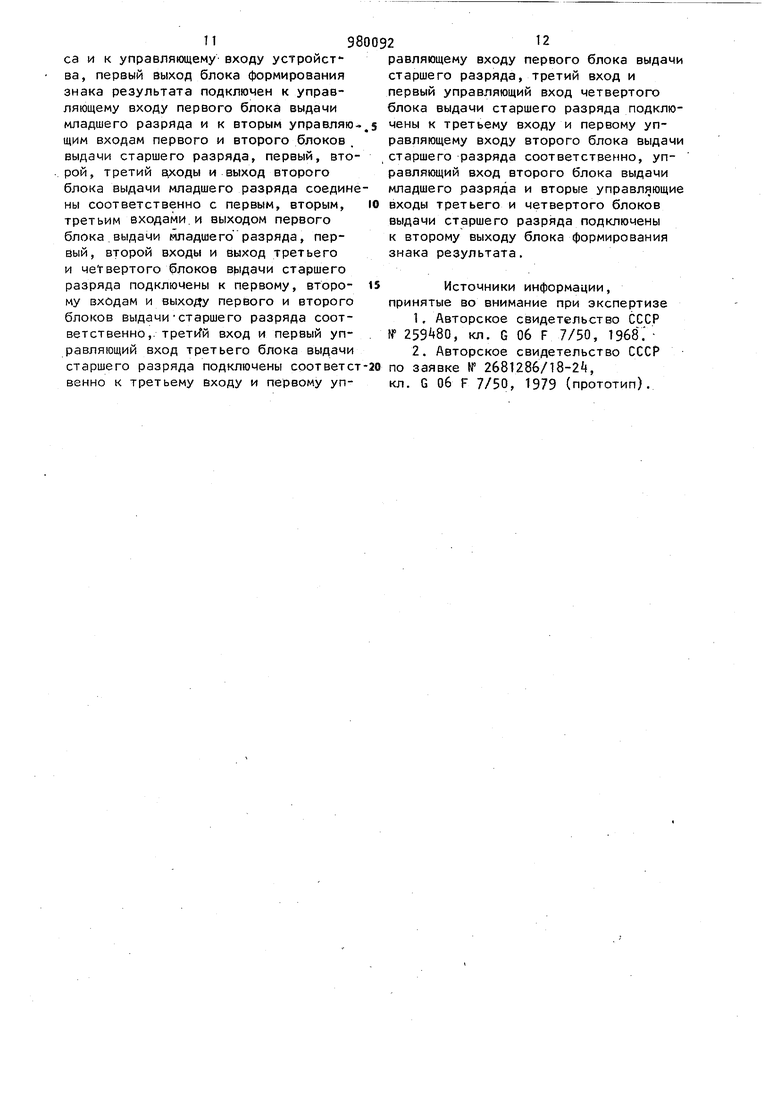

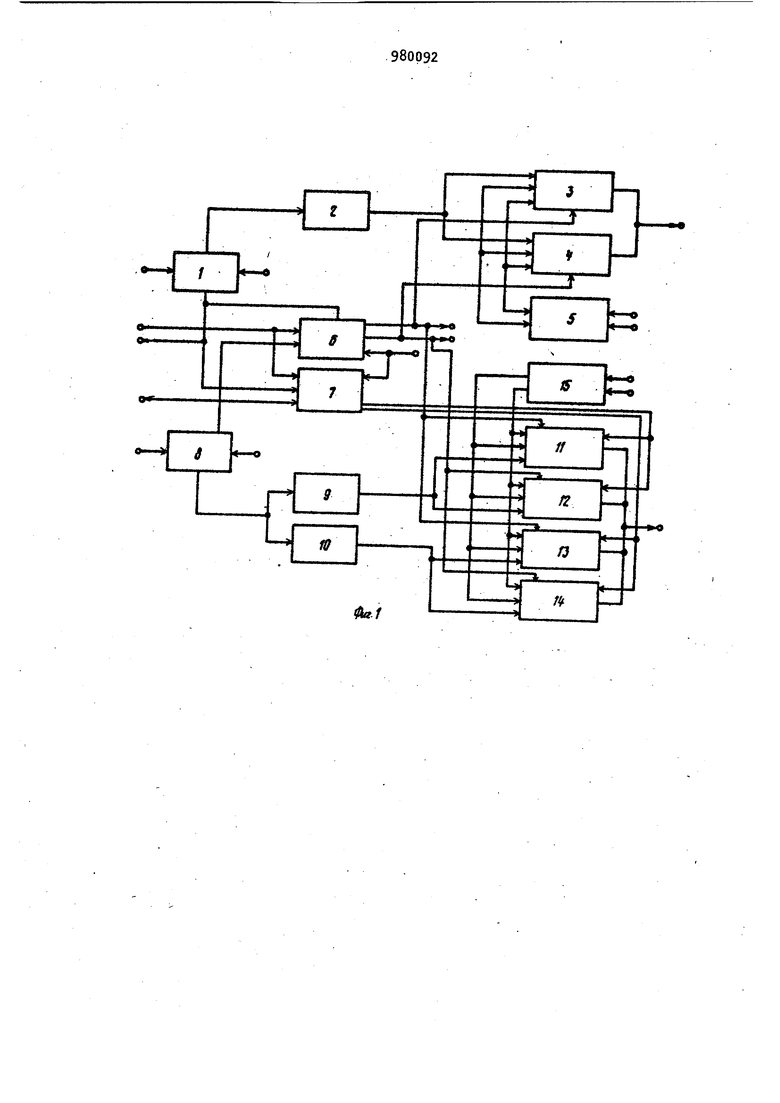

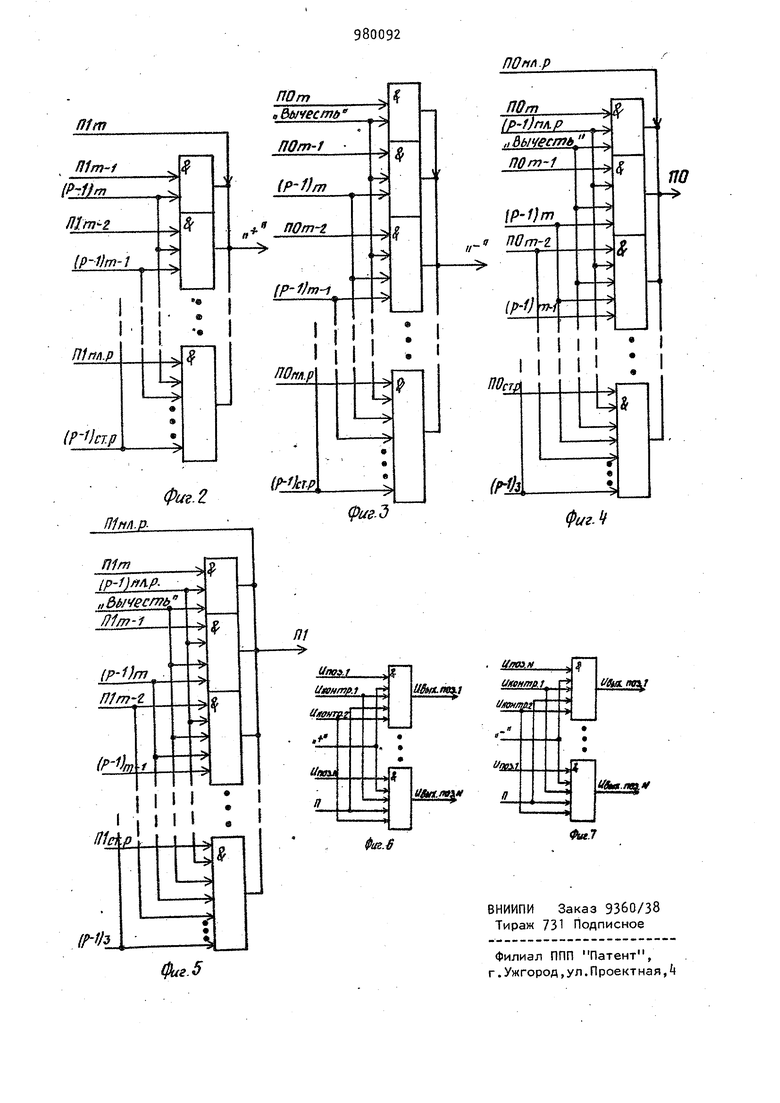

щим входам первого и второго блоков выдачи старшего разряда, первый, второй, третий входы и выход 24 результата подключен к информационному входу блока формирования переноса и к информационному входу устройства, управляющий вход блока формирования знака результата подключен к . управляющему входу блока формирования переноса и к управляющему входу . устройства,, первый выход блока знака результата подключен к управляющ ему входу первого блока выдачи младшего разряда и к. вторым управляювторого блока выдачи младшего разряда соединены соответственно с первым, вторым , третьим входами и выходом первого блока выдачи младшего разряда, первый, второй входы и выход третьего и четвертого блоков выдачи старшего разряда подключены к первому, второму входам и выходу первого и второго блоков выдачи старшего разряда соответственно, третий В1ход- и первый управляющий вход третьего блока выдачи старшего разряда подключены соответственно к третьему входу и первому управляющему входу первого блока выдачи старшего разряда, третий вход и первый управляющий вход четвертого блока выдачи старшего разряда подключены к третьему входу и первому управляющему входу второго блока выдачи старшего разряда соответственно, управляющим вход второго блока выдачи младшего разряда и вторые управляющие входы третьего и четвертого блоков выдачи старшего разряда подключены к второму выходу блока формирования знака результата. На фиг. 1 представлена блок-схема устройства; на фиг. 2 и3 - функциональная схема блока знака результата; на фиг. 4 и 5 - функциональная схема блока переноса,- на фиг. 6 и 7 - функциональная схема блоков, выдачи старше го разряда результата. Устройство содержит матрицу 1 сложения младшего разряда, шифратор 2 младшего разряда, первый 3 и второй k блоки выдачи младшего разряда, блок 5 контроля младшего разряда, блок формирования 6 знака результата, блок 7 формирования переноса, матрицу 8 сложения старшего разряда, первый Э и второй 10 шифраторы старшего разряда, первый 11 и второй 12, третий 13 и четвертый 14 блоки выдачи старшего разряда, блок 15 контроля старшего разряда. Блоки 1 и 8 устройства представляют собой матрицы многовходовых эле ментов И, каждый из которых имеет два гальванически независимых выхода. Количество входов элемента И рав но 2 М. Входы элементов И матриц 1 и 8 соединены с шинами кодов операндов ч согласно выбранному алфавиту, кодов операндов соединены с входами матриц 1 и 8. Диагональные шины, объединяющие первые выходы элементов И, соответствующих одинаковым результатам (без учета переноса) сложения, соединены с первыми группами выходов, а шины., предназначенные для выдачи сигналов Сумма равна р-1, кроме того, соединены с соответствующими выходами вторых групп выходов блоков и 8. Диагональные шины, объ единяющие вторые выходы всех элементов И, соответствующих переносу нуля и переносу единицы, соединены с соот ветствующими выходами -вторых групп выходов блоков 4 и 8. Блоки 2, 9 и 10 предлагаемого уст ройства .представляют собой группы из N многовходовых элементов ИЛИ. Входы элементов ИЛИ .соединены с входами блоков 2, 9 и 10 согласно выбранному алфавиту. Результат сложения в блоках 2 и 9 шифруется в коде М из N, а в блоке 10 - в коде М из N с до бавлением единицы . Количество входов элементов ИЛИ определяется по формулеI М- р. количество входов элемента ИЛИ блоков 2, 9 и 10; количество единиц в кодово ело ве. Выходы элементов ИЛИ являются выходами соответствующих блоков 2, 9 и 10. Блоки 3 и предлагаемого устройства представляют собой группы из N .четырехвходовых элементов И, где Nколичество позиций кодового слива. Входы каждого элемента И соединены с соответствующим входом первой груп пы входов, вторым, третьим и четвертым входами блока. Причем, порядок подключения первых входов элементов И к первому входу блока k противоположен тому, что принят для блока 3. Выходы элементов И являются выходами соответствующего блока. Шины 2 6. Блоки 5 и 15 предлагаемого устройства представляют собой схемы контроля для кода М из N (полные дешифраторы, или пороговые схемы), на входы которых подаются кодовые слова, соответствующие вычитаемому и противоположные остальным операндам. Блок 6 (фиг. 2 и 3) предлагаемого устройства состоит из двух групп элементов И. Первая группа (фиг. 2 предназначена для выработки сигнала +.(соответствующего положительному результату операции) и содержит т-1 элементов И (где m - количество разрядов многоразрядного сумматора), выходы которых соединены с первым выходом блока. Вторая группа(фиг. 2/ предназначена для выработки сигнала - (соответствующего отрицательному результату операции) и содержит m элементов И, выходы которых соединены с вторым выходом блока 6. Количество входов элементов И и в первой и второй группах последовательно меняется от 2 до m и т+1 соответственно. Входы этих элементов соединены с входами (для второй группы элементов И) блока таким образом, что при этом учитываются возможности циклического переноса в младший разряд, из любого другого разряда в остальных разрядах в этом случае, суммы равны р-1). Блок 7 (фиг. и 5) .предлагаемого .. устройства состоит из двух групп по п)-1 элементов И, причем количество входов этих элементов последовательно возрастает от 3 до т+1.Первая (фиг.З)и вторая (фиг. ) группы предназначены для выработки сигналов ПО (перенос нуля и перенос единицы) соответственно. Выходы элементов И первой и второй групп соединены с первым и вторым выходами блока, соответственно. Входы, предназначенные для подачи сигналов Перенос нуля и Перенос единицы, блока соединены с соответствующими выходами блока непосредственно. Выходы элементов И в каждой группе соединены с соответствующими входами блока таким образом, что при этом учитываются возможности циклического переноса в старший разряд из любого другого разряда многоразрядного сумматора и из самого старстаршего разряда, если во всех остальных - суммы равны р-1. Следует отметить, что к-ый разряд (где ) многорязрадного сумматора, построенного на основе предлагаемого устройства, отличается тем, что элементы И блока 7, соответствующие переносам только из младших разрядов (т.е. нецикли ес им переносам), не имеют входов, соединенных с вторым входом блока. Блоки 11-14 устройства представля.ют собой группы из N пятивходовых эле ментов И. Входы каждого элемента И соединены с соответствующим входом блока. При этом порядок соединения первых входов элементов И с первыми входами соответствующих блоков 11 и 13 (фиг. 6) противоположен тому, что принят для блоков 12 и 14{фиг. 11 Выходы элементов И являются выходами соответствующего блока. Устройство работает следующим образом. Оба операнда в коде М из N (при сложении) или один операнд (уменьшаемое) в коде М из N, а другой операнд (вычитаемое) в коде, противо положному коду М из N (при вычитании) поступают на матрицы 1 и 8 сложения соответственно разрядам. Одновременно сигналы, противоположные (по уровням напряжений в одноименных позициях кодовых слов) сигналам на входах этих матриц сложения,поступаю на блоки контроля 5 и 15 соответстве но. Появление нескомпенсированной ошибки приводит или к появлению сигналов на выходах сразу нескольких .элементов И матрицы (матриц 1 и 8 сложения), или к отсутствию сигналов на их выходах. В первом случае будет отсутствовать разрешающий сигнал на выходе соответствующего блока контро ля. в обоих случаях на выходах ошибо ного разряда (разрядов) сумматора си налы результата будут отсутствовать, Если в кодовых словах операндов длиной N- будет точно М единиц, с первых выходов матриц 1 и 8 сложения сигналы поступают в соответствующие шифраторы 2, 9 и 10, а с вторых выхо дов - в выходные шины устройства, в блок б знака результата и в блок 7 переноса. Одновременно сигналы, соот ветствующие переносам нулей и единиц суммам, равным р-1 (если такие имеют ся) из других разрядов многоразрядно го сумматора, и сигнал Вычесть (пр вычитании) поступают на другие входы блока 6 знака результата и блока 7 переноса. При вычитании с одного из выходов блока 6 знака результата сиг нал (+ или -) поступает на вход одного из блоков 3 или 4 выдачи младшего разряда результата, на входы одной из пар блоков 11, 13или 12, Н выдачи старшего разряда результата и в выходную шину устройства. При сложении отсутствующий в ряде случаев сигнал + дополняется (заменяется) поступившим из входной шины устройства сигналом Сложить. С одного из выходов блока 7 переноса сигнал (ПО или П1) поступает на входы одной из пар блоков 1J, 12 или 13, 1 выдачи старшего разряда результата. На входы одной из этих пар блоков и на вход одного из блоков 3 или k выдачи младшего разряда результата поступают сигналы с соответствующих шифраторов 2, Э и 10. Кроме того, на входы блоков. 3 и выдачи младшего разряда результата и блоков 11-1 if выдачи старшего разряда результата поступают сигналы с соответствующих блоков 5 и 15 контроля. При наличии всех разрешающих сигналов навходах одного из блоков 3 и 4 выдачи младшего. разряда результата и одного из блоков 11-1 выдачи старшего разряда результата, сигналы с выходов этих блоков поступают в выходные шины устройства. Рассмотрим подробнее схему вычитания (А-В), которая используется в данном устройстве. Примем р 10. П р и М ер 1. , Q-2k. Представим В в виде дополнений до р-1 в каждом разряде: В 75. Тогда А + + В 85 + 75- Промежуточные результаты: О в младшем разряде и перенос 1 в старший разряд; 5 в старшем разряде и перенос 1 в младший разряд. что при в.ычитании соответствует положительному результату (+). Тогда окончательно получаем результат в прямом коде: 1 в младшем разряде и 6 в старшем разряде. Пример 2. А-24, В-85. Представим В в виде дополнений до р-1 в ,каждом разряде: . Тогда А+В промежуточные результаты :8 в младшем разряде и перенос О в старший разряд; 3 в таршем разряде и перенос О в младший разряд, что при вычитании соответствует отрицательному результату (-). Тогда окончательно получаем результат в обратном коде (в виде дополнений до р-1 в каждом разряде): 1 в младшем разряде и 6 в .старшем разряде. П р и м-е р 3. А-11, В-11. Представим В в виде дополнений до р-1 в каждом разряде: . Тогда А+В 11+88. Промежуточные результаты: i 9 в младшем разряде и перенос О в .старший разряд; 9 в старшем разгряде и перенос О в младший разряд . Тогда по аналогии с BjopbiM примером получаем окончательный результат: О в младшем и старшем разрядах. Знак - при нулевом результа те нельзя отнести к существенным не достаткам.предлагаемого устройства. Пример k (для многЬразрядного .сумматора), , , Тогда А+В О 010 +9999. Промежуточ ные результаты: 9 (т, е, сумма р-1) в младшем разряде и перенос О в стар ший разряд; О в старшем разряде иперенос 1 в m-1-й разряд 9;(т. е. сумма р-1) в т-1-ом разряде и перенос О в т-ый разряд;9 9 (т,е, сумма pв т-ом разряде и перенос. О в младший разряд. Учитывая то, что между старшим и младшим разрядами возможен циклический перенос .(в т-ом и т-1-ом разрядах суммы р-1) получаем окончательный результат: +0010,

Положительнь|й эффект от внедрения предлагаемого устройства заключается в расширении его функциональных возможностей, так как в этом устройстве возможно не только сложение, но и вычитание чисел, представленных в коде М из N, .

Формула изобретения

Двухразрядный сумматор в коде М из N, содержащий матрицу сложения младшего разряда, шифратор младшего разряда, первый блок выдачи младшего разряда, блок контроля младшего разряда, блок формирования переноса, матрицу сложения старшего разряда, два шифратора старшего разряда, два блока выдачи старшего разряда, блок контроля старшего разряда, причем первый и второй входы матрицы сложе.ния младшего разряда являются соответственно входами младшего-разряда первого и второго слагаемых устройства, ее первый выход подключен к входу шифратора младшего разряда, выход которого соединен с первым . входом первого блока выдачи младшего разряда, второй и третий входы которого подключены соответственно, к первому и второму выходам блока контроля младшего разряда, первый и вто9

ГО разряда, вторые и третьи входы первого и второго блоко.в выдачи старшего разряда подключены соответственно к первому и второму выходам блока контроля старшего разряда, первый и

5 второй входы которого ЯВЛЯЮТСЯ третьим и четвертым контрольными входами устройства, второй выход матрицы сложения старшего разряда подключен квторому входу блока формирования перено0са, первый и второй выходы которого подключены-к первым управляющим входам первого и второго блоков выдачи старшего разряда соответственно, а - выходы последних под(с{тючены К выходу старшего разряда результата устройства, отличающийся тем, что, с целью расширения его функциональных возможностей за счет реализации операции вычитания в

0 коде М из N, сумматор содержит блок формирования знака результата, второй блок выдачи младшего разряда, третий и четвертый блоки выдачи младшего разряда, третий и четвертый блоки выдачи старшего разряда, причем входы младшего и старшего разрядов блока формирования знака результата подключены соответственно к первому и второму входам блока переноса и к

0 первому и второму информационным выходам устройства, информационный вход блока формирования знака результата подключен к информационному входу блока формирования переноса и к

5 информационному входу устройства, управлякяций вход блока формирования. знака результата подключен к управляющему входу блока формирования перено2- 10 рой входы которого являются первым и вторым контрольными входами устройства, выход первого блока выдачи младшего разряда является выходом младшего разряда результата устройства, второй выход матрицы сложения младшего разряда подключен к первому входу блока формирования переноса, первый и второй входы матрицы сложения старшего разряда являются соответственно входами старшего разряда первого и второго слагаемых устройства, ее первый вь1ход подключен к входам первого и второго шифраторов старшего разряда, выход первого шифратора старшего разряда подключен к первому входу первого блока выдачи старшего разряда, выход второго шифратора старшего разряда подключен к первому входу второго блока выдачи старшеса и к управлякмцему входу устройства, первый выход блока формирования знака результата подключен к управляющему входу первого блока выдачи младшего разряда и к вторым управляю-. щим входам первого и второго блоков . выдачи старшего разряда, первый, второй, третий цходы и выход второго блока выдачи младшего разряда соедине ны соответственно с первым, вторым, третьим входами.и выходом первого блока . выдачи младшего разряда, первый, второй входы и выход третьего и четвертого блоков выдачи старшего разряда подключены к первому, второму входам и выходу первого и второго блоков выдачистаршего разряда соответственно,. трет1 й вход и первый управляющий вход третьего блока выдачи старшего разряда подключены соответст венно к третьему Входу и первому управляющему входу первого блока выдачи старшего разряда, третий вход и первый управляющий вход четвертого блока выдачи старшего разряда подключены к третьему входу и первому управляющему входу второго блока выдачи старшего разряда соответственно, управляющий вход второго блока выдачи младшего разряда и вторые управляющие

входы третьего и четвертого блоков выдачи старшего разряда подключены к второму выходу блока формирования знака результата,

Источники информации,

принятые во внимание при экспертизе

кл. G Об F 7/50, 1979 (прототип).

(

в

Ф

I I ill

I

(p-fhip

фиг.г

ПОпл.р

по

{ М I

(p-Si

Авторы

Даты

1982-12-07—Публикация

1981-02-25—Подача