Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах и устройствах, работающих в избыточной двоичной системе счисления с цйфракш / -1,0,1 особенно в случае повьвпенных требований к быстродействию и точности вычислений. Известно устройство для параллельного и последовательного выполнения сложения старшими разряда ии вперед i и 21.

Время сложения и затраты оборудо- ваийя устройства в 5 раз больше, чем у полного одноразрядного сумматора, кроме того, в нем отсутствует инвариантность к инверсии двоичного представления операндов, что усложняет выполнение вычитания, а также эффективное округление результатов.

Наиболее близким к изобретению является устройство для сложения и вычитания в избыточной двоичной сие-. теме счисления, которое содержит в первом каскаде блоки формирования отрицательной суммы и положительного переноса для сложения одного операнда с положительной частью второго, во втором каскаде блоки формирования положительной суммы и отрицательного . переноса для сложения первого промежуточного результата с отрицательной частью вторюго операнда и в третьем троичный триггер для преобразования на его входных вентилях второго промежуточного результата в окончательный и хранения последнего СЗ.

Блоки формирования суммы и переноса отличаются от соответствующих

10 блоков полного двоичного сумматора. Поэтому построение этих блоков, особенно в случае реализации на СИС, приводит к относительно большим затратам оборудования на один разряд -с.

15 устройства и. низкому быстродействию. Учитывая наличие блока формирования окончательного результата 1 входные вентили триггера), затраты оборудования и время сложения в среднем .в

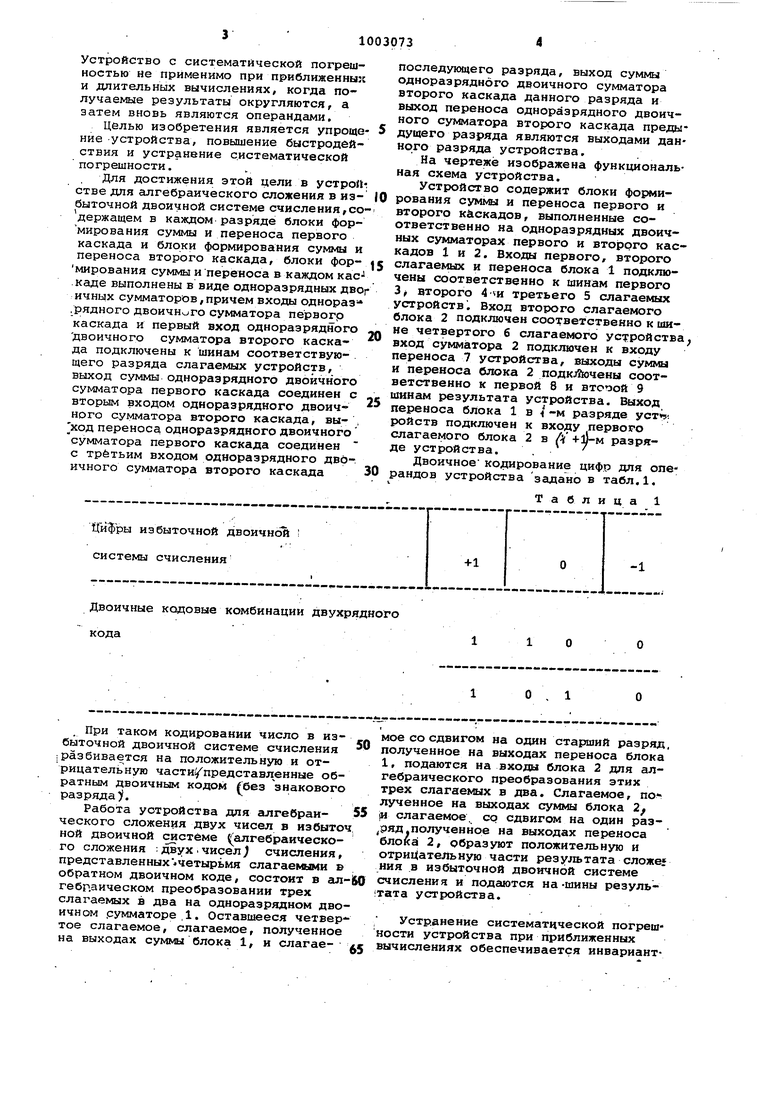

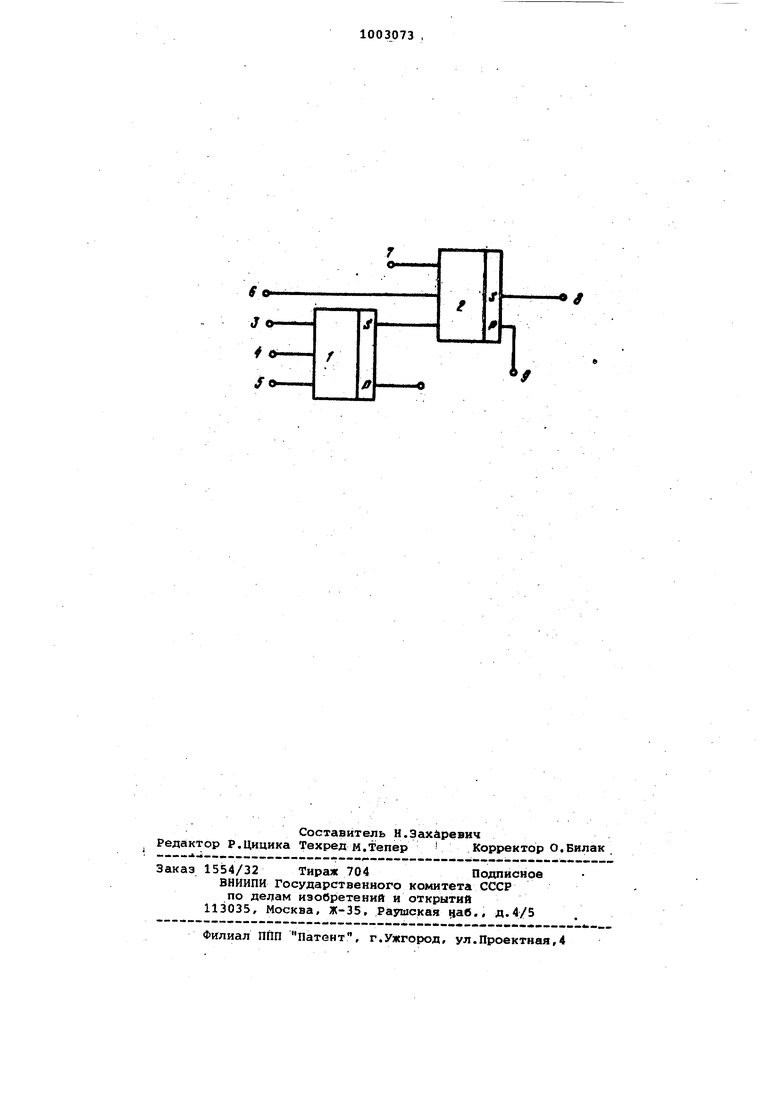

20 5 раз больше, чем у полного одноразрядного двоичного сумматора. Отсутствие, инвариантности устройства по отношению к -инверсии знака цифр троичного представления операндов при25водит к преобладанию цифр определенного знака в троичном представле.нии результатасложения. Округление таких чисел, состоящее в отбрасывании лишних младших разрядов, приво30 дит к систематической погрешности. Устройство с систематической погрешностью не применимо при приближенны:: и длительных вычислениях, когда получаемые результаты округляются, а затем вновь являются операндами. Целью изобретения является упрощение -устройства, повышение быстродействия и устранение систематической погрешности. Для достижения этой цели в устрой стве для алгебраического сложения в избыточной двоичной системе счисления,со держащем в каждом разряде блоки формирования суммы и переноса первого каскада и блоки формирования суммы и переноса второго каскада, блоки формирования суммы и переноса в каждом кас .каде выполнены в виде одноразрядных дво ичных сумматоров, причем входы однораз .рядного двоичного сумматора первогр каскада и первый вход одноразрядного двоичного сумматора второго каскада подключены к шинам соответствую- . щего разряда слагаемых устройств, выход суммы одноразрядного двоичного сумматора первого каскада соединен с вторым входом одноразрядного двоичного сумматора второго каскада, переноса одноразрядного двоичного сумматора первого каскада соединен с третьим входом одноразрядного двбг ичного сумматора второго каскада последующего разряда, выход суммы одноразрядного двоичного сумматора второго каскада данного разряда и выход переноса одноразрядного двоичного сумматора второго каскада предыдущего разряда являются выходами данного разряда устройства. На чертеже изображена функциональная схема устройства. Устройство содержит блоки формирования cyMNSJ и переноса первого и второго каскадов, выполненные соответственно на одноразрядных двоичных сумматорах первого и второго каскадов J и 2. Входы первого, второго слагаемых и переноса блока 1 подключены соответственно к шинам первого 3i второго третьего 5 слагаемых устройств I Вход второго слагаемого блока 2 подключен соответственно к шине четвертого б слагаемого устройства вход сумматора 2 подключен к входу переноса 7 устройства, выходы суммы и переноса блока 2 подключены соответственно к первой 8 и втогэой 9 шинам результата устройства. Выход переноса блока 1 в i -м разряде , ройсТВ подключен к входу первого слагаемого блока 2 в (if +)-м разряде устройства. . Двоичное кодирование цифр для операндов устройства задано в табл.1. Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для параллельного алгебраического сложения в знакоразрядной системе счисления | 1981 |

|

SU1003074A1 |

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| КОМБИНАЦИОННЫЙ СУММАТОР СТРУКТУРНЫХ КОДОВ | 1991 |

|

RU2023288C1 |

| СПОСОБ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1997 |

|

RU2109325C1 |

| Устройство для сложения в избыточной двоичной системе счисления | 1986 |

|

SU1381487A1 |

| Комбинационный сумматор | 1986 |

|

SU1327092A1 |

| Комбинационный сумматор | 1987 |

|

SU1442988A1 |

| Устройство для сложения чисел в избыточной системе счисления | 1978 |

|

SU763896A1 |

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| Последовательное устройство для сложения в избыточной двоичной системе счисления | 1980 |

|

SU968807A1 |

Двоичные кодовые комбинации двухрядного кода При таком кодировании число в избыточной двоичной системе счисления I разбивается на положительную и отрицательную части представл енные обратным двоичным кодом без знакового разряда). . Работа устройства для алгебраического сложения двух чисел в избыточ ной двоичной системе (алгебраического сложения :двухчисел счисления, представленных«четырьмя слагаемыми в обратном двоичном коде, состоит в алгебг.зическом преобразовании трех слагаемых а два на одноразрядном двоичном .сумматоре,. Оставшееся четвертое слагаемое, слагаемое, полученное на выходах суммы блока 1, и слагаемое со сдвигом на один старший разряд, полученное на выходах переноса блока 1, подаются на входы блока 2 для алгебраического преобразования этих трех слагаемых в два. Слагаемое, по .лученное на выходс1Х суммы блока 2f |И слагаемое, со сдвигом на один .полученное на выходах переноса блока 2, образуют положительную и отри1 атеЛьную части результата сложе ния в избыточной двоичной системе счисления и подаются на-шины результата устройства. Устранение систематической погрешности устройства при приближенных вычислениях обеспечивается инвариантностыо устройства к инверсии двоичного, гпредставления операндов, кодированием цифр противоположного знака инверсными кодовыми комбинациями и равновероятностью последних в каждом разряде представления операндов. Представление операнда двухряд-Двоичные кодовые комбинации двухрядного кода операнда в рассматриваемом разряде

Положительный эффект упрощения 25 устройства состоит в том, что каждый разряд состоит из двух широко применяемых в вычислительной технике одног разрядных двоичных сумматоров, структурно организованных в дерево сумма- 30 торов. Поэтому время сложения и, затраты оборудования на один разряд равны удвоенным соотве тствующим параметрам одноразрядного двоичного сумматора и в среднем в 2,5 раза меньше, чем у из- 5 вестного. В отличие от известного . приближенные вычисления на данном устройстве лишены систематической погрешности. Даже в широко применяемой обычной двоичной системе счисления устранение систематической погрешност / связано с усложнением округления и приводит к выделению округления в отдельную операцию для обеспечения строгой несмещенности (ноль матема- . тического ожидания jпогрешности. 45

Формула изобретения

Устройство для алгебраического сложения в избыточной двоичной системе счисления, содержащее в каждом разряде блоки формирования сумглы и переноса первого каскада и блоки фомирования суммы и переноса второго каскада, отличающееся тем, что, с целью упрощения устройства, повыления его быстродействия

ным кодом, в котором все кодовые комбинации в том числе инверсные равновероятны в каждом разряде, может быть получено и обратного двоичного кода операнда поразрядным преобразованием, представленным в табл.2,

Таблица 2

и устранения систематической погрешности, блоки формирования суммы и переноса в каждом каскаде выполнены в виде одноразрядных двоичных сумматоров, причем входы одноразрядного двоичного сумматора первого каскада и первый вход одноразрядного двоичного сумматора второго каскада подключены к шинам соответствующего разряда слагаемых устройств, выход суммы одноразрядного двоичного сумматора первого каскада соединен с вторым входом одноразрядного двоичного сумматора второго каскада, выход переноса одноразрядного двоич;ного сумматора первого каскада соедНен с третьим входом одноразрядного ;Цвоичного сумматора -второго каскада Последующего разряда, выход одноразрядного двоичного сумматора второго каскада данного разряда и выход переноса одноразрядного двоичного сумматора второго касжада предыдущего разряда являются выходагми данного разряда устройства.

Источники информации, принятые во внимание при экспертизе

оJ

/.

/

/

Авторы

Даты

1983-03-07—Публикация

1981-02-20—Подача