1

Изобретение относится к области вычислительной техники и предназначено для применения в запоминающих устройствах со стековой организацией, входящих в состав процессора. 5

Известно устройство стековой адресации, содержащее один регистр указателя позиции стека{|1 . Недостатком такого устройства явля- tO ется неполное использование объема стековой памяти или избыточные временные затраты на операции откачки и подкачки нижних позиций стека изза зафиксированного в оборудовании j значения начального ащреса нижней позиции стека (он равен нулю).

Наиболее близким к изобретению является устройство .стековой адре- 20 сации содержащее два регистра указателей, хранящих абсолютные адреса верхней и нижней .позиций области стека с достоверной информацией, две схемы сравнения для определения 25 уровня заполнения стекового запомина,ющего устройства объемом М, анализирующие значения регистров указателей, и схему фиксации момента совпадения значений указателей 30

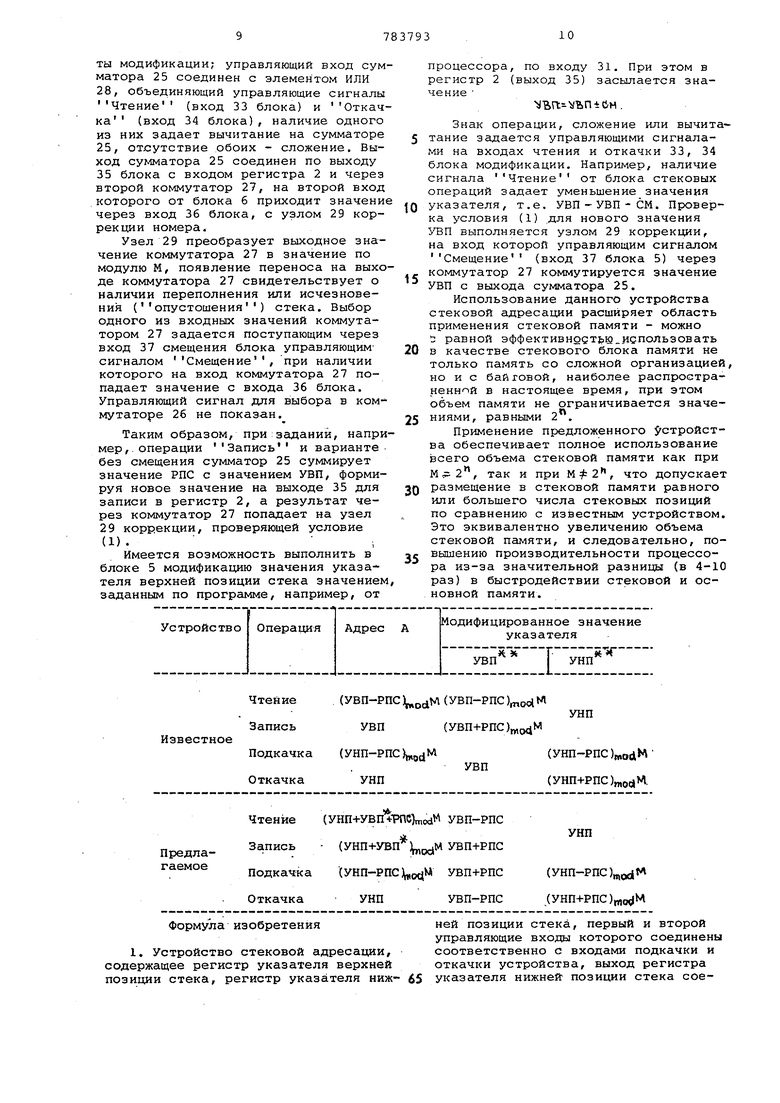

Форму.лы для вычисления адресов и значений указателей в зависимости от типа операции сведены в таблицу.

В таблице используются следующие обозначения: А - абсолютный адрес начала текущей позиции стека; УВП старое значение указателя верхней позиции стека; модифицированное значение указателя верхней позиции стека; УНП - старое значение указателя нижней позиции стека; УНП модифицированное значение указателя нижней позиции стека; РПС - размер позиции стека.

Недостатки этого устройства состоят в том, что область применения ограничена только памятью:со словной организацией и в понижении производительности при работе процессора со стековыми данными переменной длины. Они возникают из-за того, что ;операц1Ги чтения и зиписи стековых данный производятся лишь над словами фиксированной длины, а размер позиции стека неизменен и задан в аппаратуре.

Цель изобретения - повышение производительности устройства.

Для достижения указанной цели в устройство стековой адресации, содержащее регистр указателя верхней позиции стека, регистр указателя нижней позиции стека, первый и второй управляющие входы которого соединены соответственно с входами подкачки и откачки устройства, выход регистра указателя нижней позиции стека соединен с первым входом узла модификации, введены адресный; сумматор, блок модификации позиции стека, блок формирования номера позиции, регистр размера позиции стека, Первый и второй узлы коррекции, при ем вход данных первого узла коррекции соединен с выходом узла модифи ации, а выход данных первого узла «оррекции - с входом данных регистра указателя нижней пози1 и стека. Первый вход сщресного сумматора Соединен с выходом- регистра указателя нижней позиции стека, второй вход адресного сумматора - с выходом блока формирования номера Позиции и первым входом данных блока модификации позиции стека, а выход адресного сумматора соединен через второй узел коррекции с адресным выходом устройства. Выход регистра указателя верхней позиции стека соединен с первым входом данных блока формирования номера позиции и вторым входом данных блока модификации :Позиции стека, выход данных которо:го соединен с входом данных регистра указателя верхней позиции стека. Вхо:ды -генерации первого и второго узлов коррекции соединены с входом генерации устройства, вход данных которого соединен с третьим входом данных блока модификации позиции стека, вторым входом данных блока формирования номера позиции и входом Сданных регистра размера позиции стека , выход которого соединен с третьч им входом данных блока формирования номера позиции, вторым входом узла модификации и четвертым входом данных блока модификации позиции стека. Входы чтения блока модификации позиции стека и блока формирования номера позиции соединены с входом чтения устройства, вход откачки блока модификации позиции стека соединен с входом откачки и устройства, вход смещения блока модификации позиции стека соединен с входами смещения блока формирования номера позиции и устройства, а управляющий выход блока модификации с управляющим выходом устройства. Вход записи блока формирования номера позиции соединен с входом записи устройства, вход подкачки блока формирования номера позиции соединен с входом подкачки устройства.

Блок формирования номера позиции содержит два элемента ИЛИ, три элемента И, два вычитателя, причем первый и второй входы первого элемента ИЛИ соединены соответственно с входами чтения .и записи блока, выход первого элемента ИЛИ - с первым входом первого элемента И, второй вход которого соединен с первым входом данных блока, а выход первого элемента И - с первым входом первого вычитателя, первый и второй входы второго элемента ИЛИ соединены соответственно с входами блока чтения и подкачки, выход второго элемента ИЛИ - с первым входом второго элемента И,

второй вход которого соединен с третьим входом данных блока, а выход второго элемента И - с вторым входом первого вычитателя, выход которого соединен с первым входом второго вычитателя, первый и второй входы третьего элемента И соединены соответственно с вторым входом данных и входом смещения блока, а выход третьего элемента И - с вторым входом

второго вычитателя, выход которого соединен с выходом блока.

Блок модификации позиции стека содержит сумматор, два коммутатора, элемент ИЛИ и узел коррекции номера, причем первый вход данных сумматора соединен с вторым входом данных блока, второй вход данных сумматора - с выходом первого коммутатора, первый и второй входы которого соединены соответственно с третьим и четвертым входами данных блока. Управляю ций вход сумматора . соединен с выходом элемента ИЛИ, первый и второй входы которого соединены соответственно с входами чтения и откачки блока. Выход сумматора соединен с выходом данных блока и первым входом данных второго коммутатора, второй вход данных которого соединен с первым входом данных

блока, управляющий вход второго коммутатора - с входом смещения блока, а выход соединен через узел коррекции номера с управлякишм выходом блока,

Первый и второй узлы коррекции содержат вычитатель, сумматор и коммутатор, причем вход левого операнда сумматора соединен с входом правого операнда вычитателя, с первым.

входом коммутатора и входом данных узла коррекции, вход левого операнда вычитателя и вход правого операнда сумматора соединены с входом генерации узла коррекции, выход сумматора соединен с выходом данных

узла коррекции.

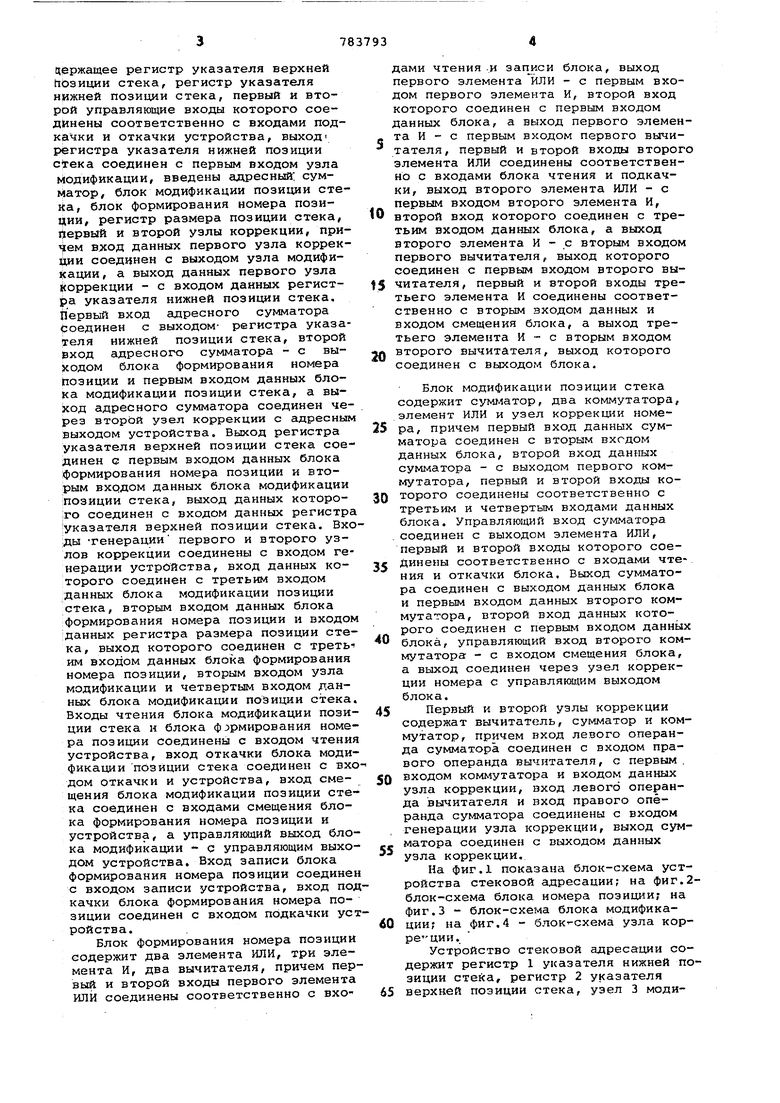

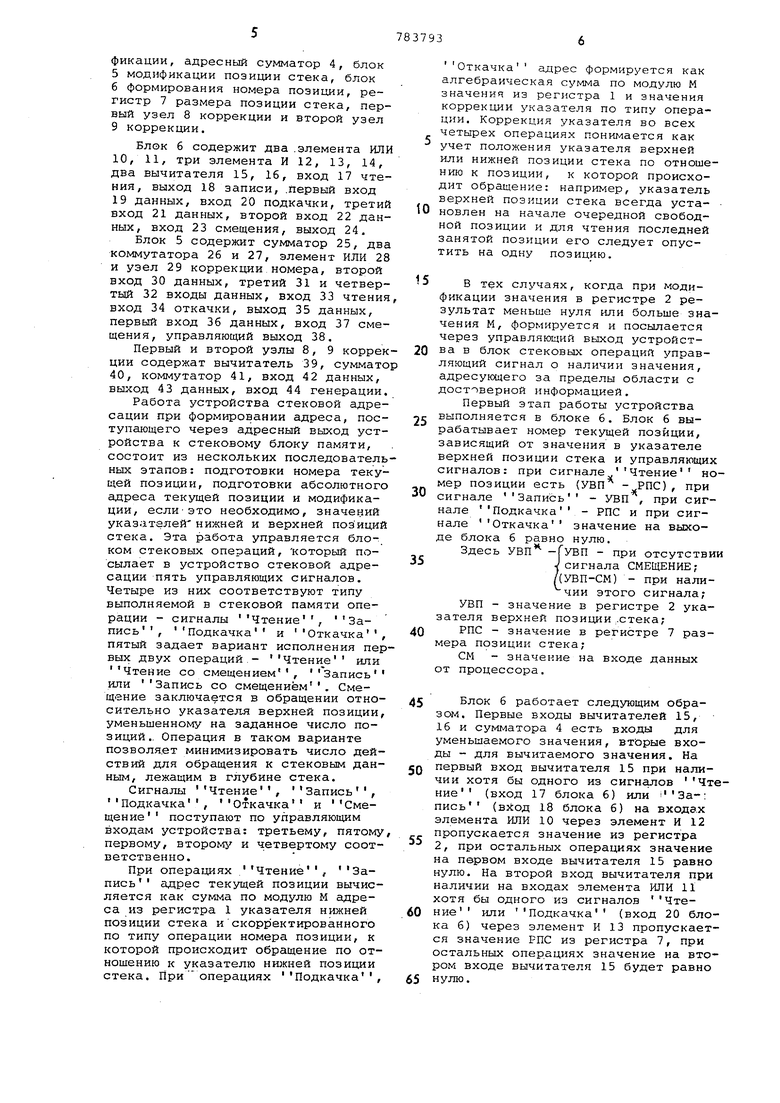

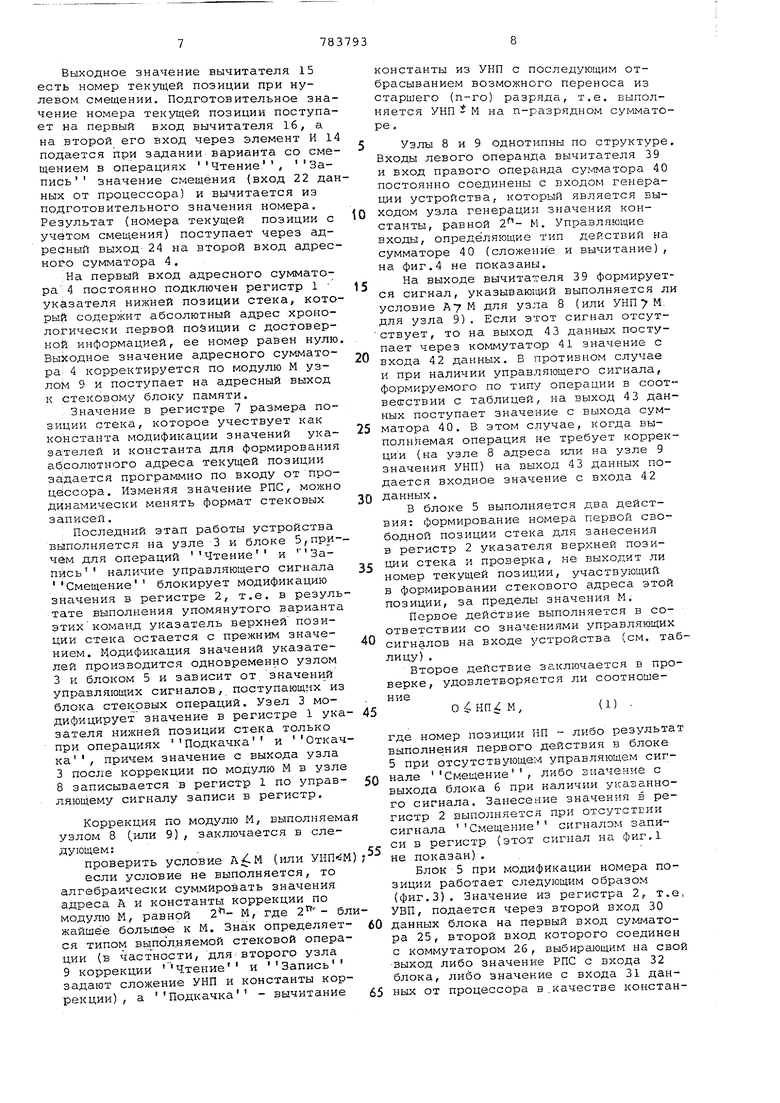

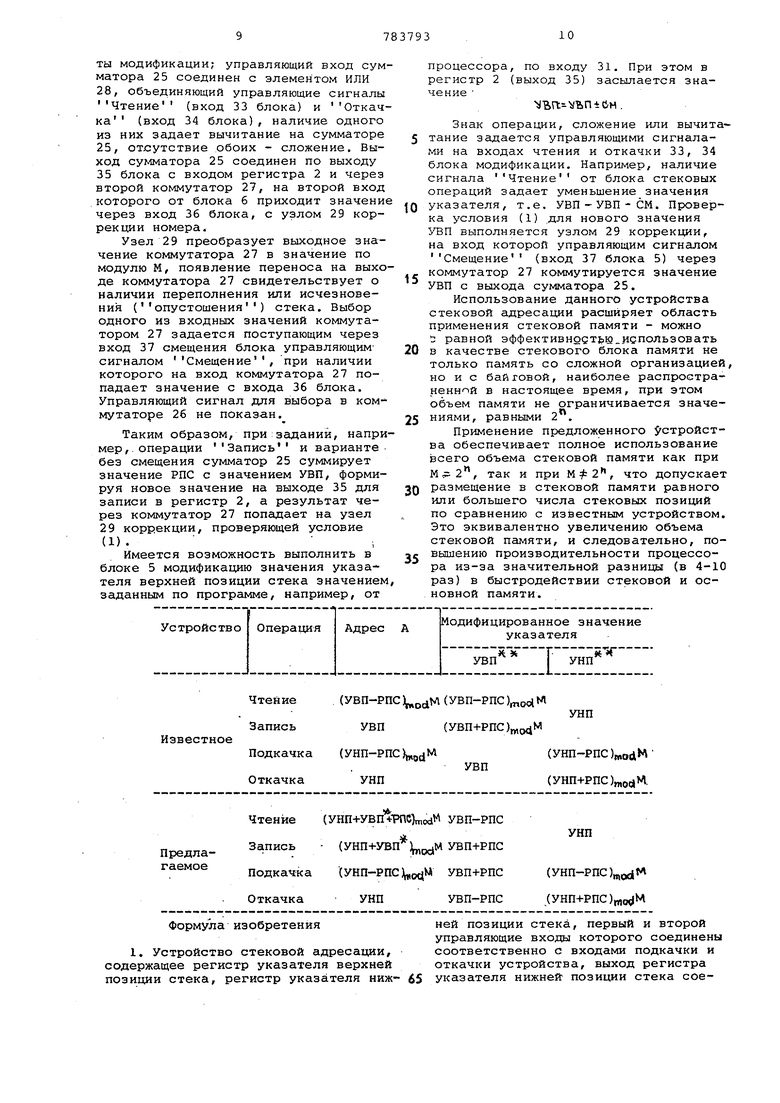

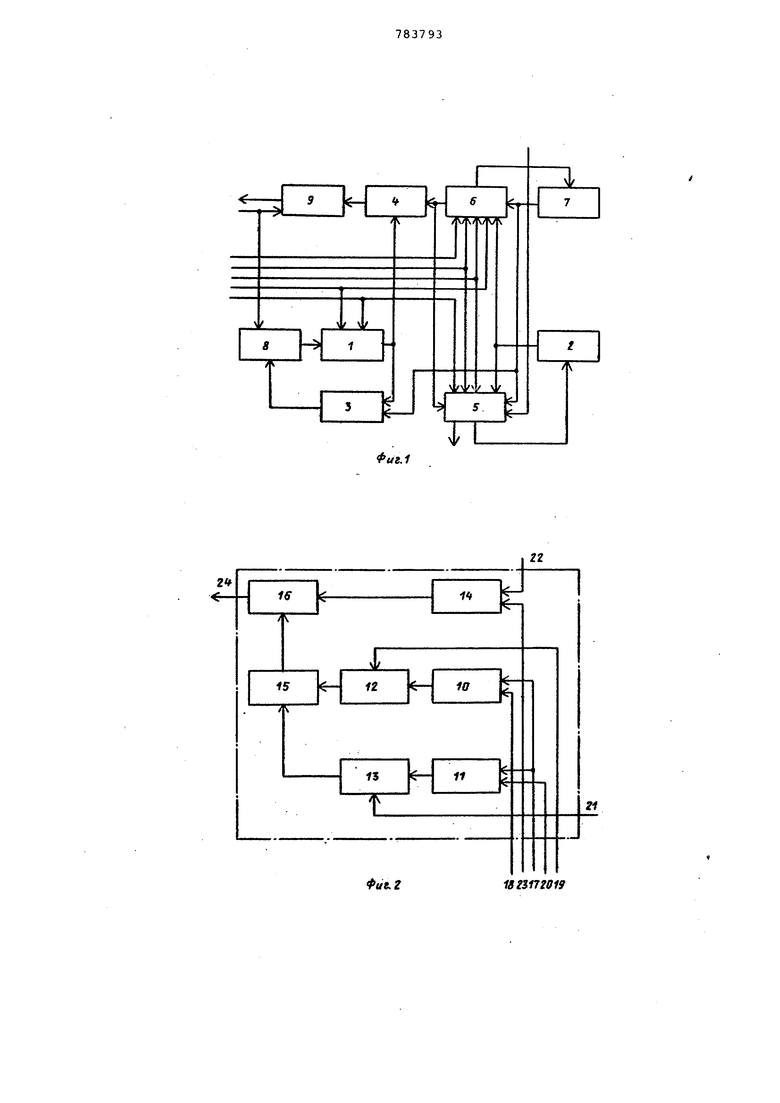

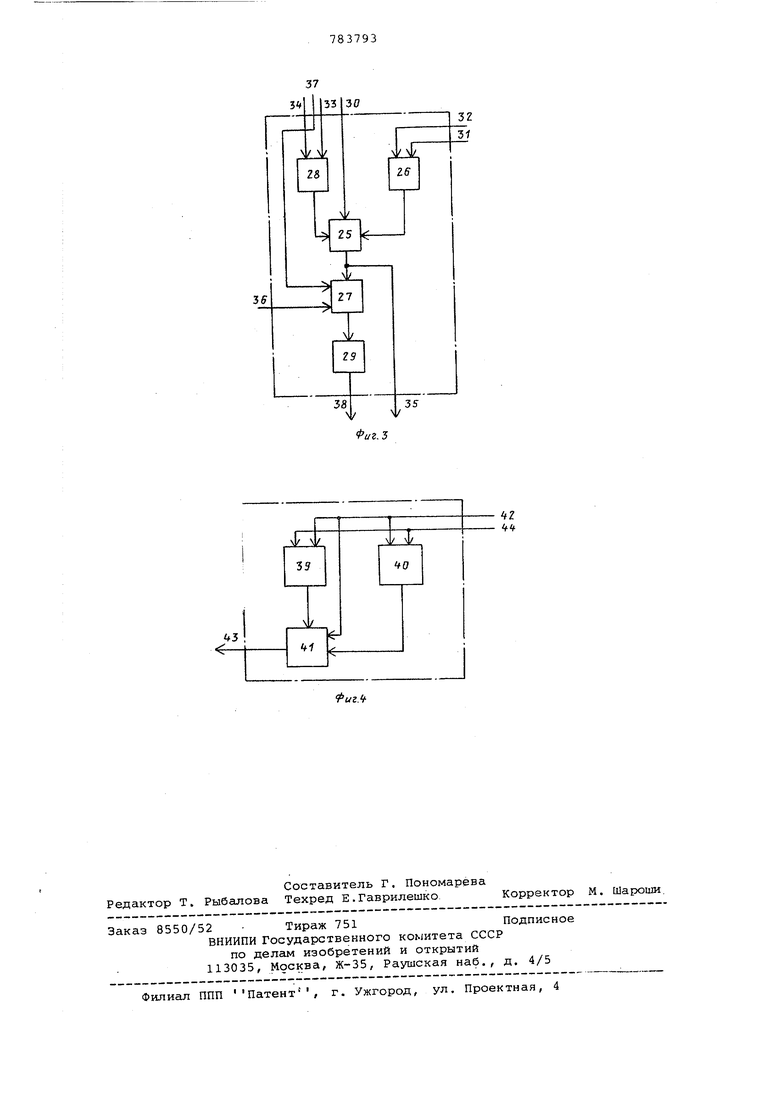

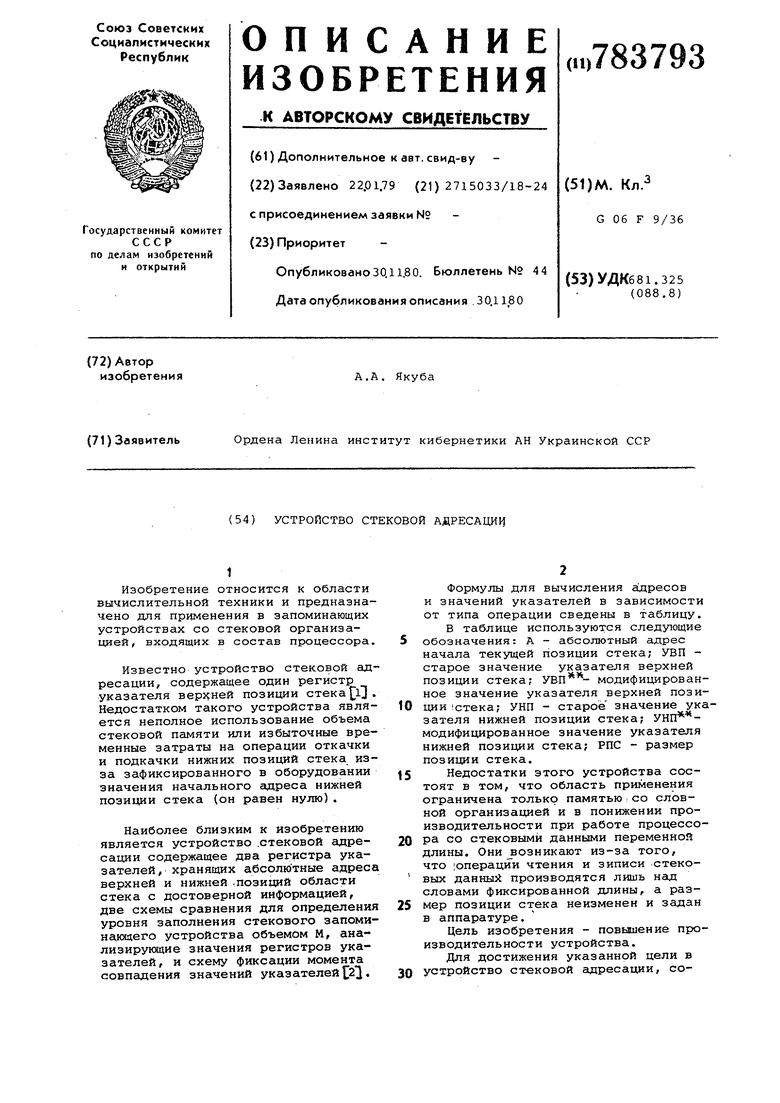

На фиг.1 показана блок-схема устройства стековой адресации; на фиг.2блок-схема блока номера позиции; на фиг.З - блок-схема блока модификации; на фиг,4 - блок-схема узла корре ции.

Устройство стековой адресации содержит регистр 1 указателя нижней позиции стека, регистр 2 указателя

верхней позиции стека, узел 3 модификации, адресный сумматор 4, блок

5модификации позиции стека, блок

6формирования номера позиции, регистр 7 размера позиции стека, первый узел 8 коррекции и второй узел 9 коррекции.

Блок 6 содержит два .элемента ИЛИ 10, 11, три элемента И 12, 13, 14, два вычитателя 15, 16, вход 17 чтения, выход 18 записи, .первый вход 19 данных, вход 20 подкачки, третий вход 21 данных, второй вход 22 данных, вход 23 смещения, выход 24.

Блок 5 содержит сумматор 25, два коммутатора 26 и 27, элемент ИЛИ 28 и узел 29 коррекции номера, второй вход 30 данных, третий 31 и четвертый 32 входы данных, вход 33 чтения вход 34 откачки, выход 35 данных, первый вход 36 данных, вход 37 смещения, управляющий выход 38.

Первый и второй узлы 8, 9 коррекции содержат вычитатель 39, суммато 40, коммутатор 41, вход 42 данных, выход 43 данных, вход 44 генерации.

Работа устройства стековой адресации при формировании адреса, поступающего через адресный выход устройства к стековому блоку памяти, состоит из нескольких последовательных этапов: подготовки номера текущей позиции, подготовки абсолютного адреса текущей позиции и модификации, если-это необходимо, значений указателей нижней и верхней позиций стека. Эта работа управляется блоком стековых операций, который посылает в устройство стековой адресации пять управляющих сигналов. Четыре из них соответствуют типу выполняемой в стековой памяти операции - сигналы Чтение

Запись, Подкачка и Откачка, пятый задает вариант исполнения перЧтение или

вых двух операций I I

Чтение со смещением , Запись

или Запись со смещением

щение заключается в обращении относительно указателя верхней позиции, уменьшенному на заданное число позиций., Операция в таком варианте позволя.ет минимизировать число действий для обращения к стековым данным, лежащим в глубине стека.

Сигналы Чтение, Запись,

Подкачка, Откачка

и

щение поступают по управляющим входам устройства: третьему, пятому первому, второму и четвертому соответственно.

При операциях Чтение, Запись адрес текущей позиции вычисляется как сумма по модулю М адреса из регистра 1 указателя нижней позиции стека и скорректированного по типу операции номера позиции, к которой происходит обращение по отнощению к указателю нижней позиции стека. При операциях Подкачка,

Откачка адрес формируется как алгебраическая сумма по модулю М значения из регистра 1 и значения коррекции указателя по типу операции. Коррекция указателя во всех четырех операциях пониг ается как учет положения указателя верхней или нижней позиции стека по отношению к позиции, к которой происходит обращение: например, указатель верхней позиции стека всегда уста-

0 новлен на начале очередной свободной позиции и для чтения последней занятой позиции его следует опустить на одну позицию.

5

В тех случаях, когда при модификации значения в регистре 2 результат меньше нуля или больше значения М, формируется и посылается через управляющий выход устройст0ва в блок стековых операций управляющий сигнал о наличии значения, адресующего за пределы области с дост верной информацией.

Первый этап работы устройства выполняется в блоке 6. Блок 6 вы5рабатывает номер текущей позиции, зависящий от значения в указателе верхней позиции стека и управляющих

Чтение

сигналов: при сигнале.

номер позиции есть (УВП - РПС), при сигнале Запись - УВП , при сигнале Подкачка - РПС и при сигнале Откачка значение на выходе блока 6 равно нулю.

Здесь -ГУВП - при отсутствии сигнала СМЕЩЕНИЕ; (УВП-СМ) - при налирчии этого сигнала;

УВП - значение в регистре 2 указателя верхней позиции ,.стека;

РПС - значение в регистре 7 размера позиции стека;

СМ - значение на входе данных от процессора.

СмеБлок 6 работает следующим образом. Первые входы вычитателей 15, 16 и сумматора 4 есть входы для уменьшаемого значения, вторые входы - для вычитаемого значения. На первый вход вычитателя 15 при наличии хотя бы одного из сигналов Чтение (вход 17 блока 6) или i3a-:

Смепись ( 18 блока 6) на входах элемента ИЛИ 10 через элемент И 12 пропускается значение из регистра 2, при остальных операциях значение на первом входе вычитателя 15 равно нулю. На второй вход вычитателя при наличии на входах элемента ИЛИ 11 хотя бы одного из сигналов Чтение или Подкачка (вход 20 блока 6) через элемент И 13 пропускается значение РПС из регистра 7, при остальных операциях значение на втором входе вычитателя 15 будет равно

нулю. Выходное значение вычитателя 15 есть номер текущей позиции при нулевом смещении. Подготовительное зна чение номера текущей позиции поступа ет на первый вход вычитателя 16, а на второй его вход через элемент И 1 подается при задании варианта со сме Чтение щением в операциях пись значение смещения (вход 22 да ных от процессора) и вычитается из подготовительного значения номера,. Результат (номера текущей позиции с учетом смещения) поступает через адресный выход 24 на второй вход адрес ного сумматора 4, На первый вход адресного сумматора 4 постоянно подключен регистр 1 указателя нижней позиции стека, кото рый содержит абсолютный адрес хронологически первой пойиции с достоверной информацией, ее номер равен нулю Выходное значение адресного сумматора 4 корректируется по модулю М узлом 9 и поступает на адресный выход к стековому блоку памяти. Значение в регистре 7 размера позиции стека, которое учествует как константа модификации значений указателей и константа для формирования абсолютного адреса текущей позиции задается программно по входу от процессора. Изменяя значение РПС, можно динамически менять формат стековых записей. Последний этап работы устройства выполняется на узле 3 и блоке 5,причам для операций Чтение и Запись наличие управляющего сигнала Смещение блокирует модификацию значения в регистре 2, т.е. в резуль тате выполнения упомянутого варианта этихкоманд указатель верхней позиции стека остается с прежним значением. Модификация значений указателей производится одновременно узлом 3 и блоком 5 и зависит от значений управляющих сигналов, поступающих из блока стековых операций. Узел 3 модифицирует значение в регистре 1 ука зателя нижней позиции стека только при операциях Подкачка и Откач ка , причем значение с выхода узла 3 после коррекции по модулю М в узле 8записывается в регистр 1 по управляющему сигналу записи в регистр. Коррекция по модулю М, выполняема узлом 8 (.или 9) , заключается в следующем: , проверить условие (или если условие не выполняется, то алгебраически суммировать значения адреса А и константы коррекции по модулю М, равной М, где бл жайшее большее к М, Знак определяется типом выполняемой стековой операции (в частности, длявторого узла 9коррекции Чтение и Запись задают сложение УНП и константы коррекции) , а Подкачка - вычитание константы из УНП с последующим отбрасыванием возможного переноса из старшего (п-го) разряда, т.е. выполняется УНП М на п-разрядном сумматоре. Узлы 8 и 9 однотипны по структуре. Входы левого операнда вычитателя 39 и вход правого операнда су матора 40 постоянно соединены с входом генерации устройства, который является выходом узла генерации значения константы, равной 2- Н. Управляющие входы, определяющие тип действий на сумматоре 40 (сложение и вычитание), на фиг.4 не показаны. На выходе вычитателя 39 формируется сигнал, указываю1ций выполняется ли условие А7 М для узла 8 (или УНП7 М. для узла 9). Если этот сигнал отсутствует, то на выход 43 данных поступает через коммутатор 41 значение с входа 42 данных. В противном случае и при наличии управляющего сигнала, формируемого по типу операции в соответствии с таблицей, на выход 43 данных поступает значение с выхода сумматора 40. В этом случае, когда выполн емая операция не требует коррекции (на узле В адреса или на узле 9 значения УНП) на выход 43 данных подается входное значение с входа 42 данных. В блоке 5 выполняется два действия; формирование номера первой свободной позиции стека для занесения в регистр 2 указателя верхней позиции стека и проверка, не выходит ли номер текущей позиции, участвуюдий в формировании стекового адреса этой позиции, за пределы значения М, Первое действие выполняется в соответствии со значениями управляющих сигналов на входе устройства (см, таблицу) , Второе действие заключается в проверке, удовлетворяется ли соотношениеО НП М, (1) где номер позиции НП либо результат выполнения первого действия в блоке 5 при отсутствующем управляющем сигнале Смещение, либо значение с выхода блока б при наличии указанного сигнала. Занесение значения в регистр 2 выполняется при отсутствии сигнала Смещение сигналом 3an5iси в регистр (этот сигнал на фиг.1 не показан). Блок 5 при модификации номера позиции работает следующим образом (фиг.З). Значение из регистра 2, т.е. УВП, подается через второй вход 30 данных блока на первый вход сумматора 25, второй вход которого соединен с коммутатором 26, выбирающим на свой выход либо значение РПС с входа 32 блока, либо значение с входа 31 данных от процессора в .качестве константы модификации; управляющий вход сумматора 25 соединен с элементом ИЛИ 28, объединяющий управляющие сигналы Чтение (вход 33 блока) и Откачка (вход 34 блока), наличие одного из них задает вычитание на сумматоре 25, отсутствие обоих - сложение. Выход сумматора 25 соединен по выходу 35 блока с входом регистра 2 и через второй коммутатор 27, на второй вход которого от блока б приходит значени через вход 36 блока, с узлом 29 коррекции номера.

Узел 29 преобразует выходное значение коммутатора 27 в значение по модулю М, появление переноса на выходе коммутатора 27 свидетельствует о наличии переполнения или исчезнове(опустошения) стека. Выбор

ния

одного из входных значений коммутатором 27 задается поступающим через вход 37 смещения блока управляющимсигналом Смещение, при наличии которого на вход коммутатора 27 попадает значение с входа 36 блока. Управляющий сигнал для выбора в коммутаторе 26 не показ-ан.

Таким образом, при задании, например ,. операции Запись и варианте без смещения сумматор 25 суммирует значение РПС с значением УВП, формируя новое значение на выходе 35 для записи в регистр 2, а результат через коммутатор 27 попадает на узел 29 коррекции, проверяющей условие (1).

Имеется возможность выполнить в блоке 5 модификацию значения указателя верхней позиции стека значением заданным по программе, например, от

процессора, по входу 31. При этом в регистр 2 (выход 35) засылается значение

Jurt-vun CH.

Знак операции, сложение или вычитатание задается управляющими сигналами на входах чтения и откачки 33, 34 блока модификации. Например, наличие сигнала Чтение от блока стековых операций задает уменьшение значения указателя, т.е. УВП-УВП-СМ. Проверка условия (1) для нового значения УВП выполняется узлом 29 коррекции, на вход которой управляющим сигналом Смещение (вход 37 блока 5) через коммутатор 27 коммутируется значение

5 УВП с выхода сумматора 25.

Использование данного устройства стековой адресации расширяет область применения стековой памяти - можно ;: равной эффективнодтьи идпользовать

0 в качестве стекового блока памяти не только память со сложной организацией, но и с байтовой, наиболее распространенной в настоящее время, при этом объем памяти не ограничивается значениями, равными 2 .

5

Применение предложенного стройства обеспечивает полное использование всего объема стековой памяти как при , так и при , что допускает размещение в стековой памяти равного

0 или большего числа стековых позиций по сравнению с известным устройством. Это эквивалентно увеличению объема стековой памяти, и следовательно, повышению производительности процессо5ра из-за значительной разницы (в 4-10 раз) в быстродействии стековой и основной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор микропрограмируемой ЭВМ | 1989 |

|

SU1697082A1 |

| Устройство стековой адресации | 1988 |

|

SU1513447A2 |

| Процессор микропрограммируемой ЭВМ | 1979 |

|

SU860077A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство для управления параллельным выполнением команд в стековой электронной вычислительной машине | 1976 |

|

SU556440A1 |

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

| ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2028665C1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для формирования динамических изображений из связок векторов | 1985 |

|

SU1339626A1 |

| Система для трансляции с проблемноориентированного языка | 1976 |

|

SU674028A1 |

Чтение (УНП+УВП РПС)т«1М УВП-РПС Запись - (УНП+УВП : р М УВП+РПС Подкачка (УНП-РПС1 о {М УВП+РПС Откачка УНП УВП-РПС Формула изобретения 1. Устройство стековой адресации, содержащее регистр указателя верхней позиции стека, регистр указателя ниж- 65

УНП

(УНП-РПС)адоо1 (УНП+РПС)„о ней позиции стека, первый и второй управляющие входы которого соединены соответственно с входами подкачки и откачки устройства, выход регистра указателя нижней- позиции стека соединен с первым входом узла модификации, отличайщеес я тем, что, с целью повышения производительности устройства, S него введены адресный сумматор, блок модификации позиции стека, блок формирования номера позиции, регистр размера позиции стека, первый и второй узлы коррекции, причем вход данных первого узла коррекции соединен с выходом уйла модификации, а выход данных первого узла коррекции с входом данных регистра указателя нижней позиции ств ка, первый вход адресного сумматора соединен с выходом регистра указателя нижней позиции стека, второй вход адресного сумматора - с выходом блока формирования номера позиции и первым входом данных блока модификации позиции стека, а выход адресного сумматора соединен через второй узел коррек ции с адресным выходом устройства, выход регистра указателя верхней позИции стека соединен с первым входом данных блока формирования номера позиции и вторым входом данных блока модификации позиции стека, выход данных которого соединен с входом данных регистра указателя верхней позиции , входы генерации первого и вто рого узлов коррекции соединены с вхо дом генерации устройства, вход данных которого соединен с третьим входом данных блока модификации позиции стека, вторым входом данных блока формирования номера позиции и входом данных регистра размера позиции стек выход которого соединен с третьим вх дом данных блока формирования номера позиции, вторым входом узла модифика ции и четвертым входом данных блока модификации позиции стека, входы чте ния блока модификации позиции стека и блока формирования номера позиции соединены с входом чтения устройства вход откачки блока модификации позиции стека соединен с входом откачки устройства, вход смещения блока модификации позиции стека соединен с входами смещения блока фop viиpoвaния номера .позиции и устройства, а управ ляющий выход блока модификации - с управляю1дим выходом устройства, вход записи блока формирования номера позиции соединен с входом записи устройства, вход подкачки блока формирования номера позиции соединен с входом подкачки устройства. 2. Устройство по П.1, о т л и чающееся тем, что блок формйрбвания номера позиции содержит дв элемента ИЛИ, три элемента И, два вычитателя, причем первый и второй входы первого элемента ИЛИ соединены соответственно с входами чтения и за писи блока, выход первого элемента ИЛИ - .с первым входом первого элемен та И, второй вход которого соединен с первым входом данных блока, а выход первого элемента И - с первым входом первого вынитателя, первый и второй входы второго элемента ИЛИ соединены соответственно с входами чтения и подкачки блока, выход второго элемента ИЛИ - с первым входом второго элемента И, второй вход которого соединен с третьим входом данных блока, а выход второго элемента И - о вторым входом первого вы штaтеля, выход которого соединен с первым входом второго вычитателя, первый и второй входы третьего элемента И соединены соответственно с вторыгвходом данных и входом смещения блока, а выход Третьего элемента И - с вторыг входом второго вычитателя, выход которого соединен с выходом блока, 3.Устройство по п.1, о т л и чающееся тем, что блок модификации позиции стека содержит сум.матор, два коммутатора, элемент ИЛИ и узел коррекции номера, причем первый вход данных сумматора соединен с в торЫхМ входом данных блока, второй вход даннлх сумг-латора - с выходом первого коммутатора, первый и второй входы которого соединены cooTBeTCTBeHtio с третьим и четвертьтм входами данных блока, управляющий вход сумматора соединен с выходок элемента ИЛИ, первый и второй входы которого соединены соответственно с входалш чтения и откачки блока,выход сумматора соединен с выходом данных блока и первьпи входом данных второго коммутатора, второй вход данных которого соединен с первым входом данных блока, управляющий вход второго коммутатора - с входом смещения блока, а выход второго коммутатора соединен через узел коррек7 ции номера с управляющим выходом блока. 4,Устройство по п.1, о т л и мающееся тем, что первый и второй узлы коррекции содержат вычитатель, cyrvSMaTop и ког-1мутатор, причем вход левого операнда сумматора соединен с входом правого операнда вычитателя, о первым входом коммутатора и входом данных узла коррекции, вход левого операнда вычитателя и вход правого операнда сумматсфа-соединены с входом генерации узла коррекции, выход cyNMaTOpa соединен с вторыг входом COMiviyTa.TOpa, выход которого соединен с выходог4 данных узла коррекции. Источники имформации, принятые во внимание при экспертизе изобретения 1.Патент США 3200379, кл. 340-172.5, 1965. 2,Патент США If 3810117, кл. 340-172,5, 1974 (прототип).

Put.Z

18ВГГг019

Авторы

Даты

1980-11-30—Публикация

1979-01-22—Подача