Изобретение относится к информационно-измерительной технике и может быть использовано при построении аналоговых и цифроаналоговых устройств для усреднения сигналов в анализато- pax, интегрирующих вольтметрах, а также в других устройствах, где при проведении операций интегрирования требуется точная начальная установка интегратора.

Цель изобретения - повышение точности интегрирования.

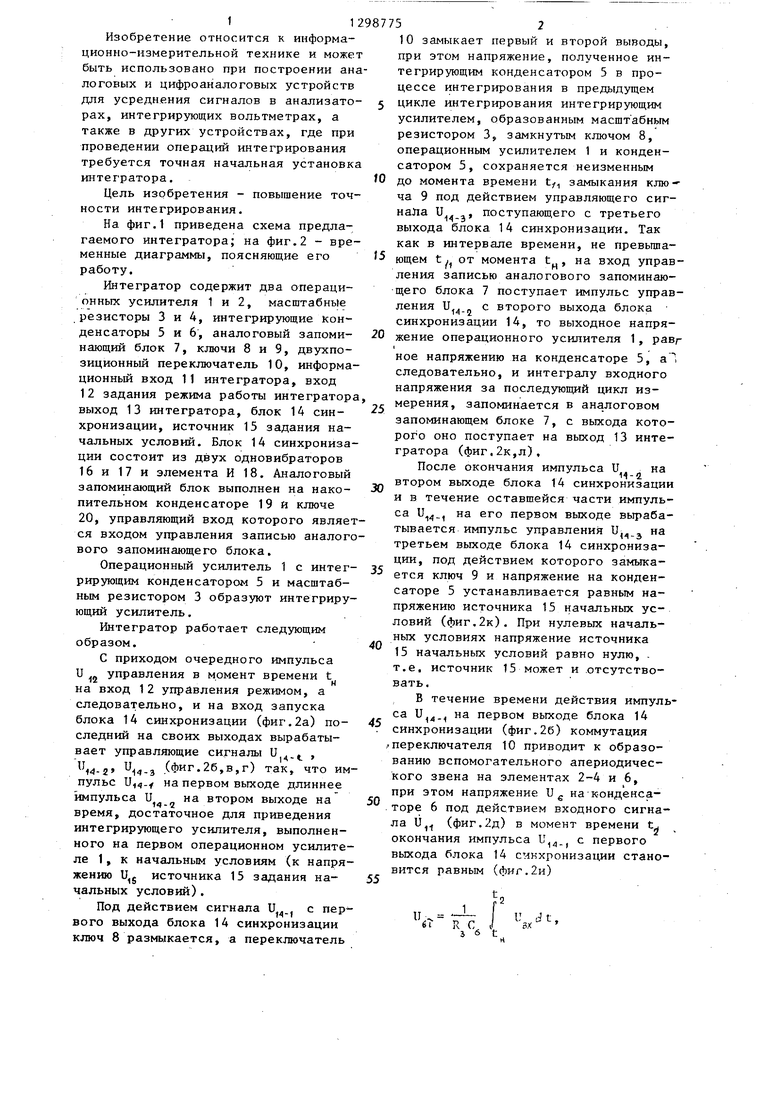

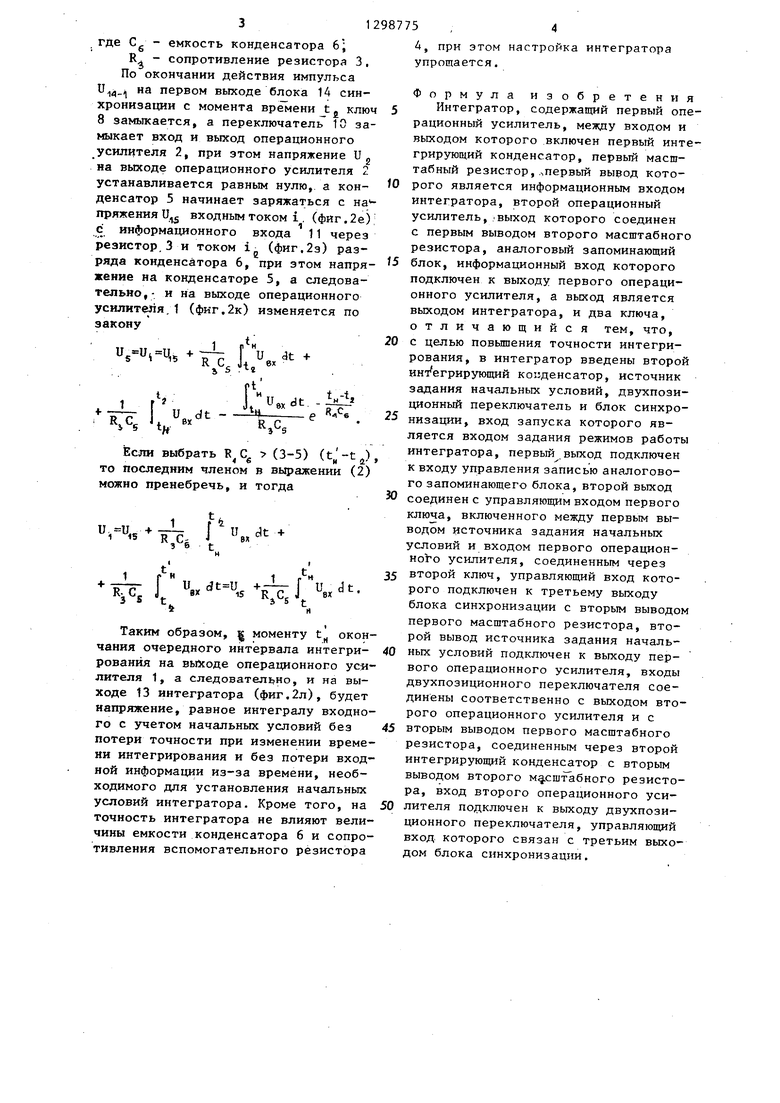

На фиг.1 приведена схема предлагаемого интегратора; на фиг.2 - временные диаграммы, поясняющие его работу.

Интегратор содержит два операционных усилителя 1 и 2, масштабные резисторы 3 и 4, интегрирующие Конденсаторы 5 и 6, аналоговый запоми- нающий блок 7, ключи 8 и 9, двухпо- зиционный переключатель 10, информационный вход 11 интегратора, вход 12 задания режима работы интегратора выход 13 интегратора, блок 14 син- хронизации, источник 15 задания начальных условий. Блок 14 синхронизации состоит из двух одновибраторов 16 и 17 и элемента И 18. Аналоговый запоминающий блок выполнен на нако- пительном конденсаторе 19 и ключе 20, управляющий вход которого является входом управления записью аналогового запоминающего блока.

Операционный усилитель 1 с интег- рирующим конденсатором 5 и масштабным резистором 3 образуют интегрирующий усилитель.

Интегратор работает следующим образом.

С приходом очередного импульса и 2 управления в момент времени t на вход 12 управления режимом, а следовательно, и на вход запуска блока 14 синхронизации (фиг.2а) по- следний на своих выходах вырабатывает управляющие сигналы U .,, , 4-2 (фиг.26,в,г) так, что импульс U,4-f на первом выходе длиннее импульса и на втором выходе на время, достаточное для приведения интегрирующего усилителя, выполненного на первом операционном усилителе 1 , к начальным условиям (к напряжению Ц источника 15 задания на- чальных условий).

Под действием сигнала U. с первого выхода блока 14 синхронизации ключ 8 размыкается, а переключатель

10 замыкает первый и второй выводы, при этом напряжение, полученное интегрирующим конденсатором 5 в процессе интегрирования в предыдущем цикле интегрирования интегрирующим усилителем, образованным масштабным резистором 3, замкнутым ключом 8, операционным усилителем 1 и конденсатором 5, сохраняется неизменным до момента времени t/, замыкания клю ча 9 под действием управляющего сигнала и, , поступающего с третьего выхода блока 14 синхронизации. Так как в интервале времени, не превышающем t от момента t, на вход управления записью аналогового запоминающего блока 7 поступает импульс управления и,.- с второго выхода блока синхронизации 14, то выходное напряжение операционного усилителя 1, рав

ное напряжению на конденсаторе 5, а следовательно, и интегралу входного напряжения за последующий цикл измерения, запоминается в аналоговом запоминающем блоке 7, с выхода которого оно поступает на выход 13 интегратора (фиг.2к,л).

После окончания импульса U на втором выходе блока 14 синхронизации и в течение оставшейся части импульса , на его первом выходе вырабатывается импульс управления U на третьем выходе блока 14 синхронизации, под действием которого замыкается ключ 9 и напряжение на конденсаторе 5 устанавливается равным напряжению источника 15 начальных условий (фиг,2к). При нулевых начальных условиях напряжение источника 15 начальных условий равно нулю, . т.е. источник 15 может и .отсутствовать.

В течение времени действия импульса и,д., на первом выходе блока 14 синхронизации (фиг.2б) коммутация переключателя 10 приводит к образованию вспомогательного апериодического звена на элементах 2-4 и 6, при этом напряжение U на конденсаторе 6 под действием входного сигнала и (фиг,2д) в момент времени t окончания импульса U. с первого выхода блока 14 смкхронизации становится равным (фиг.2и)

ь

I J 6 с

R - сопротивление резистора 3. По окончании действия импульса на первом выходе блока 14 синхронизации с момента времени Jig ключ 8 замыкается, а переключатель 10 замыкает вход и выход операционного усилителя 2, при этом напряжение Ug на выходе операционного усилителя 2 устанавливается равным нулю, а конденсатор 5 начинает заряжаться с пряжения и, входным током i , (фиг. 2е)

10

с информахщонного резистор,3 и током

входа 11 через ip (фиг.2з) разряда конденсатора 6, при этом напря- блок, информационный вход которого

упрощается.

Формула изобретени

Интегратор, содержащий первый о рационный усилитель, между входом выходом которого включен первый ин грирующий конденсатор, первый масш табный резистор,лпервый вывод кото рого является информационным входо интегратора, второй операционный усилитель, ВЫХОД которого соединен с первым выводом второго масштабно резистора, аналоговый запоминающий

блок, информационный вход которого

упрощается.

Формула изобретения

Интегратор, содержащий первый операционный усилитель, между входом и выходом которого включен первый интегрирующий конденсатор, первый масштабный резистор,лпервый вывод которого является информационным входом интегратора, второй операционный усилитель, ВЫХОД которого соединен с первым выводом второго масштабного резистора, аналоговый запоминающий

жение на конденсаторе 5, а следовательно,- и на выходе операционного усилителя.1 (фиг.2к) изменяется по закону

и

R С i S

dt г .

ft

и

20

3t +

ex

dt. Vb«л

R

25

подключен к выходу первого операционного усилителя, а выход является выходом интегратора, и два ключа, отличающийся тем, что, с целью повьшения точности интегрирования, в интегратор введены второй инт егрирующий конденсатор, источник задания начальных условий, двухпози- ционный переключатель и блок синхронизации, вход запуска которого является входом задания режимов работы интегратора, первьй выход подключен к входу управления записью аналогового запоминающего блока, второй выход соединен с управляющим входом первого ключа, включенного между первым выводом источника задания начальных условий и входом первого операционного усилителя, соединенным через второй ключ, управляющий вход которого подключен к третьему выходу блока синхронизации с вторым выводом первого масштабного резистора, второй вывод источника задания началь- чания очередного интервала интегри- 40 ных условий подключен к выходу перЁсли выбрать F С (3-5) (tj-t, то последним членом в выражении (2) можно пренебречь, и тогда

30

гЧв

1

Се

в,

ВХ 45

1 Г

R-Ж 1 в

dt,

35

Таким образом, моменту t оконрования на выходе операционного усилителя 1, а следовательно, и на выходе 13 интегратора (фиг.2л), будет напряжение, равное интегралу входного с учетом начальных условий без потери точности при изменении времени интегрирования и без потери входной информации из-за времени, необходимого для установления начальных условий интегратора. Кроме того, на точность интегратора не влияют величины емкости конденсатора 6 и сопротивления вспомогательного резистора

вого операционного усилителя, входы двухпозиционного переключателя соединены соответственно с выходом второго операционного усилителя и с вторым выводом первого масштабного резистора, соединенным через второй интегрирующий конденсатор с вторым выводом второго м§.сштабного резистора, вход второго операционного усилителя подключен к выходу двухпозиционного переключателя, управляющий вход которого связан с третьим выходом блока синхронизации.

S) .-1

.

д) Ujf

е) Lj w) ig

3) L

Ю u.

H t

Редактор Е.Папп

Составитель С,Белан

Техред Л.Сердюкова Корректор С.Шекмар

Заказ 891/52 Тираж 673 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113С35, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

// fl V /

Фа г. 2

с//

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор | 1986 |

|

SU1401485A2 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Времяимпульсный квадратичный преобразователь | 1986 |

|

SU1406610A1 |

| Интегратор | 1981 |

|

SU1029187A1 |

| Функциональный аналогоцифровой преобразователь | 1982 |

|

SU1072066A1 |

| Масштабный преобразователь напряжения и его варианты | 1980 |

|

SU922780A1 |

| Устройство для деления аналоговых сигналов | 1990 |

|

SU1795479A1 |

| Устройство для моделирования упругого гистерезиса | 1980 |

|

SU966708A1 |

| СПОСОБ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ ПРОИЗВОЛЬНОЙ ФОРМЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1990 |

|

RU2034302C1 |

| Интегратор | 1989 |

|

SU1764063A1 |

Изобретение относится к аналоговой информационно-измерительной технике и может быть .использовано при построении аналоговых и цифроана- логовых устройс;гв, в частности для усреднения сигналов в анализаторах, интегрирующих вольтметрах и т,д. Цель изобретения - повьшение точности интегрирования. Интегратор позволяет производить ввод начальных условий -без потери входной информации во время ввода начальных условий, независимо от изменений длительности следующих друг за другом циклов интегрирования, за счет введения вспомогательного интегратора, образованного операционным усилителем 2, в цепь обратной связи которого включены интегрирующий конденсатор 6 и последовательно соединенный с ним масштабный резистор 4, двухпозиционным переключателем 10, масштабным резистором 3, Вспомогательный интегратор подключают к информационному входу интегратора на время установки начальных условий основного интегрирующего усилителя, на операционном усилителе 1, с последующим переносом заряда с : интегрирующего конденсатора 6 на ин- тегрирзтощий конденсатор 5 основного интегрирующего усилителя путём коммутации ключей 8, 9 и переключателя 10, блока синхронизации 14. 2 ил. с 13 сл ю со оо vj СП

| Корн Г., Корн Т | |||

| Электронные аналоговые и аналого-цифровые вычислительные машины, - М | |||

| Приспособление для контроля движения | 1921 |

|

SU1968A1 |

| Алексеенко А.Г | |||

| и др | |||

| Применение прецизионных аналоговых ИС | |||

| - М | |||

| : Радио и связь, 1981, с.81, табл,3,2, | |||

Авторы

Даты

1987-03-23—Публикация

1985-10-21—Подача