(54) СИНТЕЗАТОР ЧАСТОТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1979 |

|

SU799150A1 |

| Синтезатор частот | 1986 |

|

SU1478328A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1993 |

|

RU2081510C1 |

| СИНТЕЗАТОР ЧАСТОТ | 1993 |

|

RU2085032C1 |

| СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2014733C1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1987 |

|

SU1543544A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1356222A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

1

Изобретение относится к радиотехнике и может использоваться в устройствах формирования сигналов с прыгающей частотой, а также в быстродействующих устройствах поиска сигналов.

Известен синтезатор частот, содержащий соединенные в кольцо перестраиваемый генератор, тракт преобразования частоты, фазовый детектор и сумматор, а также .последовательно соединенные блок управления и регистр памяти, выход которого соединен с установочным входом тракта преобразования частоты, опорный генератор, который подключен к другому входу фазового детектора 1.

Однако присущая этому устройству большая длительность переходных процессов увеличивает время установления частоты.

Цель изобретения - сокращение времени установления частоты выходного сигнала.

Для этого в синтезаторе частот, содержащем соединенные в кольцо перестраиваемый генератор, тракт преобразования частоты, фазовый детектор и сумматор, а также последовательно соединенные блок управления и регистр памяти, выход которого соединен с установочным входом тракта преобразования частоты, опорный генератор, который подключен к другому входу фазового детектора, между другим выходом блока управления и другим входом сумматора введен блок запоминающих устройств, другой вход которого соединен с выходом сумматора.

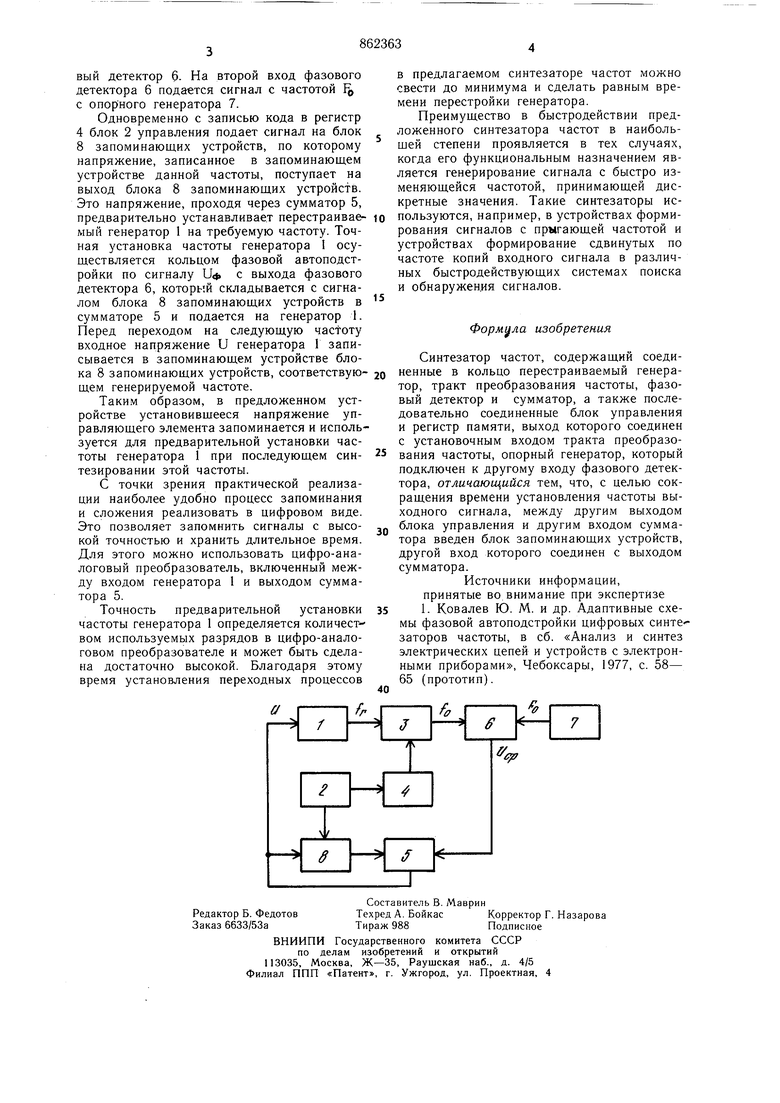

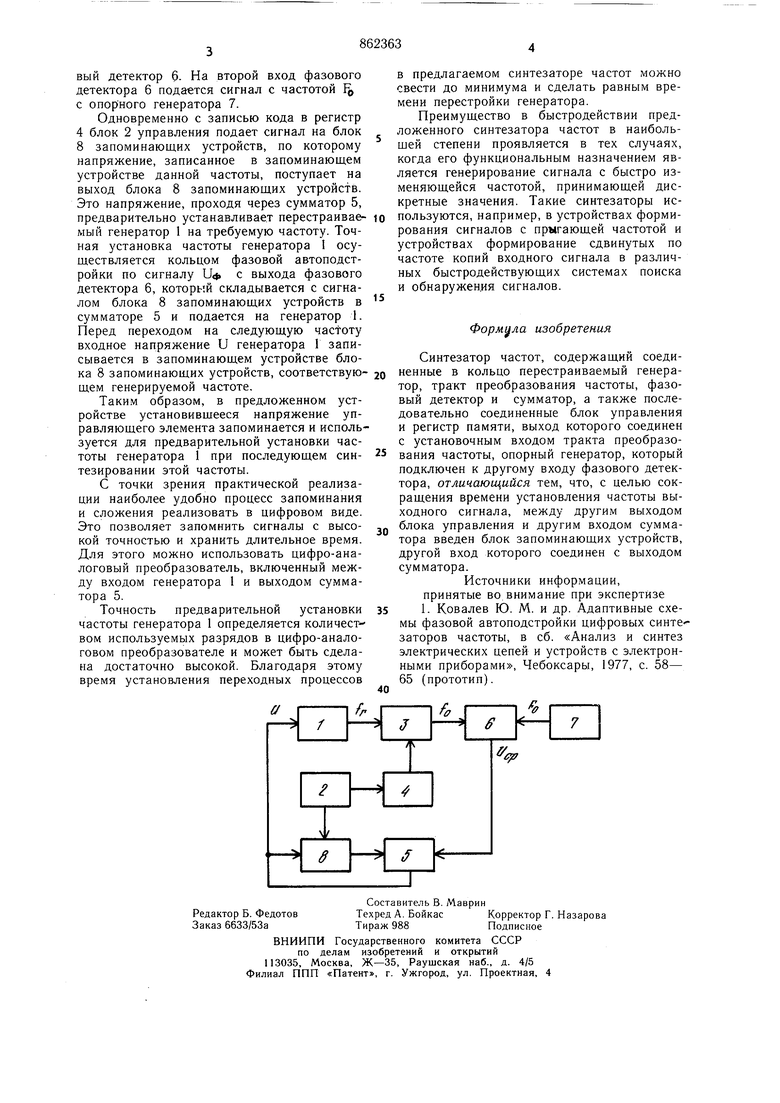

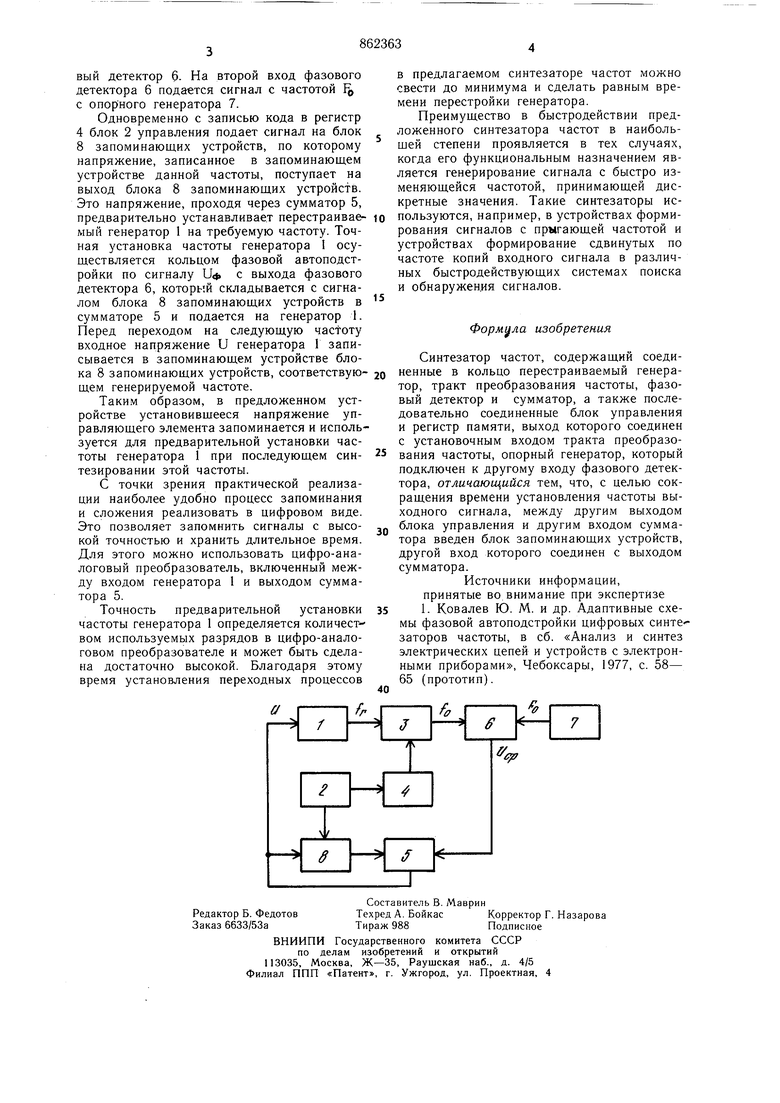

На чертеже приведена структурная электрическая схема предложенного устройства.

Синтезатор частот содержит перестраи10ваемый генератор 1, блок 2 управления, тракт 3 преобразования частот, регистр 4 памяти, сумматор 5 фазовый детектор 6, опорный генератор 7, блок 8 запоминающих устройств.

Устройство работает следующим обра15зом.

Блок 2 управления записывает в регистр 4 код, соответствующий требуемой частоте перестраиваемого генератора 1. Тракт 3 преобразования частоты в соответствии с

20 этим кодом преобразует сигнал перестраиваемого генератора 1 с частотой fr в сигнал с частотой , поступающий на фазовый детектор 6- На второй вход фазового детектора 6 подается сигнал с частотой 1 с опорного генератора 7. Одновременно с записью кода в регистр 4 блок 2 управления подает сигнал на блок 8 запоминающих устройств, по которому напряжение, записанное в запоминающем устройстве данной частоты, поступает на выход блока 8 запоминающих устройств. Это напряжение, проходя через сумматор 5, предварительно устанавливает перестраиваеыый генератор 1 на требуемую частоту. Точная установка частоты генератора 1 осуществляется кольцом фазовой автоподстройки по сигналу Уф с выхода фазового детектора 6, который складывается с сигналом блока 8 запоминающих устройств в сумматоре 5 и подается на генератор 1. Перед переходом на следующую частоту входное напряжение U генератора Г записывается в запоминающем устройстве блока 8 запоминающих устройств, соответствующем генерируемой частоте. Таким образом, в предложенном устройстве установившееся напряжение управляющего элемента запоминается и используется для предварительной установки частоты генератора 1 при последующем синтезировании этой частоты. С точки зрения практической реализации наиболее удобно процесс запоминания и сложения реализовать в цифровом виде. Это позволяет запомнить сигналы с высокой точностью и хранить длительное время. Для этого можно использовать цифро-аналоговый преобразователь, включенный между входом генератора 1 и выходом сумматора 5. Точность предварительной установки частоты генератора 1 определяется количеством используемых разрядов в цифро-аналоговом преобразователе и может быть сделана достаточно высокой. Благодаря этому время установления переходных процессов В предлагаемом синтезаторе частот можно свести до минимума и сделать равным времени перестройки генератора. Преимущество в быстродействии предложенного синтезатора частот в наибольшей степени проявляется в тех случаях, когда его функциональным назначением является генерирование сигнала с быстро изменяющейся частотой, принимающей дискретные значения. Такие синтезаторы используются, например, в устройствах формирования сигналов с прыгающей частотой и устройствах формирование сдвинутых по частоте копий входного сигнала в различных быстродействующих системах поиска и обнаружения сигналов. Форм1 ла изобретения Синтезатор частот, содержащий соединенные в кольцо перестраиваемый генератор, тракт преобразования частоты, фазовый детектор и сумматор, а также последовательно соединенные блок управления и регистр памяти, выход которого соединен с установочным входом тракта преобразования частоты, опорный генератор, который подключен к другому входу фазового детектора, отличающийся тем, что, с целью сокращения времени установления частоты выходного сигнала, между другим выходом блока управления и другим входом сумматора введен блок запоминающих устройств, другой вход которого соединен с выходом сумматора. Источники информации, принятые во внимание при экспертизе 1. Ковалев Ю. М. и др. Адаптивные схемы фазовой автоподстройки цифровых синте заторов частоты, в сб. «Анализ и синтез электрических цепей и устройств с электронными приборами, Чебоксары, 1977, с. 58- 65 (прототип).

Авторы

Даты

1981-09-07—Публикация

1979-06-06—Подача