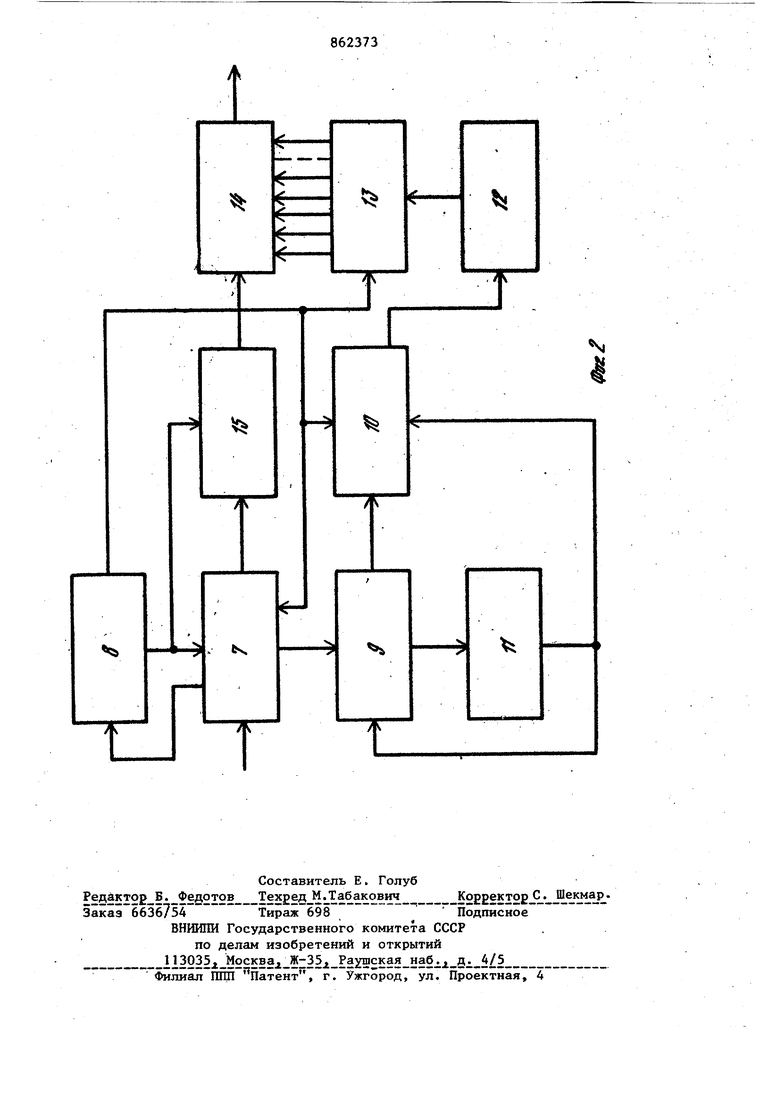

Изобретение относится к технике проводной электросвязи, может использоваться в аппаратуре асинхронно го ввода-вывода синхронной двоичной информации в цифровые каналы систем с импульсно-кодовой модуляцией и дел та-модуляцией . Известно устройство асинхронного ввода-вывода синхронной информации, содержащее на передакнцей стороне управляемый распределительi выходы которого соединены с соответств ощими входами блока памяти, а на приемной стороне - последовательно соединенны генератор тактовой частоты, управляе мый распределитель и блок памяти, а также декодер фазы, выход которого с единен с дополнительным входом блока памяти DlОднако известное устройство имеет низк:)по пропускную способность. Цель изобретения - повышение пропускной способности. Для этого в устройство асинхронного ввода-вьшода синхронной информации, содержащее на передающей стороне управляемый распределитель, выходы которого соединены с соответствующими входами блока памяти, а на приемной стороне - последовательно соединенные генератор тактовой частоты, управляемый распределитель и блок памяти, а также декодер фазы, выход которого соединен с дшюлнительным входом блока памяти, введешь на передающей стороне блок запуска и управления, блок контроля и коррекции прогноза, двоично-десятичный преобразователь и блок рекуррентных регистров сдвига, первый вход которого соединен с выходом двоичио-десятичного преобразователя, первый вход которого соединен с дополнительным входом памяти, первым выходом блока запуска и управления и вторым входом блока рекуррентных регистров сдвига, третий вход которого соединен со вторым выходом блока за3: 8 пуска и управления, третий и четвер тый выходы которого соединены соот-. ветственно с первым и вторым входами управляемого распределителя, причём первый выход блока памяти соединен со вторым входом двоично-десятичного пре образователя, второй выход блока памяти соединен через блок контроля и коррекции прогноза с четвертым входом блока рекуррентных регистров сдвига, а второй вход блока контроля и коррекций прогноза соединен с третьим вьрсодом блока запуска и управления, а на .приемной стороне введены последовательно соединенные блок запуска и управления, блок распознава,ния рекуррент, блок анализа отклоне-. 1ня от прогноза, блок коррекции прогноза и блок регул;лрного прогнозирования, выход которого соединен с входом генератора тактовой частоты. При этом второй вход управляемого распределителя соединен со вторым выходо блока запуска и управления и вторыми входами блока регулярного прогнозирования и блока распознавания рекуррент второй выход которого соединен со вхо дом блока запуска и управления , первый выход которого соединен с первым входом декодера фазы, второй вход которого соединен с третьим выходом бло ка распознавания рекуррент, причем вы ход блока коррекции прогноза соединен со вторым входом блока анализа отклонения от прогноза, второй выход которого соединен с третьим входом блока регулярного прогнозирования. На фиг. 1 представлена структурная электрическая схема передающей стороны предложенного устройства; на фиг.2 то же, приемной стороны. Устройство асинхронного ввода-вывода синхронной информации содержит на передающей стороне блок памяти 1, управляемый распределитель 2, блок 3 запуска и управления, двоично-десятичный преобразователь 4, рекуррентных регистров сдвига, блок 6 конт роля и коррекции прогноза, на приемной стороне (см. фиг. 2) - блок 7 рас познавания рекуррент, блок 8 запуска и управления, блок 9 анализа отклонения от прогноза, блок 10 регулярного прогнозирования, блок 11 коррекции прогноза, генератор 12 тактовой частоты, управляемый распределитель 13, блок памяти 14, декодер фазы 15. Устройство работает следующим образом. 3 Синхронный двоичный сигнал, следующий с тактовой частотой f , вводится в цифровой канал связи, характеризуемый несущей частотой f . Эта операция осуществляется на передающей стороне (фиг. 1). В соответствии с выбранной длиндй информационного цикла в блоке 3 .запуска и управления из сигналов частоты fц формируются опорные импульсы частоты , где N соответствует числу бит. Опорными им-.. J пульсами запускается управляемый распределитель 2, который затем тактируется импульсами тактовой частоты f . Импульсы с выхода управляемого распределителя 2 используются для записи синхроннь Х двоичных сигналов в блок памяти 1. Число импульсов, записанных в блок памяти, зависит от фазового соотношения сигналов частоты f и f, а также от возможнос1ей девиации сигналов частоты fc . Это число может равняться р-1, п или n+l. Количество импульсов /. в формируемом на передаче информационном цикле и его соответствие прогнозу контролируется блоком 6 контроля и коррекции прогноза, который запускается и управляется опорными импульсами с блока 3 запуска и управления. , Алгоритм этого контроля иллюстрируется таблицей. Алгоритм выбора псевдослучайной последовательности Если отклонение от прогноза происходит в нескольких (подряд следуюпшх) циклах и в одном и том же направлении, блок 6 контроля и коррекции прогноза корректирует прогнозируемую последовательность на передаче. Синхронные двоичные сигналы, записанные в блок памяти на тактовой частоте f, считьшаются оттуда быстрыми тактовыми импульсами (ВТИ), поступающими из блока 3 запуска и управ ления, и обрабатываются в двоично-десятичном преобразователе 4. Преобра зователь переводит информационный цикл из двоичного кода в десятичный. Максимальная длина информационного цикла в десятичном коде равна т.е. число отведенных под передачу ин формации временных позиций в этом в двоичном коде всегда равно В зависимости от наличия или отсутствия отклонения от прогнозируемого числа бит в информационном цикле в блоке 5 рекуррентных регистров сдви га выбирается псевдослучайная последо вательность I, II или III. Под действием быстрых тактовых импульсов и в соответствии с сигналами с выхода двоично-десятичного преобразователя 4 в блоке 5 рекуррентных регистров сдви га происходит сдвиг начальной фазы выбранной псевдослучайной последовательности. Последовательность из блока 5 рекуррентных регистров сдвига считьшается на несущей частоте f канала связи. Длина передаваемого в канал участка псевдослучайной последова тельности выбирается с учетом необходимости защиты информации от однократных ошибок. Цифровая последовательность из канала связи поступает на вход приемной стороны (фиг. 2). Перед началом передаШ на передающей стороне формируется псевдослучайная последовательность с таким фазовым сдвигом, который обычно в работе не используется. На приемной стороне по принятому и распознан ному участку этой псевдослучайной по следовательности происходит начальное фазирование опорных импульсов . частоты f /N и начинает работу блок 8 запуска и управления. Этот блок формирует опорйые импульсы и быстрые тактовые импульсы, используемые в дальнейшем в работе приемной стороны. С приходом участка псевдослучайной последовательности, несущего полезную информацию, блок 7 распознавания рекуррент определяет номер (I, II или И I) псевдослучайной последовательности. Эта операция производится в Случае приема .безошибочного участка псевдослучайной последовательности или приема участка , в котором имеется однократная ошибка. В зависимости от того, какая из псевдослучайных последовательностей была использована на передаче, соответствующий сигнал Поступает на блок 9 анализа отклонения от прогноза и далее на блок 10 регулярного прогнозирования. Кроме того, этот сигнал запоминается в бло- ке 11 коррекции прогноза. Блок 11 фиксирует отклонение от прогноза в одном направлении в нескольких (подряд следующих) циклах и принимает решение об изменении прогноза, для чего посылает соответствующие команды в блок 9 анализа отклонения от прогноза и в блок 10 регулярного прогнозирования. Заметим, что начало работы блока 10 определено опорными импульсами, поступающими из блока 8 запуска и управления, Сигнал с выхода блока 0 регулярного прогнозирования (скорректированный, в случае необходимости командами с выхода 9 анализа отклонения от прогноза или командами с выхода блока 1I коррекции прогноза) поступает на генератор тактовой частоты 12 и подстраивает частоту генератора в пределах информационного цикла таким образом, чтобы число бит в цикле на приемной стороне равнялось их числу на передающей стороне. Распознанный участок псевдослучайной последовательности, несущий полезную информацию, анализируется в декодере фазы 15, где определяется начальная фаза участка рекурренты в десятичном коде, которая затем перекодируется в двоичный код. Декодер функционирует с помощью быстрых тактовых импульсов. Представленная в двоичном коде нформация цикла поступает в блок паяти 14 на скорости, соответствующей есущей частоте f канала связи. Из блока памяти двоичные сигналы инормационного цикла считываются имульсами скорректированной тактовой астоты f(;, поступающими через управяемый распределитель 13 с выхода ге7862нератора тактовой частоты 12. Цикличность работы упра:вляемого распределителя 13 определяется опорными Импульсами с выхода блока 8 запуска и управления. Сигналы с выхода блока памяти 14 на тактовой частоте fg поступают в абонентскую линию. Таким образом, в предлагаемом устройстве асинхронного ввода (вьгаода) синхронной двоичной информации в цифрЬвой канал связи служебная информация передается за счет выбора различных псевдослучайных Последовательностей, что обеспечивает выигрьш в использовании пропускной способности ка нала. Формула изобретения Устройство асинхронного ввода-вывода синхронной информации, содержащее на передающей сторонеуправляемый распределитель, выходы которого соединены с соответствующими входами блока памяти, а на приемной стороне последовательно соединенные генератор тактовой частоты, управляекый ,распредели ель и блок памяти, а также декодер фазы, выход которого соединен с дополнительным входом блока памяти, отличающееся тем, что, с целью повышения пропускной способности, введены на передающей стороне блок запуска и управления, блок контроля и коррекции прогноза, двоично-де сятичный преобразователь и блок рекур рентных регистров сдвига, первый вход которого соединен с выходом двоичнодесятичного преобразователя, первый вход, которого соединен с дополнительным входом блока памяти, первым выходом блока запуска и управления, вторым входом блока рекуррентных регистров сдвига, третий вход которого соединен со вторым выходом блока за-i пуска и управления, третий и четвертый выходы которого соединены соответствейно с первым и вторым входами управляемого распределителя, причем первый выход блока памяти соединен со вторым входом Двоично-десятичного преобразователя, второй выход блока йамяти соединен через блок контроля и кйррекции прогноза с четвертым входом блока рекуррентных регистров сдвига, а второй вход блока контроля и коррекции прогноза соединен с третьим выходом блока заауска и управления, а на приемной стороне введены последовательно соединенш 1е блок запуска и управления, блок распознавания рекуррент, блок анализа отклонения от прогноза, блок коррекции прогноза и блок регулярного прогнозирования, выход которого соединен с входом генератора тактовой частоты, 1ФИ этом второй вход управляемого распределителя соединен со вторым выходом блока запуска и управления и вто1$ыми входами блока регулярного прогнозирования и блока распознавания рекуррент, второй выход которого соединен со входом блока запуска и управления, первый выход которого соединен с первьи входом декодера фазы, второй вход которого соединен с третьим выходом блока распознавания рекуррент, причем выход блока коррек ции прогноза соединен с вторым входом блока анализа отклонения от прогноза, второй выход которого соединен с третьим входом блока регулярного прогнозирования . Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 510792, кл.Н 04 J 3/00, 1974 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство ввода-вывода синхронной двоичной информации в цифровые тракты | 1984 |

|

SU1374438A1 |

| Устройство асинхронного ввода-вывода синхронной информации | 1982 |

|

SU1053307A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1979 |

|

SU860326A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1978 |

|

SU786024A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1987 |

|

SU1649681A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1982 |

|

SU1072278A1 |

| МНОГОКАНАЛЬНАЯ ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1990 |

|

RU2013012C1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1983 |

|

SU1111257A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Генератор псевдослучайных последовательностей | 1979 |

|

SU877533A1 |

I

Ф

ч

V

Авторы

Даты

1981-09-07—Публикация

1979-05-31—Подача