соединен к второму входу элемента И, выход элемента И подсоединен к управляющему входу декодера фазы, информационньв входы декоде.а фазы через декодер защиты от ошибок подключены к соответствующим информационным выходам коммутатора, причем S-вход КЗ триггера передачи и вход делителя частоты приема являются соответственно первым и вторым дополнительными опорными зходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1974 |

|

SU510792A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1986 |

|

SU1401629A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1982 |

|

SU1072278A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1979 |

|

SU860326A1 |

| Устройство асинхронного ввода-вывода синхронной информации | 1982 |

|

SU1053307A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1978 |

|

SU786024A1 |

| Адаптивная система передачи дискретных сообщений | 1986 |

|

SU1497755A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1469562A1 |

УСТРОЙСТВО АСИНХРОННОГО СОПРЯЖЕНИЯ ЦИФРОВЫХ СИГНАЛОВ, содержащее на передающей стороне последовательно соединенные фазовый компаратор, управляемый распределитель передачи и блок памяти передачи, а также кодер фазы и датчик фазирующей комбинации, выход которого подключен к входу записи служебной информации блока памяти передачи, вход кодера фазы подключен к второму выходу фазового компаратора, а на приемной стороне - последовательно соединенные блок фазирования по циклам, коммутатор и блок памяти приема, последовательно соединенные декодер фазы и управляемый распределитель приема, а также блок фазовой автоподстройки . частоты, вход и выход которого подключены соответственно к выходу декодера фазы и тактовому входу управляемого распределителя приема, другие входы записи информации блока памяти приема подключены к выходам управляемого распределителя приема, а фазирующий выход коммутатора подсое 1инен к входу блока фазирования по циклам, причем объединенные тактовые входы фазового компаратора и управляемого распределителя передачи являются тактовым входом устройства, информационный и опорный входы блока памяти передачи являются соответственно информационным и опорным вхо дами устройства,, выход блока памяти передачи является канальным выходом устройства, информационный вход коммутатора и выход блока памяти приема являются соответственно канальным входом и информационным выходом устройства, отличающееся тем, что, с целью повьпиения точности сопряжения цифровых сигналов, в устройство введены на передающей стороне (Л последовательно соединенные RS-триггер передачи, элемент И и блок задержки, а также делитель частоты передачи и кодер защиты от ошибок, а на приемной стороне - последовательно соединенные делитель частоты приема, элемент И, блок задержки и RS-триггер приема, а также декодер защиты от ощибок, при этом на пере сд дающей стороне вькод блока задержки подсоединен к R-входу RS-триггера передачи,вход и выход делителя часч тоты передачи подключены соответст- венно к опорному входу блока памяти передачи и второму входу элемента И, выход которого подсоединен к информационному входу фазового компаратора, выходы кодера фазы через кодер защиты от ошибок подсоединены к соответствующим входам записи информации блока памяти передачи, а на приемной стороне вькод блока фазирования по циклам подсоединен к R-входу RSтриггера приема, выход которого под

Изобретение относится к технике электросвязи и может быть использовано для ввода-вывода синхронных двоичных сигналов в цифровые тракты систем с дельта- и импульсйо-кодовой модуляцией.

Известно устройство асинхронного сопряжения цифровых сигналов, содержащ е на передакщей стороне последовательно соединенные блок Запуска, блок прогнозирования, блок сравнения кодер и блок памяти, последовательно соединенные управляемый распределитель и счетчик, а также блок цикловой синхронизации, выход которого подсоединен к второму входу блока памяти, выход блока запуска подсоединен к объединенным входам блока цикловой синхронизации, счетчика и упрайляемого распределителя, дополнительный выход блока запуска подсоединен к второму входу управляемого распределителя, другие выходы которого подсоединены к соответствующим дополнительным входам блока памяти, выход кодера подсоединен к второму входу блока прогнозирования а на приемной стороне - последовательно соединенные коммутатор, блок цикловой синхронизации, декодер, блок прогнозирования, блок автоматической подстройки частоты, управляемый распределитель и блок памяти, другие входы которого подключены к соответствующим выходам коммутатора, дополнительный выход крторого подсоединен к входу декодера, а второй вход управляемого распределителя подключен к дополнительному выходу блока цикловой синхронизации СПНедостатком известного устройства асинхронного сопряжения цифровых сигналов является низкая точность сопряжения цифровых сигналов.

Наиболее близким по техническому :решению к предлагаемому является устройство асинхронного сопряжения цифровых сигналов, содержащее на передакицей стороне последовательно соединенные фазовьй компаратор, управляемый распределитель передачи и блок памяти передачи, а также кодер фазы и датчик фазирукицей комбинации, выход которого подключен к входу записи служебной информации блока памяти передачи, вход кодера фазы подключен к второму выходу фазового компаратора, а на приемной стороне - последовательно соединенные блок фазирования по циклам, коммутатор и блок памяти приема, последовательно соединенные декодер фазы и управляемьй распределитель, приема, а также блок фазовой автоподстройки частоты, вход и выход которого подключен соответственно к выходу декодера фазы и тактовому входу управляемого распределителя приема, другие входы записи инфор мации блока памяти приема подключены к выходам управляемого распределителя приема, а фазирующий выход коммута тора подсоединен, к входу блока фазирования по циклам, причем объединенные тактовые входы фазового компаратора и управляемого распределителя передачи являются тактовым входом устройства, информационный и опорный входы блока памяти передачи являются соответственно информационным и опорным входами устройства, выход блока памяти передачи является канальным ; выходом устройства, информационный вход коммутатора и выход блока памяти приема являются соответственно канальным входом и информационным выходом устройства, выходы кодера фазы подсоединены к соответствующим iдополнительным входам записи блока памяти передачи, выходы служебных

311

сигналов коммутатора подсоединены к соответствующим информационным входам декодера фазы, управляющий вход которого подключен к выходу опорных сигналов блока фазирования по цикла:м 23. .

Недостатком известного устройства асинхронного сопряжения цифровых сигналов является низкая точность сопряжения цифровых сигналов.

Цель изобретения - повьшение точности сопряжения цифровых сигналов.

Поставленная цель достигается тем, что в устройство асинхронного сопряжения цифровых сигналов, содержащее на передакицей стороне последовательно соединенные фазовый компаратор, управляемый распределитель передачи и блок памяти передачи, а также кодер фазы и датчик фазирующей комбинации, 1выход которого подключен к входу записи служебной информации блока па мяти передачи, вход кодера фазы подключен к второму выходу фазового компаратора, а на приемной стороне последовательно соединенные блок фазирования по циклам, коммутатор и блок памяти приема, последовательно соединенные декодер фазы и управляемый распределитель приема, а также блок фазовой автоподстройки частоты,

вход и выход которого подключены COOT

ветственно к выходу декодера фазы и тактовому входу управляемого распре делителя приема, другие входы записи информации блока памяти приема подклю чены к выходам управляемого распределителя приема, а фазирующий выход коммутатора подсоединен к входу блока фазирования по циклам, причем объединенные тактовые входы фазового компаратора и управляемого распределителя передачи являются тактовым входом устройства, информационный и опорный входы блока памяти передачи являются соответственно информационным и опорным входами устройства, выход блока памяти передачи является канальным выходом устройства, информационный вход коммутатора и выход блока памяти приема ЯВЛЯЮ.ТСЯ соответственно канальным входом и информационным выходом устройства, введены на передающей стороне последовательно соединенные RS-трйггер передачи, злёмент И и блок задержки, а также делитель частоты передачи и кодер защиты от ощибок, а на приемной стороне - последовательно соединенные делитель час257

тоты приема, элемент И, блок задерж ки и RS-триггер приема, а также декодер защиты.от ощибок, при этом на передающей стороне выход блока задерж5 ки подсоединен к R-входу RS-триггера передачи, вход и выход делителя частоты передачи подключены соответственно к опорному входу блока памяти передачи и второму входу элемента И,

0 выход которого подсоединен к информационному входу фазового компаратора, выходы кодера фазы через кодер защиты от ошибок подсоединены к соот-. ветствующим входам записи информации

5 блока памяти передачи, а на приемной стороне выход блока фазирования по циклам подсоединен к R-входу RS-триггера приема, выход которого подсоединен к второму входу элемента И,

0 выход элемента И подсоединен к управляющему входу декодера фазы, информационные входы декодера фазы череэ декодер защиты от ошибок подключены к соответствующим информационным

5 выходам коммутатора, причем S-вХод RS-триггера передачи и вход делителя частоты приема являются соответственно первым и вторым дополнительными опорными входами устройства.

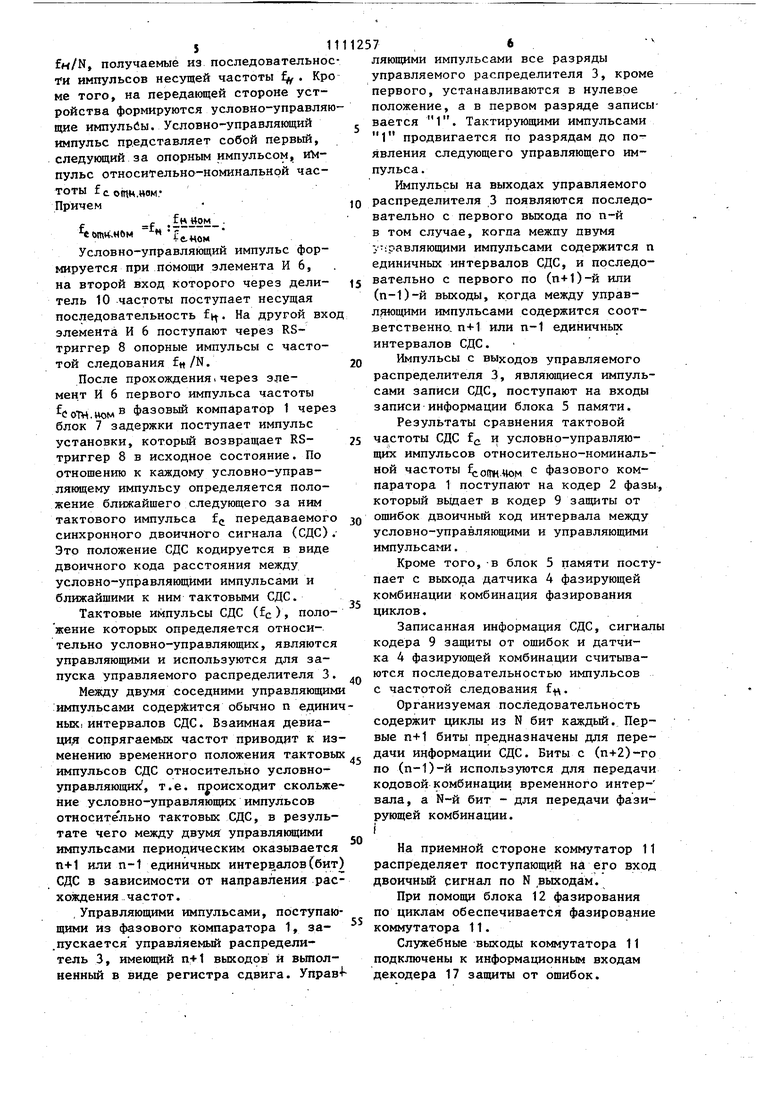

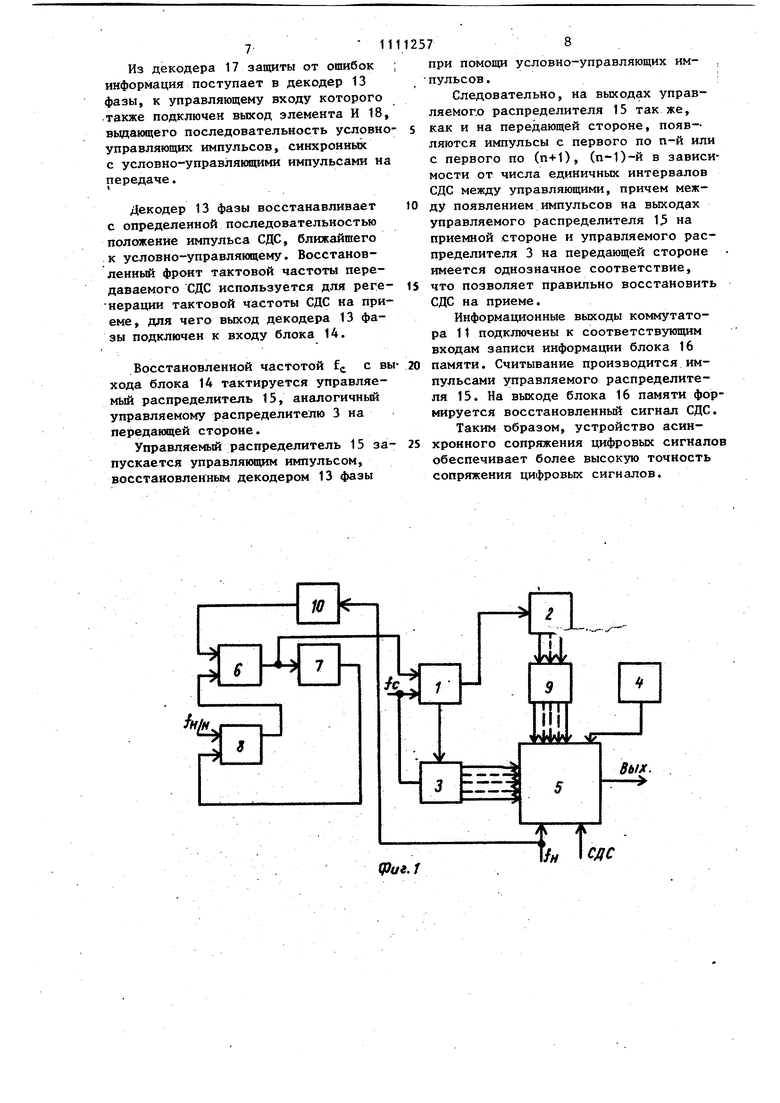

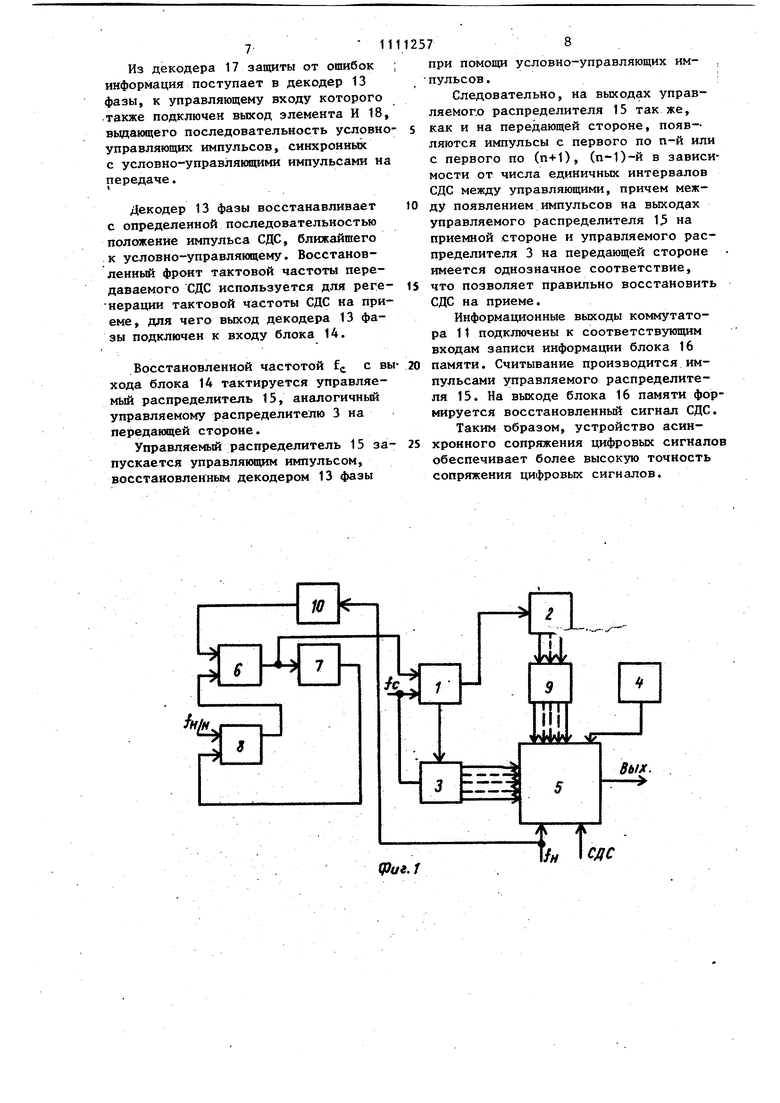

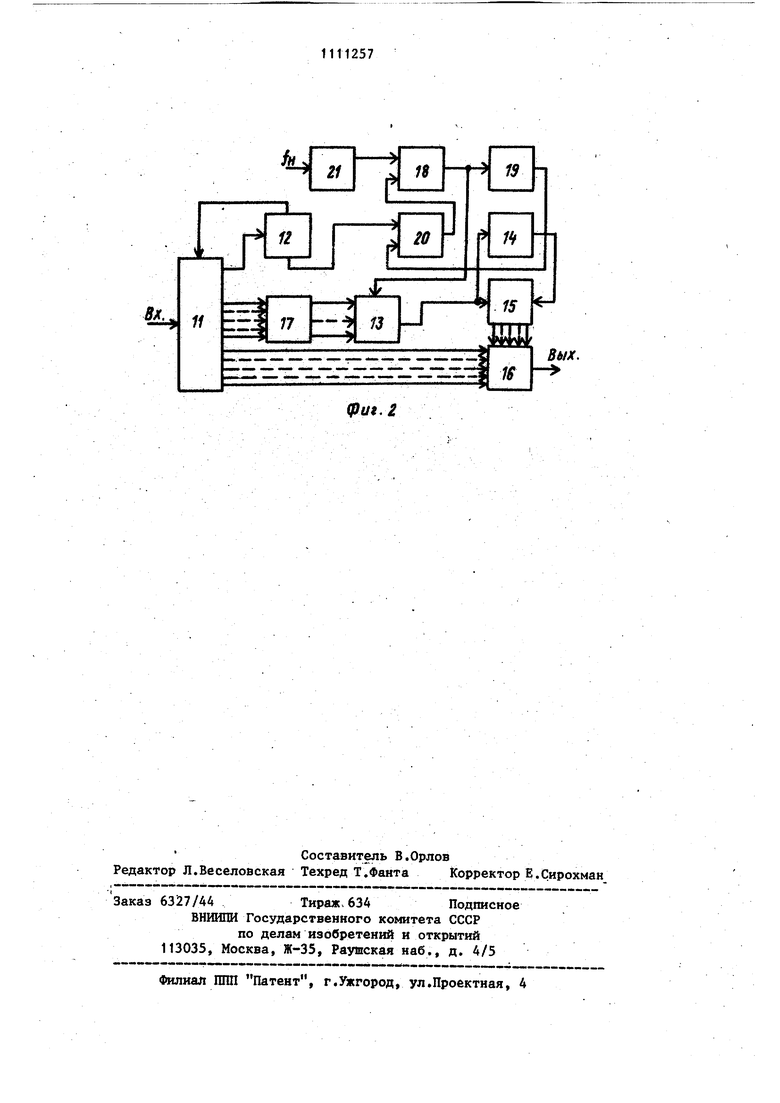

0 На фиг, 1 и 2 приведены соответственно передающая и приемная стороны устройства асинхронного сопряжения дифровых сигналов.

Устройство асинхронного сопряжения цифровых сигналов содержит на передакядей стороне фазовый компаратор 1, кодер 2 фазы, управляемый распределитель 3 передачи, датчик 4 фазирукнцей комбинации, блок 5 памяти передачи,

элемент И 6, блок 7 задержки, RSтриггер 8 передачи, кодер 9 защиты от ошибок, делитель 10 частоты передачи, а на приемной стороне - коммутатор 11, блок 12 фазирования по цик, лам, декодер 13 фазы, блок 14 фазовой автоподстройки частоты, управляемый распределитель 15 приема, блок .16 памяти приема, декодер 17 защиты от ощибок, элемент И 18, блок 19 задержки, RS-триггер 20 приема, делитель 21 частоты приема.

Устройство асинхронного сопряжения цифровых сигналов работает следующим образом.

Для передачи синхронного двоичного сигнала с тактовой частотой f с помощью несущей последовательности if на передающем конце формируются опорные импульсы с частотой следования f«/N, получаемые из последовательно ти импульсов несущей частоты f . Кр ме того, на передающей стороне устройства формируются условно-управля щие импульйы. Условно-управляющий импульс представляет собой первый, следующий за опорным импульсом, irt пульс относительно-номинальной частоты fcomM.HOMпричемf -f .ti5°:t ЧотнчМбм « Че-мом Условно-управляющий импульс формируется при помощи элемента И 6, на второй вход которого через делитель 10 частоты поступает несущая последовательность fi. На другой вх элемента И 6 поступают через RSтриггер 8 опорные импульсы с частотой следования ftt/N. После прохождения через элемент И 6 первого импульса частоты coTrtHOM фазовый компаратор 1 чере блок 7 задержки поступает импульс установки, которьш возвращает RSтриггер 8 в исходное состояние. По отношению к каждому условно-управляющему импульсу определяется положение ближайщего следующего за ним тактового импульса (. передаваемог синхронного двоичного сигнала (СДС) Это положение СДС кодируется в виде двоичного кода расстояния между условно-управляющими импульсами и ближайщими к ним тактовыми СДС. Тактовые импульсы СДС (fc), поло жение которых определяется относительно условно-управляющих, являютс управляющими и используются для запуска управляемого распределителя 3 Между двумя соседними управляющи :импульсами содержится обычно п един ных интервалов СДС. Взаимная девиаци,я сопрягаемых частот приводит к и менению временного положения тактовых импульсов СДС относительно условноуправляющиз, т.е. происходит скольже ние условно-управляющих импульсов относительно тактовых СДС, в результате чего между двумя управляющими импульсами периодическим оказывается п+1 или п-1 единичных интервалов(бит) СДС в зависимости от направления расхождения частот. , Управляющими импульсами, поступающими из фазового компаратора 1, за.пускается управляемый распределитель 3, имеющий выходов и вьтолненный в виде регистра сдвига. Управ- 76ляющими импульсами все разряды управляемого распределителя 3, кроме первого, устанавливаются в нулевое положение, а в первом разряде записывается 1. Тактирующими импульсами 1 продвигается по разрядам до появления следующего управляющего импульса . Импульсы на выходах управляемого распределителя 3 появляются последовательно с первого выхода по п-й в том случае, когда между двумя у-;равляющими импульсами содержится п единичных интервалов СДС, и последовательно с первого по (п+1)-й или (п-1)-й выходы, когда между управляющими импульсами содержится соответственно, п+1 или п-1 единичных интервалов СДС. Импульсы с выходов управляемого распределителя 3, являющиеся импульсами записи СДС, поступают на входы записи информации блока 5 памяти. Результаты сравнения тактовой частоты СДС f и условно-управляющих импульсов относительно-номинальной частоты о(ШЧом фазового компаратора 1 поступают на кодер 2 фазы, который вьщает в кодер 9 защиты от ошибок ДВ.ОИЧНЫЙ код интервала между условно-управляющими и управляющими импульсами. 5 памяти постуКроме того, в блок 4 фазирующей пает с выхода датчика комбинации комбинация фазирования циклов. Записанная информация СДС, сигналы кодера 9 защиты от ошибок и датчика 4 фазирующей комбинации считываются последовательностью импульсов с частотой следования f. Организуемая последовательность содержит циклы из N бит каждый. Первые п+1 биты предназначены для передачи информации СДС. Биты с (п+2)-гр / л ч по (п-1)-и используются для передачи кодовой комбинации временного интервала, а N-й бит - для передачи фазирующей комбинации. На приемной стороне коммутатор 11 распределяет поступающий на его вход двоичный сигнал по N выходам. При помощи блока 12 фазирования по циклам обеспечивается фазирование коммутатора 11. Служебные выходы коммутатора 11 подключены к информационным входам декодера 17 защиты от ошибок.

7- 11

Из декодера 17 защиты от ошибок информация поступает в декодер 13 фазы, к управляющему входу которого также подключен выход элемента И 18, вьщающего последовательность условноуправляющих импульсов, синхронных с условно-управляющими импульсами на передаче.

Декодер 13 фазы восстанавливает с определенной последовательностью положение импульса СДС, ближайшего к условно-управляющему. Восстановленный фронт тактовой частоты передаваемого СДС используется для регенерации тактовой частоты СДС на приеме, для чего выход декодера 13 фазы подключен к входу блока 14.

Восстановленной частотой f с выхода блока 14 тактируется управляемЬй распределитель 15, аналогичный управляемому распределителю 3 на передающей стороне.

Управляемый распределитель 15 запускается управляющим импульсом, восстановленным декодером 13 фазы

78

при помощи условно-управляющих им- , пульсов.:

Следовательно, на выходах управляемог.о распределителя 15 так же,

как и на передающей стороне, появляются импульсы с первого по п-й или с первого по (п+1), (п-1)-й в зависимости от числа единичных интервалов СДС между управляющими, причем между появлением импульсов на выходах управляемого распределителя 15 на приемной стороне и управляемого распределителя 3 на передающей стороне имеется однозначное соответствие,

что позволяет правильно восстановить СДС на приеме.

Информационные выходы коммутатора 11 подключены к соответствующим входам записи информации блока 16

памяти. Считывание производится импульсами управляемого распределителя 15. На выходе блока 16 памяти формируется восстановленный сигнал СДС. Таким образом, устройство асинхронного сопряжения цифровых сигналов обеспечивает более высокую точность сопряжения цифровых сигналов.

Лг.

СДС

(Pui.f

фш,2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1978 |

|

SU786024A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1974 |

|

SU510792A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-08-30—Публикация

1983-06-29—Подача