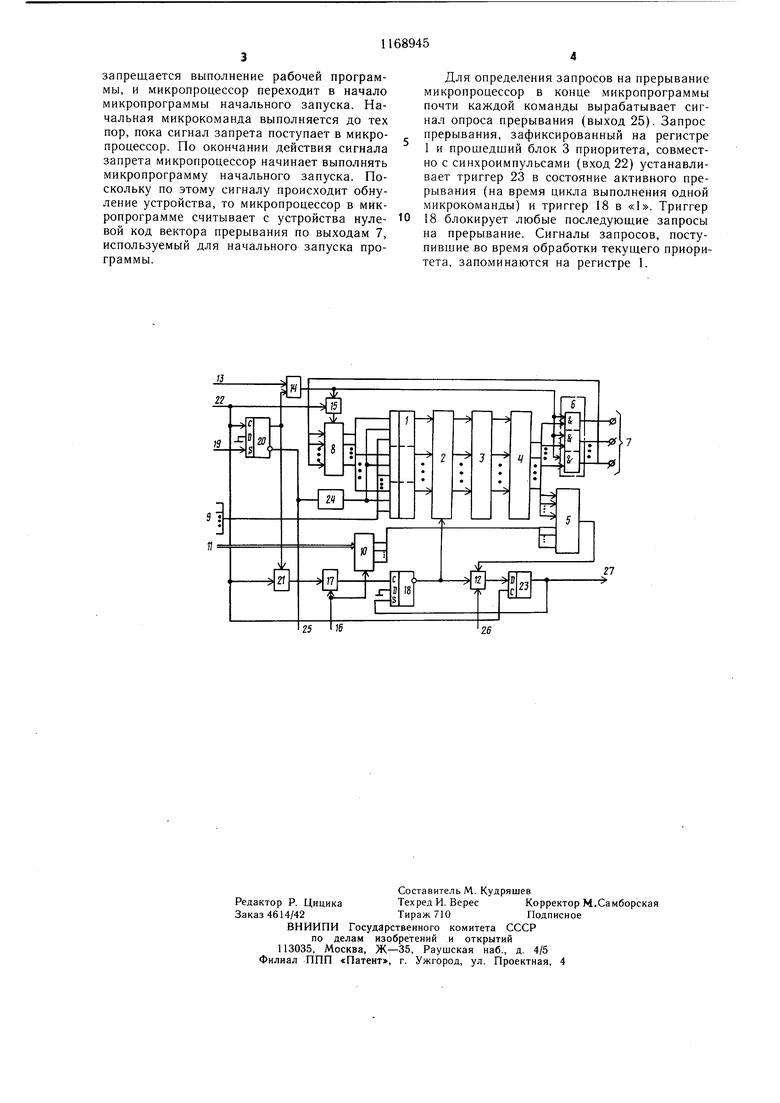

Изобретение относится к вычислительной технике и может быть использовано для организации прерывания при проектировании специализированных микро-ЭВМ. Цель изобретения - повышение надежности обслуживания запросов путем уменьшения вероятности их потери. На чертеже показана структурная схема устройства. Устройство содержит регистры 1 и 2, блок 3 приоритета, шифратор 4, схему 5 сравнения, группу элементов И 6, группу выходов 7 устройства, дешифратор 8, группу информационных входов 9 устройства, регистр 10, группу кодовых входов 11 устройства, элемент И 12, вход 13 чтения устройства, элемент ИЛИ 14, элемент И 15, вход 16 записи устройства, элемент ИЛИ 17, триггер 18, вход 19 запуска устройства, триггер 20, элемент И 21, тактовый вход 22 устройства, триггер 23, элемент 24 задержки, сигнальный выход 25 устройства, опросный вход 26 устройства, выход 27 прерывания устройства. Устройство работает следующим образом. В начальный момент работы (например, после включения напряжения питания) регистры 1 и 2 должны быть обнулены, а триггер 18, служаший для обеспечения запрета прерывания, установлен в нулевое состояние, разрешающее прием запросов прерываний в регистр 2. Установка начальных условий в устройстве позволяет микропроцессору начать выполнять рабочую программу с заданной команды. В противном случае микропроцессор обрабатывает ложные сигналы прерывания, искажается выполнение рабочих программ. Сигнал «Запуск на входе 19 устанавливает триггер 20 в единичное состояние. Сигнал «1 с выхода триггера 20 через элемент ИЛИ 14 открывает группу элементов И 6 и разрешает прохождение синхроимпульсов с входа 22 на управляющий вход дешифратора 8. Единичный выход триггера 20 также разрешает установку триггера 18 в нулевое состояние, переводя тем самым регистр 2 запросов прерываний в режим, когда состояние выходов регистра повторяет состояние его входов. Таким образом, в процессе начальной установки образуется схема, состоящая из регистров 1 и 2 запросов прерываний, блока 3 приоритета прерываний, шифратора 4, группы элементов И 6 и дешифратора 8, в которой поочередно сбрасываются все триггеры регистра 1, причем длительность импульса сброса определяется суммарным временем распространения в указанных блоках. Импульс сброса стробируется импульсом синхронизации (вход 22) через элемент И 15 и дешифратор 8. В процессе начальной установки сигнал «О с нулевого выхода триггера 20, поступающий в микропроцессор по выходу 25, запрещает выполнение основной программы, переводя микропроцессор в начало микропрограммы начального запуска программы. Триггер 20 через элемент 24 задержки также запрещает прием сигналов запросов прерывания по входам 9 на регистр 1 запросов прерывания в момент запуска устройства. В микропрограмме начального запуска в одной из первых микрокоманд микропроцессор устанавливает начальный код маски в регистр 10 (вход 11) управляющим сигналом по входу 16. После процесса начального запуска, если на входах 9 нет ни одного запроса, то элементы И 6 закрыты и сигнал прерывания (выход 27 устройства) не вырабатывается. Программа микропроцессора выполняется, не прерываясь. Допустим, что по одному из входов 9 пришел запрос на прерывание. Он запоминается на соответствующем триггере регистра 1 и далее проходит через регистр 2 на блок 3, так как триггер 18 сброшен. Информация с регистра 2 поступает через блок 3 приоритета прерываний и шифратор 4 на элементы И 6 и схему 5 сравнения. Код приоритета, поступивший на схему 5 сравнения, сравнивается с кодом, записанным в регистр 10. Если код с шифратора 4 больше кода, хранящегося в регистре 10 маски, то схема 5 сравнения вырабатывает сигнал, который разрешает выработку сигнала прерывания программы. Если же код с шифратора 4 меньше или равен коду с регистра 10 маски, то схема сравнения запрешает выработку указанного сигнала. При совпадении внешнего сигнала опроса прерывания (вход 26) и сигнала синхронизации (вход 22), поступающих из микропроцессора, на выходе 27 появляется сигнал прерывания программы. Причем, длительность его определяется периодом частоты синхронизации. Сигнал на выходе 27 появляется по переднему фронту синхроимпульса и устанавливает триггер 18 в положение, запрещающее прием новых запросов на прерывание в регистр 2. Триггер 18 также подготавливает триггер 23 к сбросу в исходное состояние. Следующим синхроимпульсом происходит сброс триггера 23 и окончание сигнала прерывания программы. Предварительно по внешнему сигналу «Запуск (вход 19) устройство для прерывания программ вырабатывает сигнал запрета (выход 27), поступающий в микропроцессор в блок микропрограммного управления. По этому сигналу в микропроцессоре

запрещается выполнение рабочей программы, и микропроцессор переходит в начало микропрограммы начального запуска. Начальная микрокоманда выполняется до тех пор, пока сигнал запрета поступает в микропроцессор. По окончании действия сигнала запрета микропроцессор начинает выполнять микропрограмму начального запуска. Поскольку по этому сигналу происходит обнуление устройства, то микропроцессор в микропрограмме считывает с устройства нулевой код вектора прерывания по выходам 7, используемый для начального запуска программы.

Для определения запросов на прерывание микропроцессор в конце микропрограммы почти каждой команды вырабатывает сигнал опроса прерывания (выход 25). Запрос прерывания, зафиксированный на регистре 1 и прошедший блок 3 приоритета, совместно с синхроимпульсами (вход 22) устанавливает триггер 23 в состояние активного прерывания (на время цикла выполнения одной микрокоманды) и триггер 18 в «1. Триггер 18 блокирует любые последуюш,ие запросы на прерывание. Сигналы запросов, поступившие во время обработки текущего приоритета, запоминаются на регистре 1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приоритетного прерывания для микро-ЭВМ | 1982 |

|

SU1113803A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммное устройство для обработки прерываний | 1983 |

|

SU1126956A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Устройство многоуровневого прерывания | 1983 |

|

SU1104516A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для моделирования системы сбора данных | 1988 |

|

SU1534469A1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

УСТРОЙСТВО ДЛЯ ПРЕРЫВАНИЯ ПРОГРАММ, содержащее три регистра, блок приоритета, шифратор, дешифратор, группу элементов П, три элемента И, два элемента ИЛИ, нричем входы сброса первого регистра соединены с выходами дешифратора, группа входов второго регистра соединена с группой кодовых входов устройства, группа выходов блока приоритета соединена с группой входов шифратора, отличающееся те.м, что, с целью повышения надежности обслуживания запросов путе.м уменьшения вероятности их потери, устройство содержит три триггера, элемент задержки и схему сравнения, причем каждый вход группы информационных входов устройства соединен с тактовым входом одноименного разряда первого регистра, информационные входы которого через элемент задержки соединены с инверсным выходом первого триггера и с сигнальным выходом устройства, тактовый вход которого соединен с тактовыми входами первого и второго триггеров и с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с прямым выходом первого триггера и с выходо.м первого элемента ИЛИ, первый и второй входы которого соединены соответственно с входом чтения устройства и с прямым выходом первого триггера, информационный вход которого соединен с входом логического нуля устройства, входы запуска и записи которого соединены соответственно с единичным входом первого регистра и с тактовым входом второго регистра, группа выходов которого соединена с первой группой входов схемы сравнения, вторая группа входов которой соединена с группой выходов шифратора и с первыми входами элементов И группы, вторые входы и выходы которых соединены соответственно с выходом первого элемента ИЛИ, с группой выходов устройства и с группой входов дешифратора, управляюший вход которого 3 соединен с выходом второго элемента И, (Л группа выходов первого регистра соединена с группой входов третьего регистра, группа выходов которого соединена с группой входов блока приоритета, выход первого элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с входо.м записи устройства, опросный вход которого соединен с первым входом третьего элемента И, второй вход и выход которого соединены соответственно с ot выхолчом схемы сравнения и с информацион00 ным входом второго триггера, выход кото( рого является выходом нрерывания СЛ ройства и соединен с единичным входо.м третьего триггера, информационный и тактовый входы которого соединены соответственно с входо.м логического нуля устройства и с выходом второго элемента ИЛИ, выход третьего триггера соединен с третьим входом третьего э.чемента И и с тактовым входом третьего регистра.

| Устройство для прерывания программ | 1978 |

|

SU792254A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство прерывания | 1974 |

|

SU525094A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-23—Публикация

1983-12-20—Подача