1

Изобретение относится к вьтчисли- тельной технике и может быть использовано при построении мультипроцессорных систем.

Целью изобретения является повышение надежности системы за счет введения контроля времени захвата шины каждым процессором.

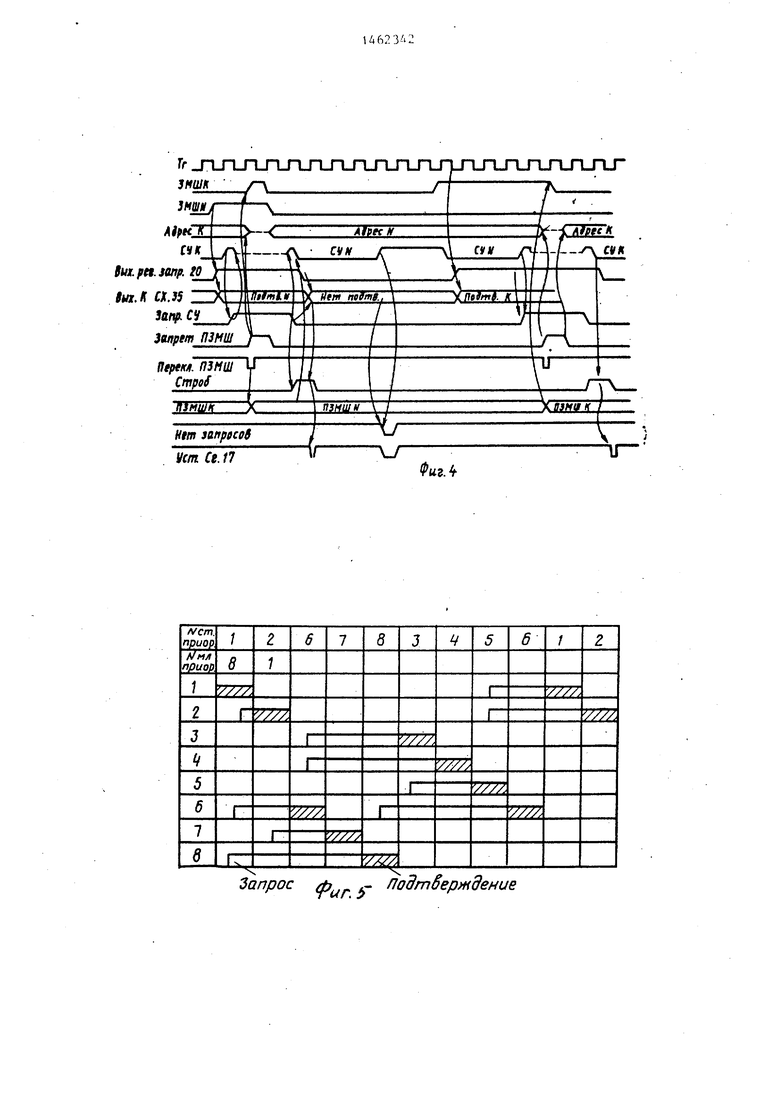

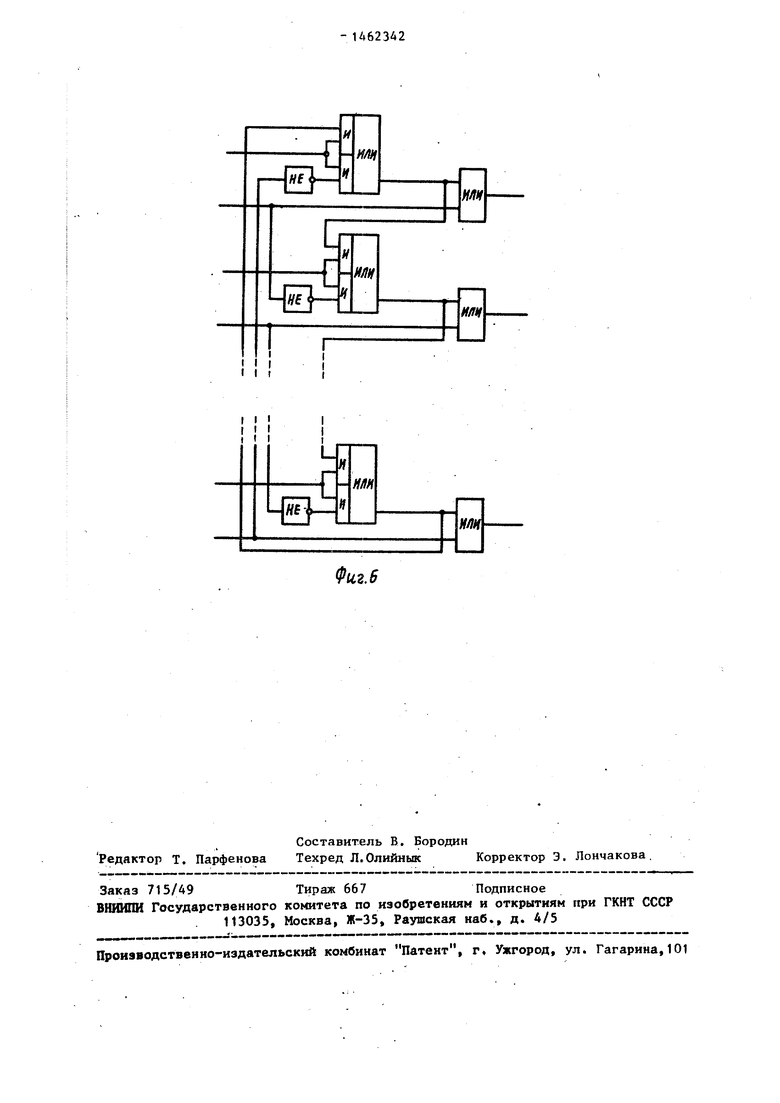

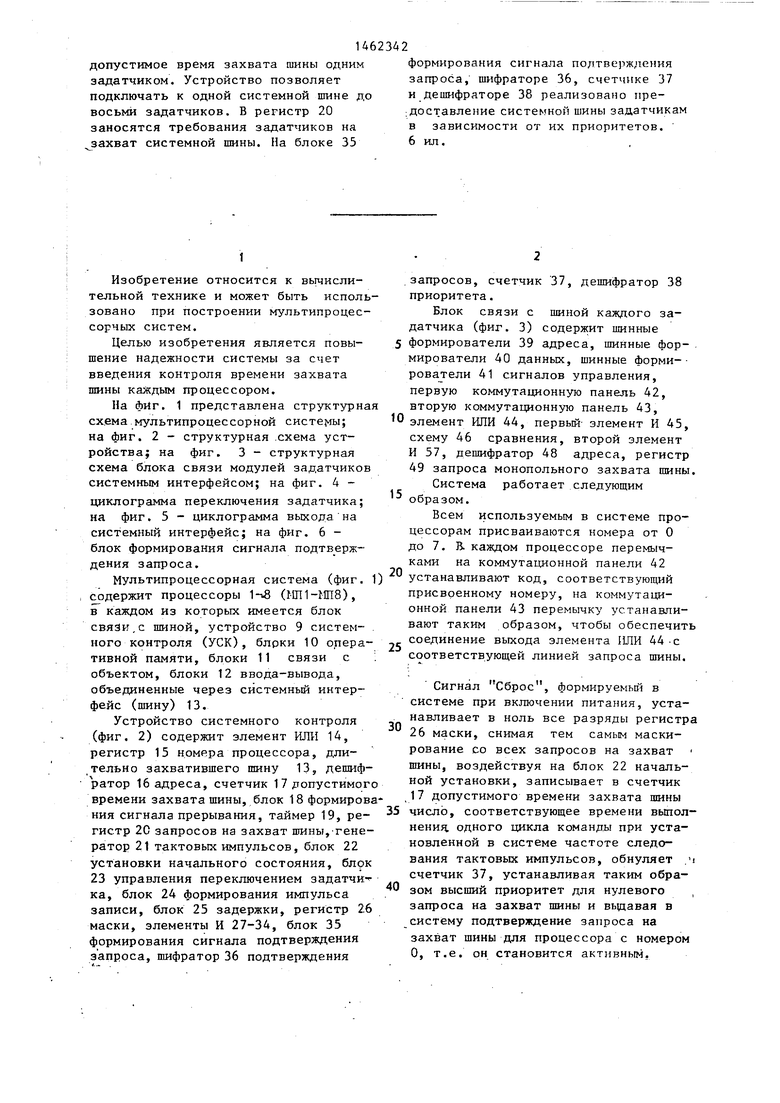

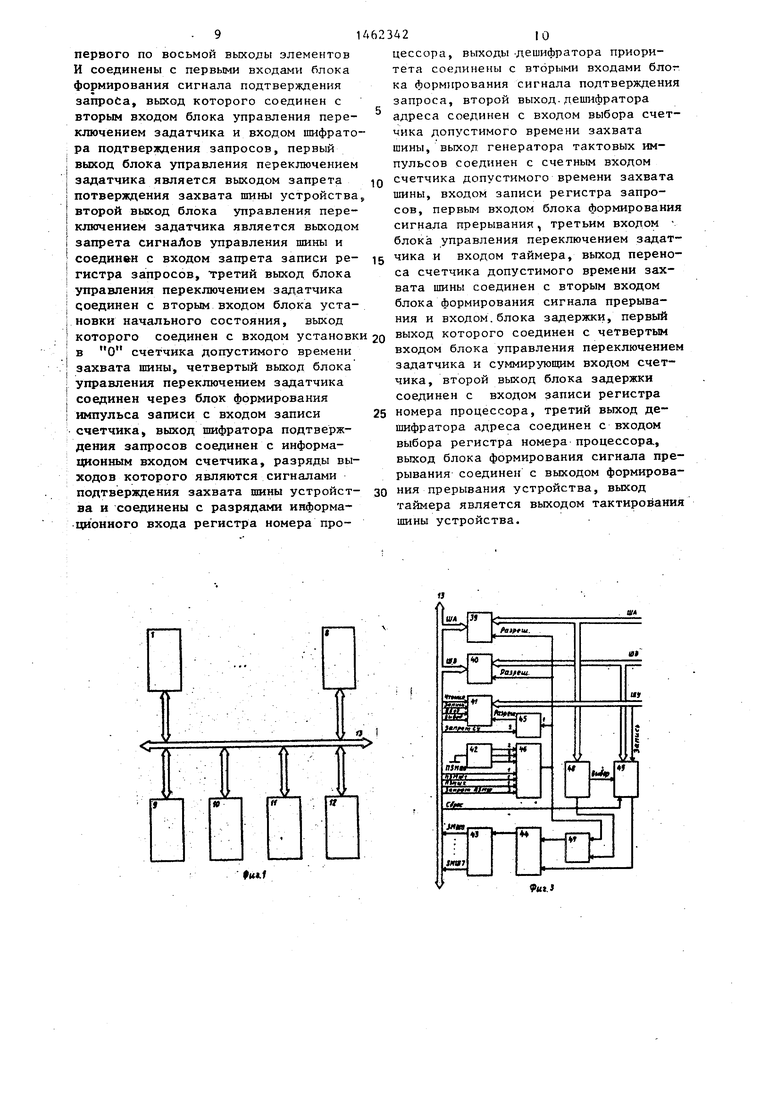

На фиг. 1 представлена структурна схема мультипроцессорной систе чы; на фиг. 2 - структурная .схема устройства; на фиг, 3 - структурная схема блока связи модулей задатчиков системным интерфейсом; на фиг. 4 - циклограмма переключения задатчика; на фиг. 5 - циклограмма выхода на системный интерфейс; на фиг. 6 - блок формирования сигнала подтверждения запроса.

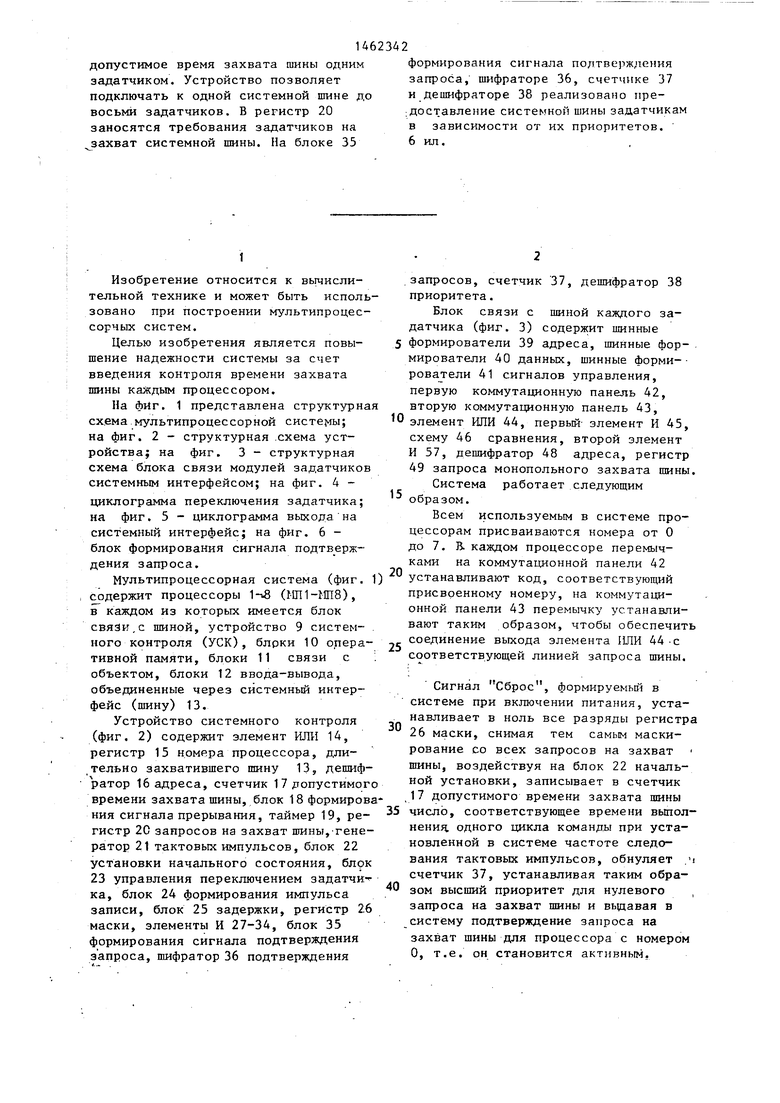

Мультипроцессорная система (фиг. содержит процессоры 1-ь8 (М111-Ш8), в каждом из которых имеется блок связи,с шиной, устройство 9 системного контроля (УСК), блрки 10 оперативной памяти, блоки 11 связи с объектом, блоки 12 ввода-вывода, объединенные через системный интерфейс (шину) 13.

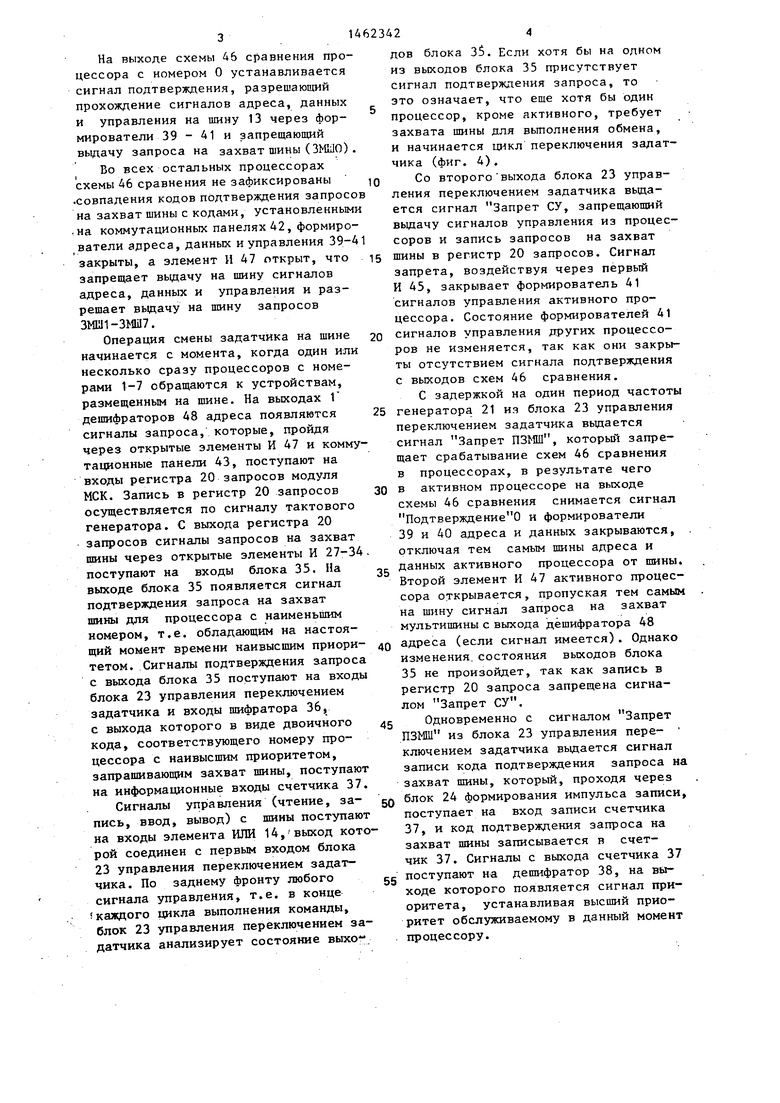

Устройство системного контроля (фиг. 2) содержит элемент ИЛИ 14, регистр 15 номера процессора, дли- ,тельно захватившего шину 13, дешифратор 16 адреса, счетчик 1 7 допустимог времени захвата шины, блок 18 формировния сигнала прерывания, таймер 19, регистр 20 запросов на захват шины,-генератор 21 тактовых импульсов, блок 22 установки начального состояния, блрк 23 управления переключением задатчи- ка, блок 24 формирования импульса записи, блок 25 задержки, регистр 26 маски, элементы И 27-34, блок 35 формирования сигнала подтверждения запроса, шифратор 36 подтверждения

0

5

0

5

0

5

0

запросов, счетчик 37, дешифратор 38 приоритета.

Блок связи с шиной каждого задатчика (фиг. 3) содержит шинные формирователи 39 адреса, шинные фор- . мирователи 40 данных, шинные форми- 41 сигналов управления, первую коммутационную панель 42, вторую коммутационную панель 43, элемент ИЛИ 44, первый- элемент И 45, схему 46 сравнения, второй элемент И 57, дешифратор 48 адреса, регистр 49 запроса монопольного захвата шины.

Система работает следующим образом.

Всем используемьгм в системе процессорам присваиваются номера от О до 7. В. каждом процессоре перемычками на коммутационной панели 42 устанавливают код, соответствующий присвоенному номеру, на коммутационной панели 43 перемычку устанавливают таким образом, чтобы обеспечить соединение выхода элемента ИЛИ 44 -с соответствующей линией запроса шины.

Сигнал Сброс, формируемый в системе при включении питания, устанавливает в ноль все разряды регистра 26 маски, снимая тем самым маскирование со всех запросов на захват шины, воздействуя на блок 22 начальной установки, записывает в счетчик 17 допустимого времени захвата шины число, соответствующее времени ВЕЛЮЛ- нения одного цикла команды при установленной в системе частоте следования тактовых импульсов, обнуляет .ч счетчик 37, устанавливая таким образом высший приоритет для нулевого запроса на захват шины и вьщавая в систему подтверждение запроса на захват шины для процессора с номером О, т.е. он становится активным.

На выходе схемы 45 сравнения процессора с номером О устанавливается сигнал подтверждения, разрешающий прохождение сигналов адреса, данных и управления на шину 13 через формирователи 39 - 41 и запрещающий выдачу запроса на захват шины (3MUO).

Во всех остальных процессорах схемы 46 сравнения не зафиксированы .совпадения кодов подтверждения запросов на захват шины с кодами, установленными ,на коммутационных панелях 42, формирователи адреса, данных и управления 39-41 закрыты, а элемент И 47 открыт, что запрещает выдачу на шину сигналов адреса, данных и управления и разрешает вьщачу на шину запросов ЗМ1111-ЗМШ7.

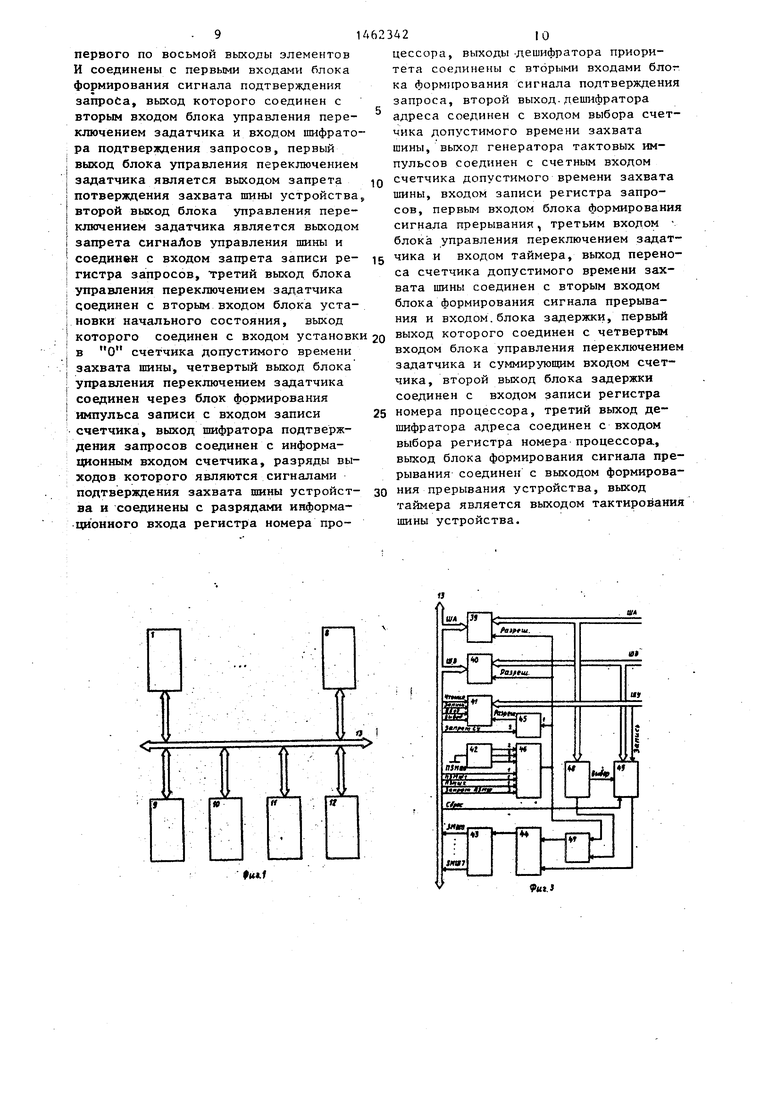

Операция смены задатчика на шине начинается с момента, когда один или несколько сразу процессоров с номерами 1-7 обращаются к устройствам, размещенным на шине. На выходах 1 дешифраторов 48 адреса появляются сигналы запроса, которые, пройдя через открытые элементы И 47 и коммутационные панели 43, поступают на входы регистра 20 запросов модуля МСК. Запись в регистр 20 запросов осуществляется по сигналу тактового генератора. С выхода регистра 20 . запросов сигналы запросов на захват шины через открытые элементы И 27-34 поступают на входы блока 35. На выходе блока 35 появляется сигнал подтверждения запроса на захват шины для процессора с наименьшим номером, т.е. обладающим на настоящий момент времени наивысшим приоритетом. Сигналы подтверждения запроса с выхода блока 35 поступают на входы блока 23 управления переключением задатчика и входы шифратора 36, с выхода которого в виде двоичного кода, соответствующего номеру процессора с наивысшим приоритетом, запрашивающим захват шины, поступаю на информационные входы счетчика 37 Сигналы управления (чтение, запись, ввод, вывод) с шины поступаю на входы элемента ИЛИ 14, выход котрой соединен с первым входом блока 23 управления переключением задатчика. По заднему фронту любого сигнала управления, т.е. в конце

каждого цикла выполнения команды, блок 23 управления переключением задатчика анализирует состояние выхо

10

20

- . .

23424

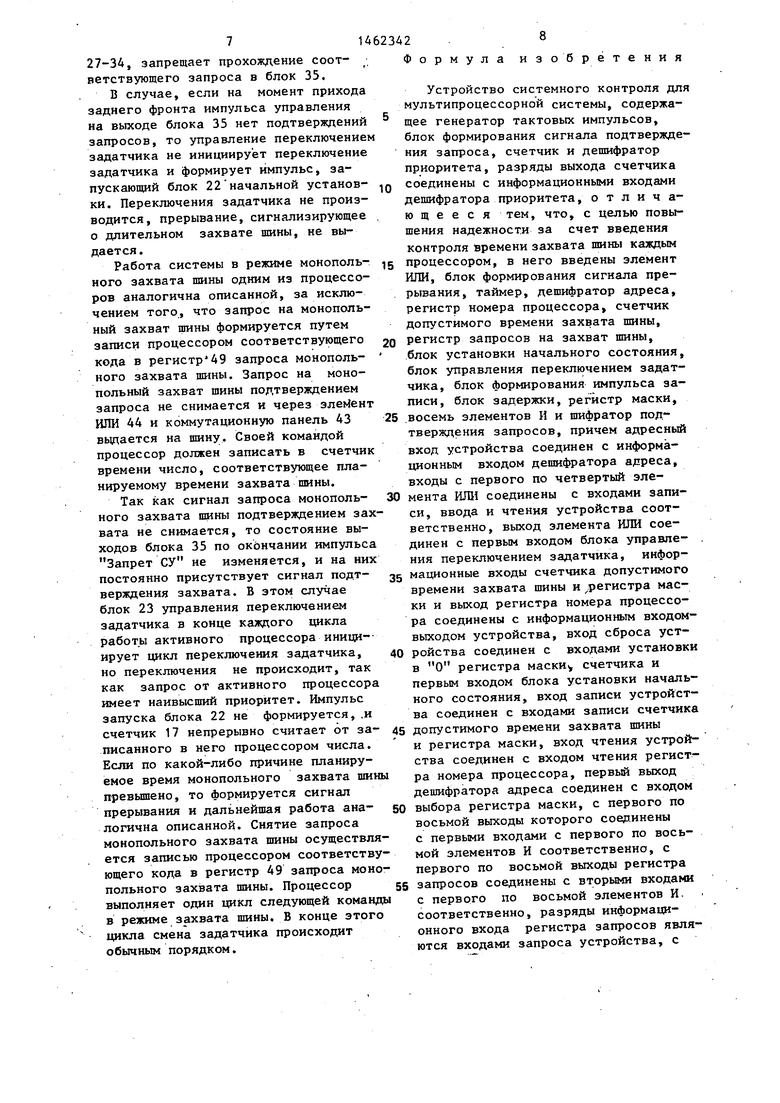

дов блока 35. Если хотя бы на одном из выходов блока 35 присутствует сигнал подтверждения запроса, то это означает, что еше хотя бы один процессор, кроме активного, требует захвата шины для вьтолнения обмена, и начинается цикл переключения задатчика (фиг. 4).

Со второго выхода блока 23 управления переключением задатчика вьща- ется сигнал Запрет СУ, запрещающий вьщачу сигналов управления из процессоров и запись запросов на захват 15 шины в регистр 20 запросов. Сигнал запрета, воздействуя через первый И 45, закрывает формирователь 41 сигналов управления активного процессора. Состояние формирователей 41 сигналов управления других процессоров не изменяется, так как они закрыты отсутствием сигнала подтверждения с выходов схем 46 сравнения.

С задержкой на один период частоты 25 генератора 21 ия блока 23 управления переключением задатчика выдается сигнал Запрет ПЗМШ, который запрещает срабатывание схем 46 сравнения в процессорах, в результате чего 30 в активном процессоре на выходе

схемы 46 сравнения снимается сигнал Подтверждение 0 и формирователи 39 и 40 адреса и данных закрываются, отключая тем самым шины адреса и данных активного процессора от шины. Второй элемент И 47 активного процессора открывается, пропуская тем самым на шину сигнал запроса на захват мультишины с выхода дешифратора 48 адреса (если сигнал имеется). Однако изменения, состояния выходов блока 35 не произойдет, так как запись в регистр 20 запроса запрещена сигналом Запрет СУ.

Одновременно с сигналом Запрет ПЗШ из блока 23 управления переключением задатчика выдается сигнал записи кода подтверждения запроса на захват шины, который, проходя через блок 24 формирования импульса записи, поступает на вход записи счетчика 37, и код подтверждения запроса на захват шины записывается в счетчик 37. Сигналы с выхода счетчика 37 поступают на дешифратор 38, на выходе которого появляется сигнал приоритета, устанавливая высший приоритет обслуживаемому в данный момент процессору.

40

45

50

Код подтверяздения захвата шины по линиям ПЗМШО-ПЗМШ2 поступает на входы схем 46 сравнения. По окончани сигнала Запрет ПЗМШ схема 46 сравнения в процессоре, номер которого соответствует коду на линиях ПЗШО- ПЗШ12, формирует на своем выходе сигнал Подтверждение,и формирователи ,39 и 40 адреса и данных этого процессора открываются, пропуская сигналы адреса и данньк на шину. Сигнал Подтверждение, воздействуя на второй элемент И 47, запрещает вьща- чу на шину запроса на захват шины от этого процессора.

Формирователи 41 сигналов управления остаются закрытыми из-за при-, сутствия на входах элементов И 45 сигнала Запрет СУ. С задержкой на один период частоты генератора 21 снимается сигнал Запрет СУ, и формирователь 41 в процессоре, номер которого соответствует коду подтверждения на линиях ПЗМШО-ПЗИИ1 открывается, пропуская на шину сигналы управления, и цикл переключения за- датчика завершается.

По окончании импульса Запрет СУ запись в регистр 20 запросов возобновляется, новое состояние линий запроса ЗМШО-ЗШ17 записывается в регистр 20 запросов, что приводит к изменению состояния выходов блока 35 Если на выходах блока 35 имеется сигнал подтверждения запроса на захват шины, то по окончании Цикла обмена процесс переключения задатчика повторяется.

Защита от несанкционированно долгого захвата мультишины осуществляется следующим образом. По окончании сигнала Запрет СУ возобновляется за,пись запросов в регистр 20 запросов. Если переключение задатчика произошло, то активный модуль к этому моменту времени уже снял свой запрос на захват шины. Состояние регистра 20 запросов изменяется, что приводит к-изменению состояния выходов блока 35 (фиг. 6). Совпадение изменения состояния выходов блока 35 сигналом Сброс длительностью в один период: частоты ген1ератора 21, формируемЬго блоком 23 управления переключением задатчика нeпocpeдcт-. веяно за импульсом Запрет СУ, приводит к срабатыванию блока 22, к в

. .

10

15

20

25

и. 4623426

счетчик 17 записывается число, соответствующее времени, достаточному для вьшолнения одного цикла команды с учетом допустимого времени ожидания ответа от внешнего устройства. На счетный вход счетчика 17 поступают импульсы с выхода генератора 21. С приходом каждого импульса тактового генератора число, записанное в счетчике, уменьшается на единицу. Если импульс с блока 22 начальной установки не поступил до того момента, когда счетчик установится в ноль, и не записал в него новое значение кода начальной установки, то принимается решение о несанкционированно долгом захвате шины, и на выходе счетчика 17- формируется импульс, . который через блок 25 задержки поступает на вход записи регистра 15 и записывает в «его код подтверждения запроса, соответствующий номеру ак- ., тивного в этот момент процессора, длительно захватившего шину. С задержкой, достаточной для записи кода подтверждения запроса в регистр 15, с первого выхода блока 25 задержки на счетный вход счетчика 37 поступает импульс, вызывающий изменение состояния счетчика 37 на единицу, т.е. происходит принудительное изменение приоритетов запросов процессоров. Импульс с первого выхода блока 25 задержки поступает так же на четвертый вход блока 23 управления переключением задатчика, что инициирует цикл переключения задатчика на ашне уже с новыми приоритетами для каждого из процессоров. Сигнал с выхода счетчика 17 поступает также на второй вход блока 18 формирования сигнала прерывания. С выхода блока 18 формирования сигнала прерывания импульс выдается по шине на соответствующие входы прерывания процессоров, которые в соответствии с принятым с системе протоколом, считывая номер процессора из регистра 15, принимают решение о причине длительного захвата шины. Если принято решение о неисправности одного из процессо30

35

40

45

50

ров, то он может быть исключен из дальнейшей работы в системе путем наложения на его запрос маски. Наложение маски осуществляется записью соответствующего кода в регистр 26 маски. Сигнал с выхода регистра 26 маски, воздействуя на элементы И

27-34, запрещает прохождение соот- ; ветствующего запроса в блок 35.

В случае, если на момент прихода заднего фронта импульса управления на выходе блока 35 нет подтверждений запросов, то управление переключением задатчика не иницииру ет переключение задатчика и формирует импульс, запускающий блок 22 начальной установ- кн. Переключения задатчика не производится, прерывание, сигнализирующее о длительном захвате шины, не выдается.

Работа системы в режиме монопольного захвата шины одним из процессоров аналогична описанной, за исключением того, что запрос на монопольный захват шины формируется путем записи процессором соответствующего кода в регистр 49 запроса монопольного захвата шины. Запрос на монопольный захват шины подтверждением запроса не снимается и через элемент ИЛИ 44 и коммутационную панель 43 вьщается на шину. Своей командой процессор должен записать в счетчик времени число, соответствующее планируемому времени захвата шины.

Так как сигнал запроса монопольного захвата шины подтверждением захвата не снимается, то состояние выходов блока 35 по окончании импульса Запрет СУ не изменяется, и на них постоянно присутствует сигнал подтверждения захвата. В этом случае блок 23 управления переключением задатчика в конце каждого цикла работы активного процессора инициирует цикл переключения задатчика.

но переключения не происходит, так как запрос от активного процессора имеет наивысший приоритет. Импульс запуска блока 22 не формируется, ,и счетчик 17 непрерывно считает от записанного в него процессором числа. Если по какой-либо причине планируемое время монопольного захвата ши превышено, то формируется сигнал прерывания и дальнейшая работа аналогична описанной. Снятие запроса монопольного захвата шины осуществлется записью процессором соответствющего кода в регистр 49 запроса монпольного захвата шины. Процессор выполняет один цикл следующей коман в режиме захвата шины. В конце этог цикла смена задатчика происходит обычным порядком.

Формула изобретения

5

0

5

55

Устройство системного контроля для мультипроцессорной системы, содержащее генератор тактовых импульсов, блок формирования сигнала подтверждения запроса, счетчик и дешифратор приоритета, разряды выхода счетчика соединены с информационными входами дешифратора приоритета, отличающееся тем, что, с целью повьг- шения надежности за счет введения контроля времени захвата шины каждым процессором, в него введены элемент ИЛИ, блок формирования сигнала прерывания, таймер, дешифратор адреса, регистр номера процессора, счетчик допустимого времени захвата шины, регистр запросов на захват шины, блок установки начального состояния, блок управления переключением задатчика, блок формирования импульса записи, блок задержки, регистр маски, восемь элементов И и шифратор подтверждения запросов, причем адресный вход устройства соединен с информационным входом дешифратора адреса, входы с первого по четвертый эле- 30 мента ИЛИ соединены с входами записи, ввода и чтения устройства соответственно, выход элемента ИЛИ соединен с первым входом блока управления переключением задатчика, инфор- 35 мационные входы счетчика допустимого времени захвата шины и регистра маски и выход регистра номера процессора соединены с информационным входом- выходом устройства, вход сброса уст- 40 ройства соединен с входами установки в О регистра маскиу счетчика и первым входом блока установки начального состояния, вход записи устройства соединен с входами записи счетчика 45 допустимого времени захвата шины и регистра маски, вход чтения устройства соединен с входом чтения регистра номера процессора, первый выход дешифратора адреса соединен с входом 50 выбора регистра маски, с первого по восьмой выходы которого соед.инены с первыми входами с первого по восьмой элементов И соответственно, с первого по восьмой выходы регистра запросов соединены с вторыми входами с первого по восьмой элементов И- соответственно, разряды информационного входа регистра запросов являются входами запроса устройства, с

первого по восьмой выходы элементов И соединены с первыми входаму блока формирования сигнала подтверждения запроса, выход которого соединен с вторым входом блока управления переключением задатчика и входом шифратора подтверждения запросов, первый выход блока управления переключением задатчика является выходом запрета потверждения захвата шины устройства, второй выход блока управления переключением задатчика является выходом запрета сигналов управления шины и соединен с входом запрета записи регистра запросов, третий выход блока управления переключением задатчика соединен с вторым входом блока установки начального состояния, выход

цессора, выходы -дешифратора приоритета соединены с вторыми входами бло ка формирования сигнала подтверждени запроса, второй выход-дешифратора

адреса соединен с входом выбора счет чика допустимого времени захвата шины, выход генератора тактовых импульсов соединен с счетным входом счетчика допустимого времени захвата шины, входом записи регистра запросов, первым входом блока формировани сигнала прерывания, третьим входом блока управления переключением задат

5 чика и входом таймера, выход перено са счетчика допустимого времени захвата шины соединен с вторым входом блока формирования сигнала прерывания и входом.блока задержки, первый

которого соединен с входом установки 2о выход которого соединен с четвертым

входом блока управления переключение задатчика и суммируюшим входом счетчика, второй выход блока задержки соединен с входом записи регистра

в о счетчика допустимого времени захвата шины, четвертый выход блока управления переключением задатчика соединен через блок формирования импульса записи с входом записи счетчика, выход шифратора подтверждения запросов соединен с информационным входом счетчика, разряды выходов которого являются сигналами подтверждения захвата шины устройства и соединены с разрядами информационного входа регистра номера про

цессора, выходы -дешифратора приоритета соединены с вторыми входами блог ка формирования сигнала подтверждения запроса, второй выход-дешифратора

адреса соединен с входом выбора счетчика допустимого времени захвата шины, выход генератора тактовых импульсов соединен с счетным входом счетчика допустимого времени захвата шины, входом записи регистра запросов, первым входом блока формирования сигнала прерывания, третьим входом блока управления переключением задатчика и входом таймера, выход переноса счетчика допустимого времени захвата шины соединен с вторым входом блока формирования сигнала прерывания и входом.блока задержки, первый

2о выход которого соединен с четвертым

входом блока управления переключением задатчика и суммируюшим входом счетчика, второй выход блока задержки соединен с входом записи регистра

25 номера процессора, третий выход дешифратора адреса соединен с входом выбора регистра номера процессора, выход блока формирования сигнала прерывания соединен с выходом формирова30 ния прерывания устройства, выход

таймера является выходом тактирования шины устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Электронная вычислительная машина для ускоренной обработки запросов прерываний | 1988 |

|

SU1621029A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1984 |

|

SU1332326A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1982 |

|

SU1269142A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении мультипроцессорных систем. Цель изобретения - повышение надежности системы за счет введения контроля времени захвата шины каждым процессором. Устройство содержит дешифратор 16 адреса, счетчик 17 допустимого времени захвата шины, регистр 26 маски, генератор 21 тактовых импульсов, блок 22 установки начального состояния, регистр 20 запросов и др. блоки. На счетчике 17 контролируется

$м1

9ut.i

Гг JOJTJTJTJ lJTJTJTJnJTJTJT-nJTJnj

СУК

tM.fa.3unp. го 9м. К CU5 ZlA

Запр.СУ Запрет ПЗНШ

Уст Се. П

Запрос fh ,- Подт6ер пдение

U

игЛ

Фиг, 6

| Патент США № 4418385, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Всасывающе-нагнетательное устройство для передвижения судов | 1925 |

|

SU1800A1 |

| Техническое описание и инструкция по эксплуатации | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-02-28—Публикация

1987-01-04—Подача