Изобретение относится к автомати ке, вычислительной технике и может быть использовано для регистрации сигналов неисправности от логических блоков, работающих последовательно во времени.

Известно устройство для фиксации сигналов ошибки логического блока, содержащее элементы И, НЕ, запрета, счетчик тактовых импульсов ij .

Однако это устройство, хотя и позволяет определить номер такта в момент возникновения ошибки, характеризуется малой достоверностью проверки блоков, поскольку оно нечувствительно к сигналам ошибки, не совпадающим по времени с синхронизирующим импульсом.

Наиболее близким к предлагаемому по технической сущности является устройство для регистрации сигналов неисправности, содержащее первый элемент И, первьш триггер, элемент запрета и счетчик, причем первый вход первого элемента И является информационным входом устройства, выход первого элемента И соединен с -ВХОДОМ установки в ноль первого триггера, инверсный вьшод которого подключен к первому ВХОДУ элемента запрета, выход которого соединен с входом счетчика, блок вьщеления последнего импульса пачки, формиро ватель импульсов, второй элемент И, второй триггер и элемент задержки,вход которого является синхронизирующим входом устройства, выход элемента задержки подключен к входу установки в единицу второго триггера, прямой выход которого соединен с первым входом второго элемента И, второй вход которого соединен с вьпсодом формирователя импульсов, выход второго элемента И подключен к второму входу первого элемента И ;и входу блока выделения последнего импульса пачки, выход которого соедй нен с вторым входом элемента запрета и входом установки в ноль второго триггера 2J .

Недостатками известного устройства являются невозможность проверки нескольких блоков с фиксацией момента, появления сигналов неисправности в каждом из них, а также невозможность подсчета общего количес ва сигнал ов неисправности, что -затрудняет диагностику. Кроме того, использование этого устройства для фиксации моментов сбоев неустойчиво работающих блоков с целью локализации места неисправности, вызывающей сбои, неэффективно, так как по первому сбою устройсво блокируется и последующие сбои не фиксируются.

Цель изобретения - повышение информативности результатов регистрации сигналов неисправности логических блоков.

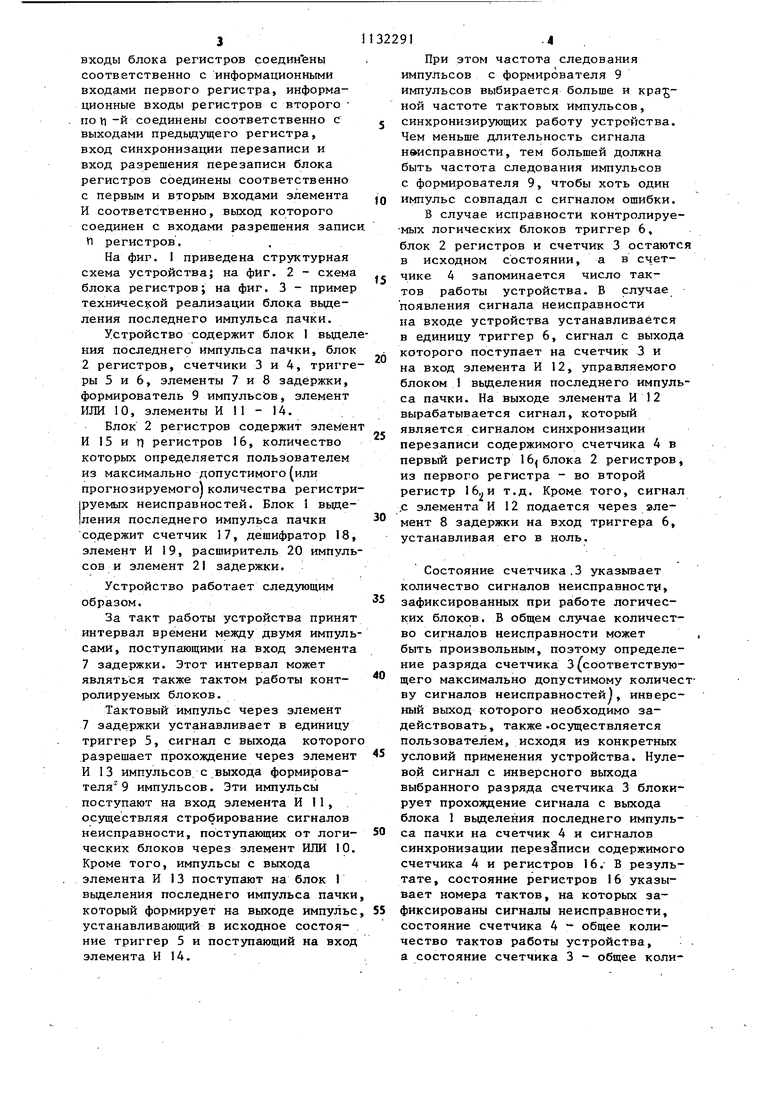

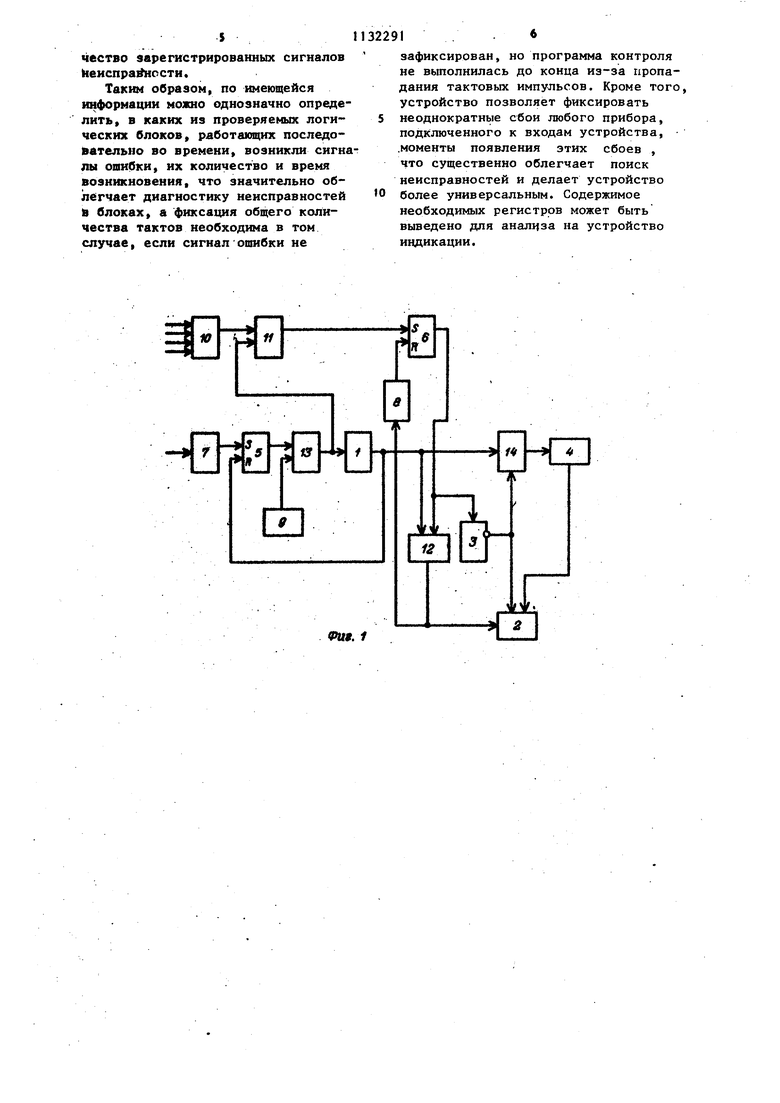

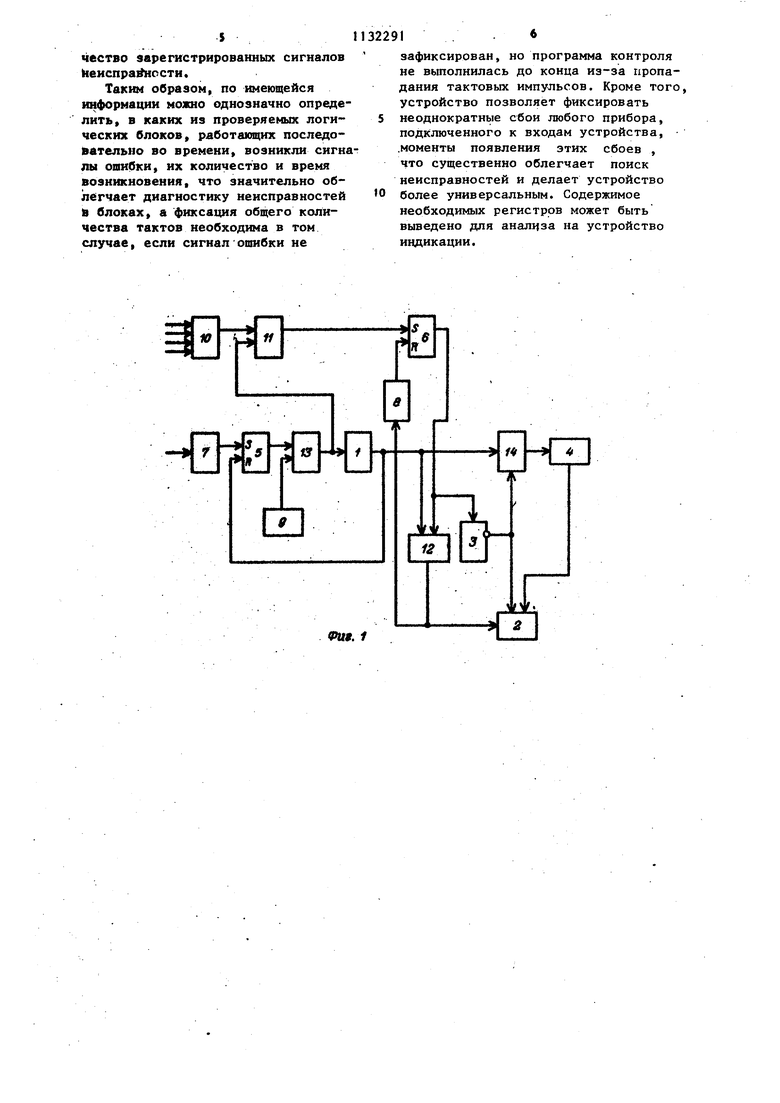

Поставленная цель достигается тем, что в устройство для регистрации сигналов неисправности,содержащее блок вьщеления последнего импульса пачки, формирователь импульсов, два триггера, два элемента И, первый элемент задержки и первый счетчик, причем тактовый вход устройства соединен через первый элемент задержки с 5 -входом первого триггера, выход которого соединен с первым входом первого элемента И, выход первого элемента И соединен с первым входом второго элемента И и входом блока выделения последнего импульса пачки, выход которого соединен с R-входом первого триггера, выход формирователя импульсов соединен с вторым входом первого элемента И, введены второй счетчик, второй элемент задержки, элемент ИЛИ, третий и четвертый элементы И и блок регистров, причем информационные входы ус/ройства соединены с входами элемента ИЛИ, выход которого соединен с вторым входом второго элемента И, выход второго элемента И соединен с 5-входом второго триггера, вь1ход которого соединен с первым входом третьего элемента И и счетным входом первого счетчика, выход бл;ока выделения последнего импульса пачки соединен с вторым входом третьего элемента И и первым входом четвертого элемента И, выход которого соеди: ен со счетным входом второго счетчика, выход третьего элемента И соединен с синхровходом блока регистров и через второй элемент задержки с R -входом второго триггера, инверсный выход первогосчетчика соединен с вторым входом четвертого элемента И и входом разрешения перезаписи блока регистров, информационные входы которого соединены с выходами второго счетчика, блок регистров содержит элемент И и П регистров, причем информационные входы блока регистров соединены соответственно с информационными входами первого регистра, информационные входы регистров с второго поц -и соединены соответственно с выходами предыдущего регистра, вход синхронизации перезаписи и вход разрешения перезаписи блока регистров соединены соответственно с первым и вторым входами элемента И соответственно, вькод которого соединен с входами разрешения запис И регистров.. На фиг. 1 приведена структурная схема устройства; на фиг. 2 - схема блока регистров; на фиг. 3 - пример технической реализации блока выделения последнего импульса пачки. Устройство содержит блок 1 выдел ния последнего импульса пачки, блок 2 регистров, счетчики 3 и 4, тригге ры 5 и 6, элементы 7 и 8 задержки, формирователь 9 импульсов, элемент ИЛИ 10, элементы И 11 - 14. Блок 2 регистров содержит элемен И 15 и п регистров 16, количество которых определяется пользователем из максимально допустимого(или прогнозируемого количества регистри руемых неисправностей. Блок 1 вьщеления последнего импульса пачки содержит счетчик 17, дешифратор 18 элемент И 19, расширитель 20 импуль сов и элемент 21 задержки. Устройство работает следующим образом. За такт работы устройства принят интервал времени между двумя импуль сами, поступающими на вход элемента 7 задержки. Этот интервал может являться также тактом работы контролируемых блоков. Тактовый импульс через элемент 7 задержки устанавливает в единицу триггер 5, сигнал с выхода которог разрешает прохождение через элемент И 13 импульсов с выхода формирователя 9 импульсов. Эти импульсы поступают на вход элемента И 11, осуществляя стробирование сигналов неисправности, поступающих от логических блоков через элемент ИЛИ 10 Кроме того, импульсы с выхода элемента И 13 поступают на блок 1 выделения последнего импульса пачки который формирует на выходе импульс устанавливающий в исходное состояние триггер 5 и поступающий на вход элемента И 14. 91-4 При этом частота следования импульсов с формирователя 9 импульсов выбирается больше и Kpajной частоте тактовых импульсов, синхронизирующих работу устройства. Чем меньше длительность сигнала н исправности, тем большей должна быть частота следования импульсов с формирователя 9, чтобы хоть один импульс совпадал с сигналом ошибки. В случае исправности контролируемых логических блоков триггер 6, блок 2 регистров и счетчик 3 остаются в исходном состоянии, а в счетчике 4 запоминается число тактов работы устройства. В случае появления сигнала неисправности на входе устройства устанавливается в единицу триггер 6, сигнал с выхода которого поступает на счетчик 3 и на вход элемента И 12, управляемого блоком 1 вьщеления последнего импульса пачки. На выходе элемента И 12 вырабатывается сигнал, который является сигналом синхронизации перезаписи содержимого счетчика 4 в первый регистр 16jблока 2 регистров, из первого регистра - во второй регистр 16,, и т.д. Кроме того, сигнал .с элемента И 12 подается через элемент 8 задержки на вход триггера 6, устанавливая его в ноль. Состояние счетчика,3 указьгеает количество сигналов неисправности, зафиксированных при работе логическ:их блоков, В общем случае количество сигналов неисправности может быть произвольным, поэтому определение разряда счетчика 3(соответствующего максимально допустимому количеству сигналов неисправностей), инверсный выход которого необходимо задействовать, также-осуществляется пользователем, исходя из конкретных условий применения устройства. Нулевой сигнал с инверсного выхода выбранного разряда счетчика 3 блокирует прохождение сигнала с выхода блока 1 выделения последнего импульса пачки на счетчик 4 и сигналов синхронизации перезЕписи содержимого счетчика 4 и регистров 16. В результате, состояние регистров 16 указывает номера тактов, на которых зафиксированы сигналы неисправности, состояние счетчика 4 - общее количество тактов работы устройства, а состояние счетчика 3 - общее коли$ 1

«iecTBO зарегистрированных сигналов йенспра о сти,

Таким образом, по имеющейся информации можно однозначно опредцелить, в каких из проверяемых логических блоков, работахяцих последовательно во времени, возникли сигналы ошибки, их количество и время возникновения, что значительно облегчает диагностику неисправностей И блоках, а фиксация общего количества тактов необходима в том случае, если сигнал ошибки не

32291

зафиксирован, но программа контроля не выполнилась до конца из-за пропадания тактовых импульсов. Кроме того, устройство позволяет фиксировать 5 неоднократные сбои любого прибора, подключенного к входам устройства, .моменты появления этих сбоев , что существенно облегчает поиск неисправностей и делает устройство О более универсальным. Содержимое необходимых регистров может быть выведено для анализа на устройство индикации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации сигналов неисправности | 1985 |

|

SU1278859A1 |

| Устройство для регистрации сигналов неисправности | 1979 |

|

SU864290A1 |

| Устройство для контроля последовательности сигналов | 1987 |

|

SU1462493A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1536387A1 |

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1238093A1 |

| Устройство для имитации сбоев и неисправностей цифровой вычислительной машины | 1985 |

|

SU1265779A1 |

| Устройство для имитации неисправностей | 1985 |

|

SU1273933A1 |

| Устройство для имитации неисправностей | 1984 |

|

SU1164715A1 |

| Пересчетное устройство | 1980 |

|

SU921093A1 |

| Устройство для имитации неисправностей | 1985 |

|

SU1283775A1 |

УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ СИГНАЛОВ НЕИСПРАВНОСТИ, содержащее блок вьщеления последнего импульса пачки, формирователь импульсов, два триггера, два элемента И, первый элемент задержки и первый счетчик, причем тактовый вход устройства соединен через первый элемен.т задержки с 5 -входом первого триггера, выход которого соединен с первым входом первого элемента И, выход первого элемента И соединен с первым входом второго элемента И и входом блока выделения последнего импульса пачки, выход которого соединен с R-входом первого триггера, выход формирователя импульсов соединен с вторым входом первого элемента И, отличающееся тем, что, с целью повьпиения информативности результатов регистрации, в него введены второй счетчик, второй элемент задержки, элемент ШШ, третий и четвертый элементы И и блок регистров, причем информационные входы устройства соединены с входами элемента ИЛИ, выход которого соединен с вторым входом второго элемента И, выход второго элемента И соединен с 5 -входом второго триггера, выход которого соединен с первым входом третьего элементу И и счетным входом первого счетчика, выход блока вьщеления последнего импульса пачки соединен с вторь№1 входом третьего элемента И и первымвходом четвертого элемента И, выход которого соединен со счетным входом второго счетчика, выход третьего элемента И соединен с синхровходом блока регистров и через второй элемент задержки с R -входом второго триггера,, инверсный выход первого счетчика соединен с вторым входом четвертого элемента И и входом разрешения перезаписи блока регистров информационные входы которого соединены с выходами второго счетчика, блок регистров содержит элемент И и п регистр.ов, причем информационСО ные входы блока регистров соединены о соответственно с информационными N9 входами первого регистра, информаци-. СО онные входы регистров с второго по h-u соединены соответственно с выходами предьщущего регистра, вход синхронизации перезаписи и вход разрешения перезаписи блока регистров соединены соответственно с пер- , вым и вторым входами элемента И соответственно, выход которого соединен с входами разрешения записи п регистров.

15

16i

Pz/5. 2

-

17

18

20

21

ФИ8. 3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

Авторы

Даты

1984-12-30—Публикация

1982-12-23—Подача