- Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах с повышенными требованиями к информационной надежности.

Известно запоминающее устройство содержащее блок памяти, состоящий и ферритовых запоминающих матриц, подключенных к разрядным генераторам тока, к ключам записи и считывания Щ .

В этом устройстве достигнуто увеличение емкости за счет специального соединения адресных шин, но не предусмотрено дискретное изменение времени подачи стробирующего сигнала на усилитель считывания в зависимости от адреса опрашиваемых запоминающих линеек, что снижает одну из самых важных качественных характеристик запоминающих устройств, т.е. информационную надежность.

Наиболее близким техническим решением к изобретению является запоминающее устройство, родержащее накопитель, дополнительную числовую линейку, формирователи адресных и разрядных токов, формирователь стробирующего сигнала, регистр числа, усилители считывания, дешифратор адреса 2 .

Однако в известном устройстве отсутствует возможность изменения уровня стробирования (дискриминации) сигнала чтения в зависимости от- естественного изменения амплитуд сигнала чтения из-за различных условий распространения его по разрядно-счигывающей линии, что снижает надежность устройства.

Целью изобретения является повышение надежности запоминающего устройства за счет .обеспечения оптималного уровня стробирования сигналов считывания.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее регистр числа, один из входов которого подключены к выходам усилителей считывания, а выходы к одним из входов основных формирователей разрядных токов, основной накопитель информации, входы которого соединены с выходами основных формирователей разрядных и адресных токов, а один из выходов - с информационными входами усилителей считывания, одыи из управляющих входов которых подключены к-выходу формирователя стробирующего сигнала, вход которого соединен с выходом усилителя сигналов, вход которого подключен к информационному выходу дополнительного накопителя, дешифратор адреса, выходы которого подключены к входам основных формирователей адресных токов, дополнительный формирователь разрядных токов, которого соединен с одним из входов дополнительного накопителя, другие входы которого подключены к другим выходам основного накопителя введены дополнительные формирователи адресных токов и дискриминаторы, выходы которых подключены к другим управляющим входам усилителей считывания, а входы - к выходам дополнительных формирователей адресных токов, одни из входов которых соединены с управляющими выходами дополнительного накопителя, а другие входы объединены и являются одним из входов устройства.

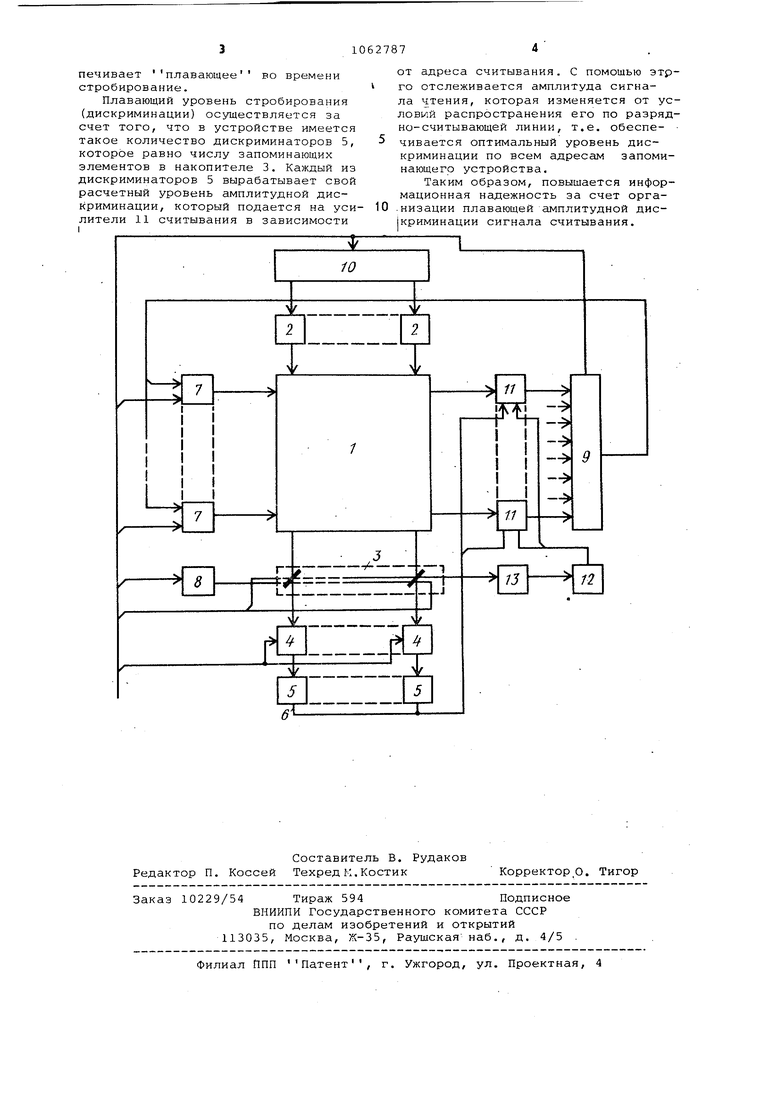

На чертеже изображена структурная . схема предлагаемого устройства.

Устройство содержит основной накопитель 1, основные формирователи 2 адресных токов, дополнительный накопитель 3, дополнительные формирователи, 4 адресных токов, дискриминаторы 5, имеющие выходы 6, основные формирователи 7 разрядных токов дополнительный формирователь 8 разрядных токов, регистр 9 числа, дешифратор 1„0 адреса, усилители 11 считывания, формирователь 12 стробирующего сигнала, усилитель 13 сигналов .

В режиме записи на регистр 9 подется код числа, который устанавливает триггеры регистра 9 в определенное состояние. Затем после поступления на формирователи 7 разрешающего сигнала на входы накопителя 1 подаются разрядные токи записи, а с некоторой задержкой по времени (с целью уменьшения помех) на дешифратор 10 адреса поступает код адреса числа, срабатывают соответствующие формирователи 2, 4, 8.

В результате этого в соответствующую ячейку памяти накопителя 1 происходит запись кода числа, а в запоминающий элемент накопителя 3-1 Количество запоминающих элементов в накопителе 3 зависит от схемы дешифратора 10 адреса, например устройства, выполненного по системе 2Д емкостью 256 слов, где число запоминающих элементов равно 8. Аналогично происходит запись кода числ

накопитель 3

в накопитель 1 и

при считывании в момент регенерации. В режиме считывания на входы усилителей 11 считывания поступают сигналы чтения, а сигнал чтения 1 из накопителя 3 поступает на вход усилителя 13. Задержка по времени этого сигнала соответствует приблизительно задержке сигнала чтения, поступившего на усилитель 11 считывания. Этот сигнал усиливается на усилителе 13 и запускает формирователь 12,. с выхода которого сигнал стробирования подается на входы усилителей 11 считывания, что обеспечивает плавающее во времени стробирование.

Плавающий уровень стробирования (дискриминации) осуществляется за счет того, что в устройстве имеется такое количество дискриминаторов 5, которое равно числу запоминающих элементов в накопителе 3. Каждый из дискриминаторов 5 вырабатывает свой расчетный уровень амплитудной дискриминации, который подается на усиот адреса считывания. С помощью этрго отслеживается амплитуда сигнала чтения, которая изменяется от условий распространения его по разрядно- считывающей линии, т.е. обеспе- чивается оптимальный уровень дискриминации по всем адресам запоминающего устройства.

Таким образом, повышается информационная надежность за счет орга.низации плавающей амплитудной дис

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1982 |

|

SU1049969A1 |

| Запоминающее устройство | 1981 |

|

SU982093A1 |

| Запоминающее устройство | 1979 |

|

SU809350A1 |

| Запоминающее устройство | 1979 |

|

SU824304A1 |

| Запоминающее устройство | 1980 |

|

SU892475A1 |

| "Запоминающее устройство | 1979 |

|

SU809369A1 |

| Запоминающее устройство | 1975 |

|

SU627539A1 |

| Запоминающее устройство | 1977 |

|

SU733020A1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

| Запоминающее устройство | 1986 |

|

SU1361636A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее регистр числа, одни из входов которого подключены к выходг1М усилителей считывания, а-выходы к одним из входов основных формирователей разрядных токов, основной накопитель информации, входы которого соединены с выходами основных формирователей разрядных и адресных токов, а одни из выходов - с информационными входами усилителей считывания, одни из управляющих входов которых подключены к выходу формирователя стробирующего сигнала, вход которого соединен с выходом усилителя сигналов, вход которого подключен к информационному выходу дополнительного накопителя, дешифратор адреса, выходы которого подключены к входам основных формирователей адресных токов, дополнительный формирователь разрядных тотоков, выход которого соединен с одним из входов дополнительного накопителя, другие входы которого подключены к другим выходам основного накопителя, отличающееся тем, что, с целью повышения надежности устройства за счет обеспечения оптимального уровня стробирования сигналов считывания, в него S введены дополнительные формировате(Л ли адресных токов и дискриминаторы, выходы которых подключены к другим управляющим входам усилителей считывания, а входы - к выходам допол нительных формирователей адресных токов, одни из входов которых соединены с управляющими выходами дополнительного накопителя, а другие входы объединены и являются одним из входов устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство | 1970 |

|

SU809371A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Известия Ленинградского, электротехнического института, 1969, вып | |||

| Машина для разделения сыпучих материалов и размещения их в приемники | 0 |

|

SU82A1 |

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

Авторы

Даты

1983-12-23—Публикация

1982-10-29—Подача