1

Изобретение относится к запоминающим устройствам и может быть использовано для построения быстродействующих запоминающих устройств большого объема.

Известно запоминающее устройство, содержащее накопитель с основными и дополнительными разрядными шинами, адресный регистр, формирователь токов опроса, основные и дополнительные усилители-формирователи, линии задержки и регистр числа, причем для временной селекции используются сигналы, формируемые при помощи дополнительных разрядных шин f1.

Недостатком этого устройства является низкое быстродействие.

Наиболее близким к предлагаемому по технической сущности является запоминающее устройство, содержащее накопитель с адресными шинами, основными и дополнИтельньми разрядными шинами, адресньй регистр, основные усилители-формирователи.

ВХОДЫ которых подключены к выходам основных разрядных шин, дополнительные усилители-формирователи, входы которых подключены к выходам дополнительных разрядных шин, формирователь токов опроса, злемент задержки, схемы И и регистр числа f2.

Однако устройство имеет низкое быстродействие вследствие большого времени пробега информации от нако10пителя до регистра числа и нестабильности временного расположения сигналов из-за применения элементов И временной селекции.

Цель изобретения - повьшение

15 быстродействия устройства.

Поставленная цель достигается тем,что в запоминающее устройство, содержащее регистр адреса, регистр числа, формирователь тока опроса,

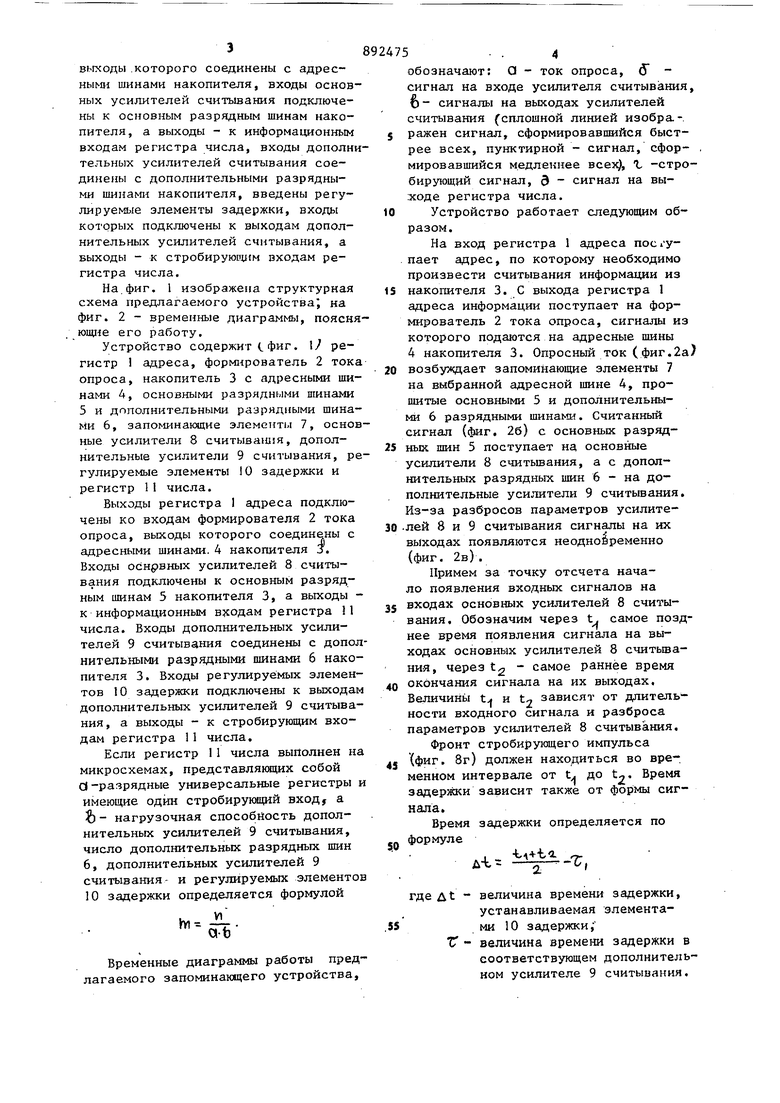

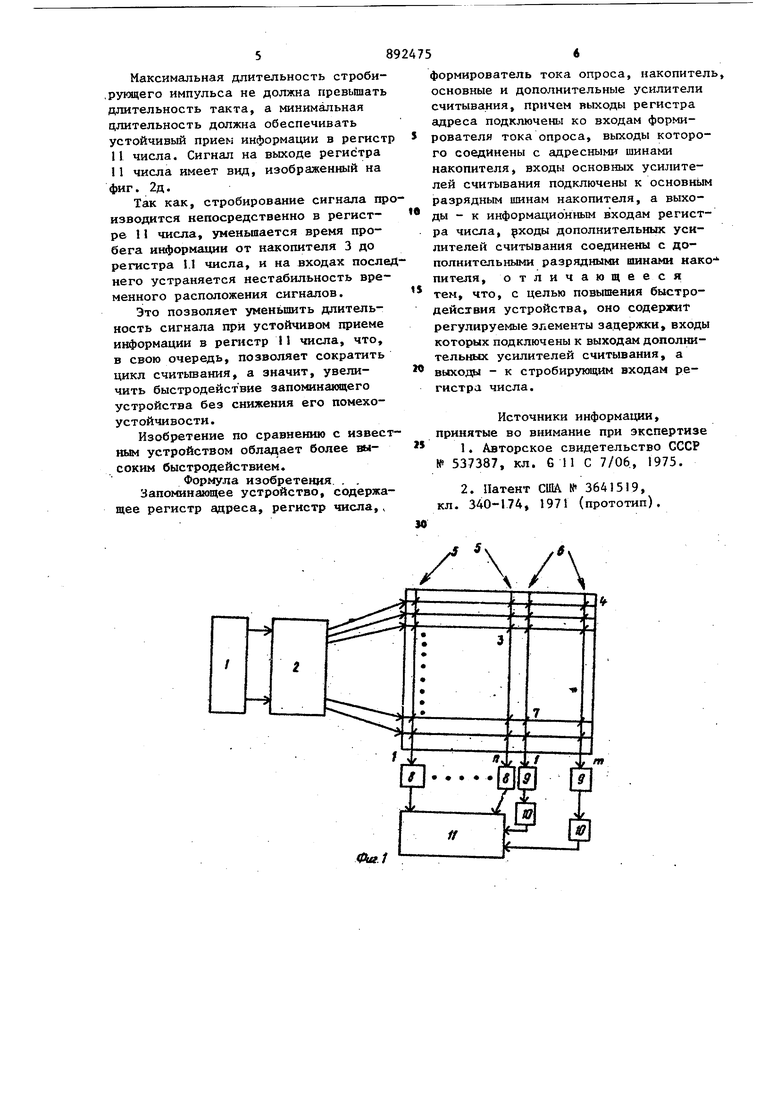

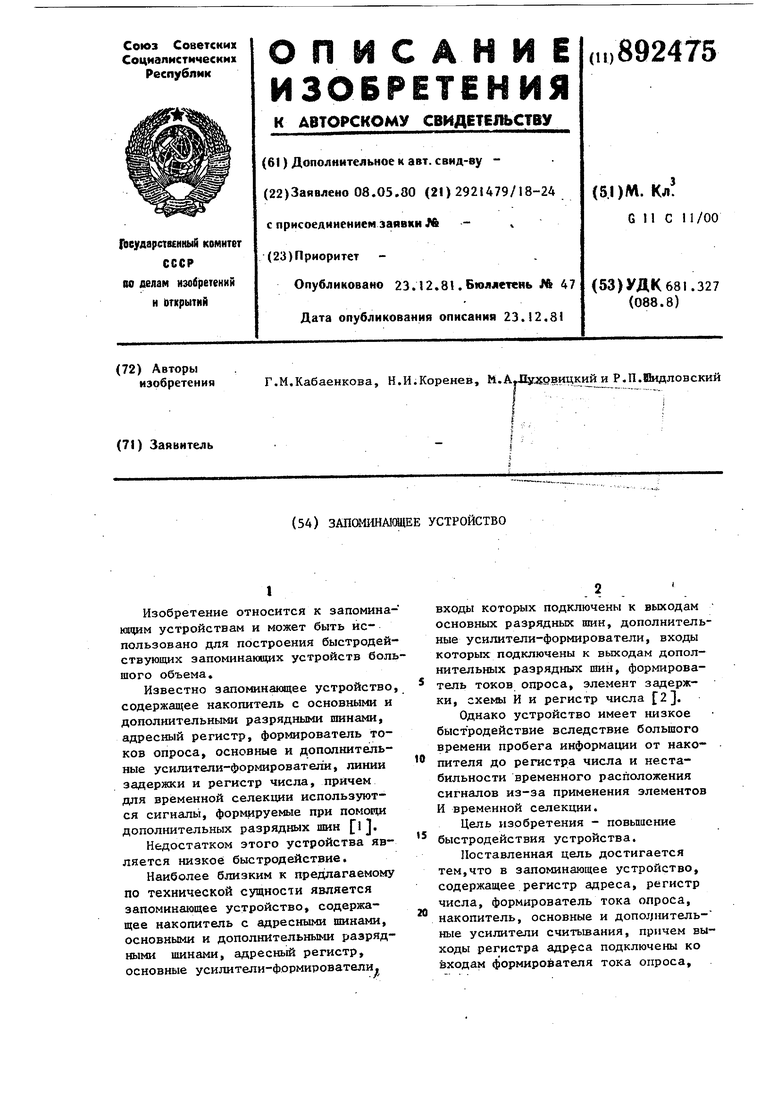

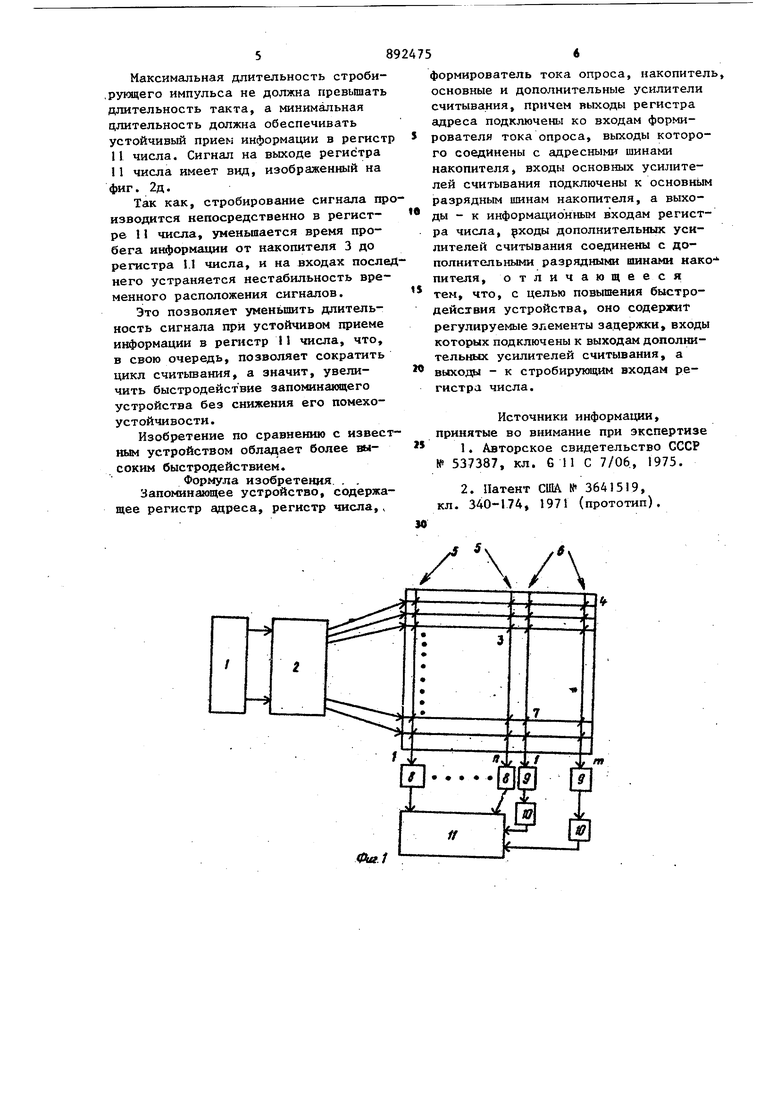

20 накопитель, основные и дoпoJ нитeльные усилители считывания, причем выходы регистра адреса подключены ко входам формирователя тока опроса. выходы .которого соединены с адресны в шинами накопителя, входы основ ных усилителей считьшания подключены к основным разрядным шинам накопителя, а выходы - к информационным входам регистра числа, входы дополн тельных усилителей считывания соединены с дополнительными разрядными шинами накопителя, введены регулируемые элементы задержки, входы которых подключены к выходам дополнительных усилителей считывания, а выходы - к стробирую11у1м входам регистра числа. На.фиг. 1 изображена структурная схема предлагаемого устройства на фиг. 2 - временные диаграммы, поясня ющие его работу. Устройство содержит (.фиг. l7 регистр 1 адреса, формирователь 2 тока опроса, накопитель 3 с адресными шинами А, основными разрядными шинами 5 и дополнительными разрядными шинами 6, запоминающие элементы 7, основ ные усилители 8 считывания, дополнительные усилители 9 считывания, ре гулируемые элементы 10 задержки и регистр 11 числа. Выходы регистра 1 адреса подключены ко входам формирователя 2 тока опроса, выходы которого соединены с адресными шинами. 4 накопителя 3. Входы оснрвных усилителей 8 считывания подключены к основным разрядным шинам 5 накопителя 3, а выходы к информационным входам регистра 11 числа. Входы дополнительных усилителей 9 считывания соединены с допол нительными разрядными пшнами 6 накопителя 3. Входы регулируемых элементов 10 задержки подключены к выходам дополнительных усилителей 9 считывания , а выходы - к стробирующим входам регистра 11 числа. Если регистр 11 числа выполнен на микросхемах, представляющих собой d-разрядные универсальные регистры и имеющие один стробирующий вход, а Ъ- нагрузочная способность дополнительных усилителей 9 считывания, число дополнительных разрядных шин 6, дополнительных усилителей 9 считывания- и регулируемых элементо 10 задержки определяется формулой Временные диаграммы работы пред лагаемого запоминающего устройства, 5 . . 4 обозначают: О - ток опроса, б сигнал на входе усилителя считывания, О - сигналы на выходах усилителей считывания (сплошной линией изобраражен сигнал, сформировавшийся быстрее всех, пунктирной - сигнал, сфор- , мировавшийся медленнее все, t -стробиру1ощий сигнал, 3 - сигнал на выходе регистра числа. Устройство работает следующим образом. На вход регистра 1 адреса nociyпает адрес, по которому необходимо произвести считывания информации из накопителя 3. С выхода регистра 1 адреса информации поступает на формирователь 2 тока опроса, сигналы из которого подаются на адресные шины 4 накопителя 3. Опросный ток (фиг.2а) возбуждает запоминающие элементы 7 на выбранной адресной шине 4, прошитые основными 5 и дополнительными 6 разрядными шинами. СчитаннЕ 1й сигнал (фиг, 2б) с основных разрядных шин 5 поступает на основные усилители 8 считьшания, а с дополнительньпс разрядных шин 6 - на дополнительные усилители 9 считьюания. Из-за разбросов параметров усилителей 8 и 9 считывания сигналы на их выходах появляются неодновременно (фиг. 2в). Примем за точку отсчета начало появления входных сигналов на входах основных усилителей 8 считывания. Обозначим через t. самое позднее время появления сигнала на выходах основных усилителей 8 считьшания, через tg - самое раннее время окончания сигнала на их выходах. Величины tj и t зависят от длительности входного сигнала и разброса параметров усилителей 8 считывания. Фронт стробирующего импульса (фиг. 8г) должен находиться во временном интервале от t до Время задержки зависит также от формы сигнала. Время задержки определяется по формуле л4. - Т Д-t- л- I где At - величина времени задержки, устанавливаемая элементами 10 задержки; Т - величина времени задержки в соответствующем дополнительном усилителе 9 считывания. Максимальная длительность стробирующего импульса не должна превьпиать длительность такта, а минимальная длительность должна обеспечивать устойчивый приеы информации в регист И числа. Сигнал на выходе регистра 11 числа имеет вид, изображенный на , стробирование сигнала пр изводится непосредственно в регистре 1 числа, уменьшается время пробега информации от накопителя 3 до регистра М числа, и на входах после него устраняется нестабильность вре манного расположения сигналов. Это позволяет уменьшить длитель ность сигнала при устойчивом приеме информации в регистр И числа, что в свою очередь, позволяет сократить цикл считывания, а значит, увеличить быстродействие запоминающего устройства без снижения его помехо по сравнению с извес ным устройством обладает более высоким быстродействием. Формула изобретения. . . Запомянеаащее устройство, содерж щее регистр адреса, регистр числа, 8

/ л ормирователь тока опроса, накопитель, сновные и дополнительные усилители читывания, причем выходы регистра дреса подключены ко входам форми ователя тока опроса, выходы которого соединены с адресными шинами накопителя, входы основных усилителей считывания подключены к основным разрядным шинам накопителя, а выходы - к информационным входам регистра числа, 9ХОДЫ дополнительных усилителей считывания соединены с дополнительными разрядными шинами накопителя, отличающееся тем что, с целью повышения быстродействия устройства, оно содержит регулируемые злементы задержки, входы которых подключены к выходам дополнительных усилителей считывания, а выходы - к стробирующим входам регистра числа. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 537387, кл. 6 П С 7/06, 1975. 2. Патент США № 3641519, кл. 340-174, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1100640A1 |

| Запоминающее устройство | 1982 |

|

SU1062787A1 |

| Запоминающее устройство | 1980 |

|

SU911614A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| Полупроводниковое запоминающее устройство с произвольной выборкой | 1984 |

|

SU1215135A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1316050A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1019495A1 |

| Запоминающее устройство | 1982 |

|

SU1049969A1 |

It

Фиг/

Uc

фш,2

Авторы

Даты

1981-12-23—Публикация

1980-05-08—Подача