1

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в устройствах формирования импульсных последователь-j ностей.

Известно устройство, обеспечивающее возможность фазировки счетчиков, содержащее два синхронных источника импульсов, входы которых объединены, |Q и блок фазировки, выполненный на счетном триггере, инверторе и двух логических элементах Недостатком его является высокое быстродействие..,

Известно также устройство фазиров;ки синхронных источников импульсов, содержащее генератор импульсов, выход которого соединен со входами деталей частоты, двухвходовые логичес- 20 кие элементы И и ИЛИ и счетчик, причем выходы деталей частоты соединены со входами элемента И, выход которого соединен со входом элемента ИЛИ, другой вход которого соединен с выходом 25 последнего разряда счетчика, счетный вход которого соединен с выходом одного из делителей частоты, вход сброса которого соединен с выходом последнего разряда счетчик а.30

При нормальной синхронной работе делителей частоты это устройство обеспечивает фазировку делителя частоты, имеющего меньший коэффициент деления от делителя частоты, имеющего больший коэффициент деления, а при расфазировке делителей частоты осуществляется фазирование делителя, имеющего меньший коэффициент деления с помощью дополнительного счетчика импульсов, сигнал с выхода которого выдается после поступления на счетчик определенного числа импульсов от делителя частоты, имевдцего меньпшй коэффициент деления t2 J,

Однако это устройство не применимо для фазировки синхронных делителей частоты с произвольно изменяющимися в процессе работы кратными между собой коэффициентами деления, так как требуемое число разрядов счетчика зависит от соотношения частот выходных сигналов делителей частоты, а в тех случаях, когда коэффициент деления делителя частоты, связанного со счетчиком, оказывается больше, чем коэффициент деления делителя не связанного со счетчиком,, время входа в синхронизм значительно возрастает. /

Целью изобретения является расширени-е функциональных возможностей за счет обеспечения возможности произвольного изменения коэффициентов деления синхронных источников импульсов.

Для достижения этой цели в устройство, содержащее делители частоты, рчетные входы которых объединены, и два двухвходовых логических элемента, введены два R-S-триггера, 5-входы которых соединены с выходами делителей Частоты, а выходы - со входами первого двухвходового логического элемента 3-к-триггер первый вход которого соединен с выходом первого двухходового логического элемента, счетный вход со счетными входами делителей частоты, третий вход и прямой выход триггера объединены, а счетный вход и инверсный выход соединены со входами второго двухвходового логического элемента, выход которого соединен со входами сброса делителей частоты и R-входами R-S-триггеров.

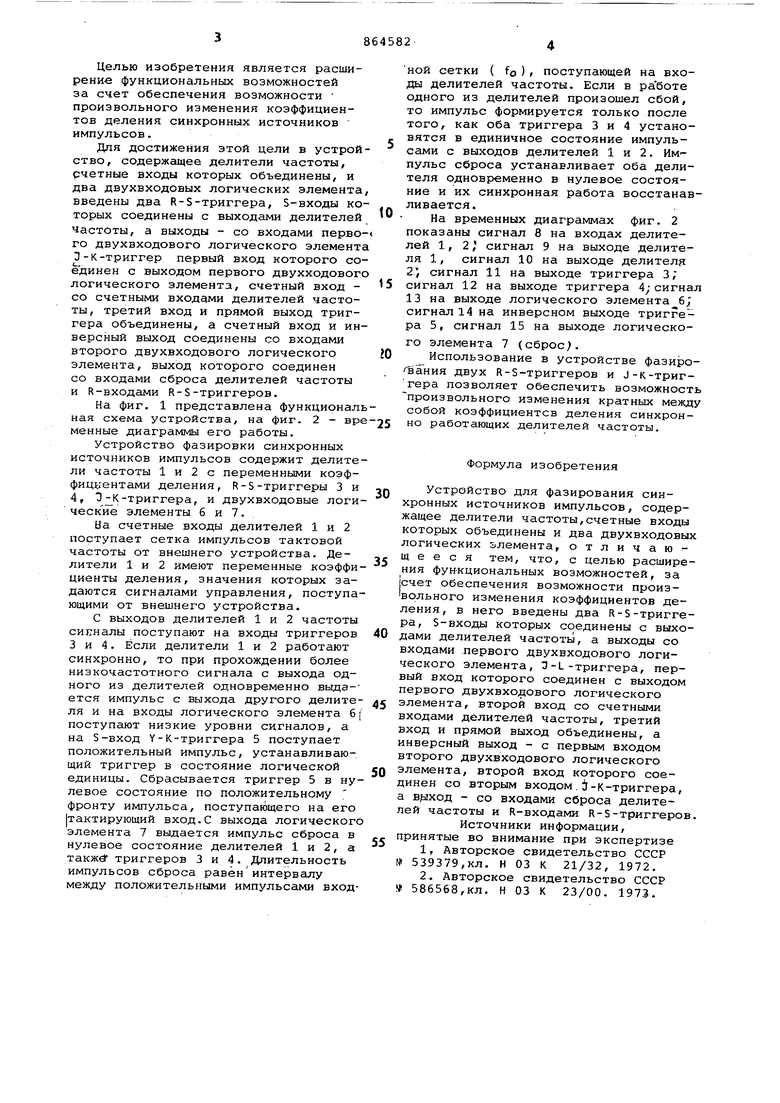

На фиг, 1 представлена функциональная схема устройства, на фиг, 2 - временные диаграммы его работы.

Устройство фазировки синхронных источников импульсов содержит делители частоты 1 и 2 с переменными коэффицуентами деления, R-S-триггеры 3 и 4, К-триггера, и двухвходовые логические элементы б и 7.

Ыа счетные входы делителей 1 и 2 поступает сетка импульсов тактовой частоты от внешнего устройства. Делители 1 и 2 имеют переменные коэффициенты деления, значения которых задаются сигналами управления, поступающими от внешнего устройства.

С выходов делителей 1 и 2 частоты сигналы поступают на входы триггеров 3 и 4, Если делители 1 и 2 работают синхронно, то при прохождении более низкочастотного сигнала с выхода одного из делителей одновременно вьщается импульс с выхода другого делителя и на входы логического элемента 6f поступают низкие уровни сигналов, а на S-вход У-К-триггера 5 поступает положительный импульс, устанавливающий триггер в состояние логической единицы. Сбрасывается триггер 5 в нулевое состояние по положительному фронту импульса, поступающего на его (тактирующий вход,С выхода логического элемента 7 выдается импульс сброса в нулевое состояние делителей 1 и 2, а такжй триггеров 3 и 4, Длительность импульсов сброса равен интервалу между положительными импульсами входной сетки ( fо)f поступающей на входы делителей частоты. Если в работе одного из делителей произошел сбой, то импульс формируется только после того, как оба триггера 3 и 4 установятся в единичное состояние импульсами с выходов делителей 1 и 2, Импульс сброса устанавливает оба делителя одновременно в нулевое состояние и их синхронная работа восстанавливается.

На временных диаграммах фиг, 2 показаны сигнал 8 на входах делителей 1, 2, сигнал 9 на выходе делителя 1, сигнал 10 на выходе делителя 2, сигнал 11 на выходе триггера З; сигнаш 12 на выходе триггера 4;сигна 13 на выходе логического элемента 6; сигнал 14 на инверсном выходе триггера 5, сигнал 15 на выходе логического элемента 7 (сбросу.

Использование в устройстве фазиро ания двух R-S-триггеров и J-к-триггера позволяет обеспечить возможност произвольного изменения кратных межд собой коэффициентов деления синхронно работающих делителей частоты.

Формула изобретения

Устройство для фазирования синхронных источников импульсов, содержащее делители частоты,счетные входы которых объединены и два двухвходовы логических элемента, отличающ е е с я тем, что, с целью расшире ния функциональных возможностей, за 1счет обеспечения возможности произвольного изменения коэффициентов деления, в него введены два R-S-триггера, S-входы которых соединены с выходами делителей частоть, а выходы со входами .первого двухвходового логического элемента, tJ-L-триггера, первый вход которого соединен с выходом первого двухвходового логического элемента, второй вход со счетными входами делителей частоты, третий вход и прямой выход объединены, а инверсный выход - с первым входом второго двухвходового логического элемента, второй вход которого соединен со вторым входом.i-к-триггера, а вмход - со входами сброса делителей частоты и R-входами R-S-триггеро

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР № 539379,кл. Н 03 К 21/32, 1972.

2.Авторское свидетельство СССР W 586568,кл, Н 03 К 23/00, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ 13 | 1991 |

|

RU2020743C1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Делитель частоты импульсов | 1979 |

|

SU845292A1 |

| Измерительный преобразователь активной и реактивной составляющих синусоидального тока | 1990 |

|

SU1748079A1 |

| Преобразователь кода во временной интервал | 1985 |

|

SU1300637A1 |

| Устройство для измерения скорости вращения вала | 1986 |

|

SU1315904A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Измерительный преобразователь составляющих основной гармоники переменного тока | 1989 |

|

SU1689862A2 |

| Устройство для измерения внутреннего угла синхронной машины | 1984 |

|

SU1226331A1 |

| Устройство для автоматической синхронизации генераторов переменного тока | 1984 |

|

SU1238189A1 |

j ллллллJ ллnлллллллллшlnлJгJuuшллJuulлллJlл

ff J -Jl-J -Jl-л JLJl JLJlJl JLJl л JlЛl Jl

ю-nnПfi n0

JT

Авторы

Даты

1981-09-15—Публикация

1979-09-26—Подача