(54) МУЛЬТИПЛЕКСНЫЙ КАНАЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал | 1980 |

|

SU868744A1 |

| Мультиплексный канал | 1980 |

|

SU924693A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1992 |

|

RU2032938C1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Мультиплексный канал | 1978 |

|

SU744540A2 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

, Изобретение относится к цифровой вычиспиплык технике, в частности к (фганизации структур мультиплексных каналов, и может быть 11спопьзова1ю для ввода-вывода информащга в фровых вычислительных (яетемах. Известны мультиплексные каналы, содержаодае регистр командного слова, регистр ащюса новото командного слова, модификатор. , регистр запросов, деишфратор адреса внешнего устройства, шифратор адреса командното сло ва, схему управления, шины передачи упршляющвх сигналов и информационные шины. ФувК ционирование такого канала происходит параллелшо с работой центрального процессора я заключается в приеме командных слов г управления обменом данных между внутренней памятью цифрсивой вычислительной машины (ЦВМ я большим количестаом внешних устройств, работающих одновременно. Командные слова, полученные из внутренней памяти-ЦВМ, принимаются в память устройства Мультшшекошй канал, которое содержит код операции, номер индикатора прерывания программы центрального процессора при окончашш обмена, счетчик количества обменов и указывает область памяти, используемую при обмене. При каждом однократном-обмене-происходит модификация количества обменов -и текущего адреса данных. Завершение операции ввода-вывода вызывает прерывание программы центрального процессора П1. Недостатком этих каналов является низкая пропускная способность. Наиболее близким к предлагаемому пи технической сущности является мультиплексный канал, содержащий блок для обработки команд центрального процессора, вход которого соединен с первым входом устройства, регистр связи с центральным процессором, первый вход которого соединен с выходом блока для обработки команд центрального процессора, второй вход - со вторым входом устройства, регистр разрешения запросов, дешифратор номера внешнего устройства, вход которого соединен с первым выходом pemcipe связи с центральньия процессором, а выход - со входом регистра разрешения запросов, регистр запросов, вход которого соединен с третьим ВХОДОМ устройства, шифратор адреса внешнего устройства, блок для анализа приоритетов, первый вход которого соединен со вторым выходом блока для обработки команд центрального процессора, второй вход - с выходом регистра запросов, третий вход - с выходом регистра разрешения запросов, а выход - со входом шифратора адреса внешнего устройства, коммутатор адресов обращения к памяти устройства, первьп вход которого соединен с выходом шифратора адреса внешнего устройства, второй вход - с первым выходом регистра связи с центральным процессором, а выход - с первым выходом устройства, модификатор, формирователь адресов размещения данных во внутренней памяти, регастр командного сло ва, первый вход которого соединен с четвертым входом устройства, первый выход через формирователь адресов размещения данных соединен со вторым выходом устройства, второй выход - с третьим выходом устройства и третьим входом коммутатора адреса обращения к памяти устройства, третий выход через модификатор соединен со вторым входом реги ра командного слова, четвертый выход последнего соединен с четвертым выходом устройства, коммутатор командных слов, первый вход которого соединен со вторым выходом регистра связи с центральным процессором, второй вход - с третьим выходом регистра командного слова, а выход - с пяты выходом устройства, селектор, регистр данных, пер вый вход которого соединен со вторым входом устройства, второй вход - с пятым входом устройства, а выход через селектор - с шестым и седьмым выходами устройства 2 Недостаток известного мультиплексного канала заключается в его невысокой пропускной способности, что обусловлено поочередап11М использованием входных и выходных информационных шин связи устройства с внутренней памятью ЦВМ, работающей в режиме расслоения обращений, с одной стороны, и внешними устройствами, с другой стороны, так как обслуживание запросов внешних устройств органи зовано последовательно и передача данных в каждый момент времени идет только в данном направлении. Цель изобретения - повышение пропускной способности мультиплексного канала. Поставленная цель достигается тем, что в мультиплексный канал, содержащий блок дешифрации команд центрального процессора, вход которого соединен с первым входом канала, регистр связи с центральным процессором, первый вход которого соединен с первым выходом блока дешифрации команд центрального процессора, вход - со вторым входом канала, регистр разрешения запросов. дешифратор номера внешнего устройства, вход которого соединен с первым выходом регистра связи с центральным процессором, а выход со входом регистра разрешения запросов, регистр запросов, вход которого соединен с третьим входом канала, блок приоритетов, первый вход которого соединен со вторым выходом блока дешифрации команд центрального процессора, второй вход - с выходом регистра запросов, третий вход - с выходом регистра разрешения запросов, а выход - со входом шифратора адреса внешнего устройства, коммутатор адресов обращения к памяга канала, первый вход которого соединен с вь(ходом шифратора адреса внешнего устройства, второй вход - с первым выходом регистра связи с центральным процессором, а выход - с первым выходом канала, первый регистр командного слова, первый вход которого соединен с четвертым входом канала, второй вход - с выходом блока модификации, первый выход через первый формирователь адресов размещения данных во внутренней памяти - со вторым выходом канала, второй выход - с третьим входом коммутатора адресов обращения к памяти канала и третьим выходом канала, коммутатор командных слов, первый вход которого соединен со вторым выходом регистра связи с центральным процессором, второй вход - с третьим выходом пер-, вого регистра командного слова, а выход с четвертым выходом канала, первый регистр данных, вход которого соедш ен со вторьпл входом канала, а выход - с пятым выходом канала, введены второй регистр командного слова, регистр направления передачи информации, второй регистр данных, коммутатор, второй формирователь адреса размещения данных во внутренней памяти и коммутатор номера индикатора прерьшашга программы центрального процессора, причем первый вход регистра направления передачи информации соединен с третьим выходом регистра связи с центральным процессором, второй вход - с выходом дешифратора номе} внешнего устройства, а выход - с четвертым входом блока приоритетов, первь1Й вход второго регистра командного слова соединен с четвертым входом канала, первый выход через второй форкшрователь а фесов размещения данных во внутренней памяти - с шесшм выходом канала, второй выход - с четвертым входом коммутатора адресов обращения к памяти канала и седьмым выходом канала, третий выход - с третьим входом коммутатора командных слов и. о первым входом коммутатора, второй вход которого соед|шеи с третьим выходом первого регистра командного слова, выход коммутатора соединен со входом блока модификации.

выход которого соединен со вторым входом второго регистра командного слова, первый и второй входы коммутатора номера индикатора прерывания программы центрального процессора соединены соответственно с четвертыми выходами первого и второго регистров командного слова, а выход - с восьмым выходом канала, вход и выход второго регистра данных соединены соответственно с пятым входом и девятым выходом канала.

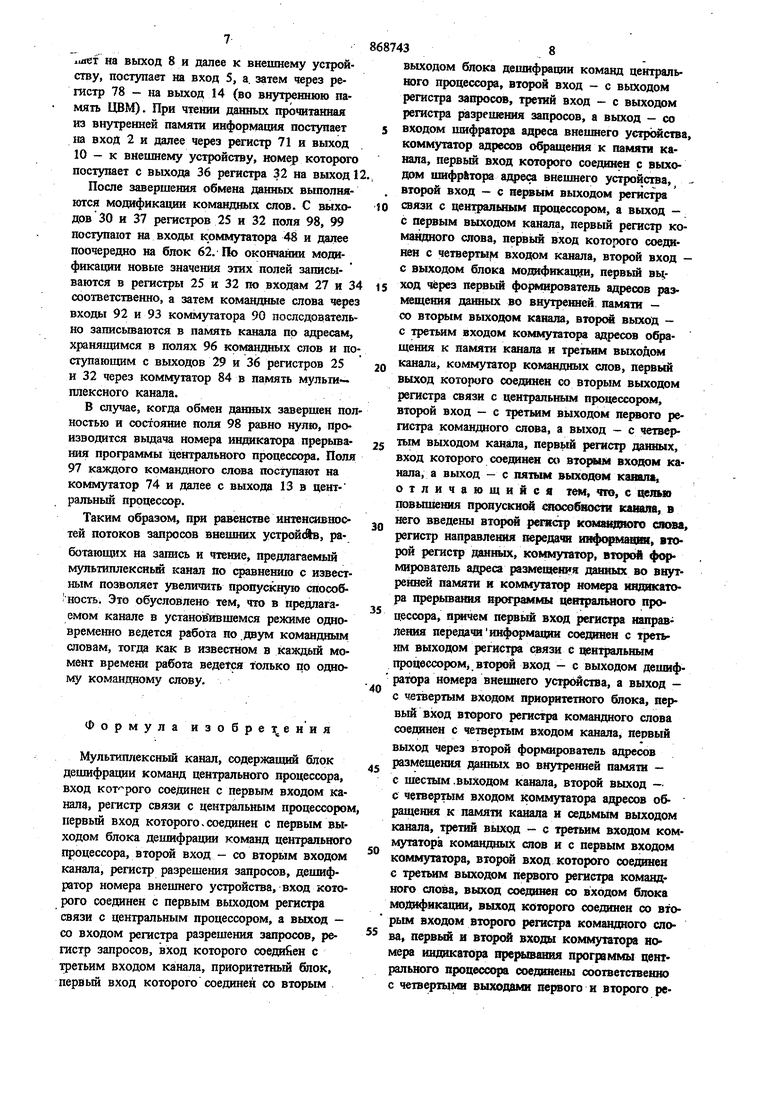

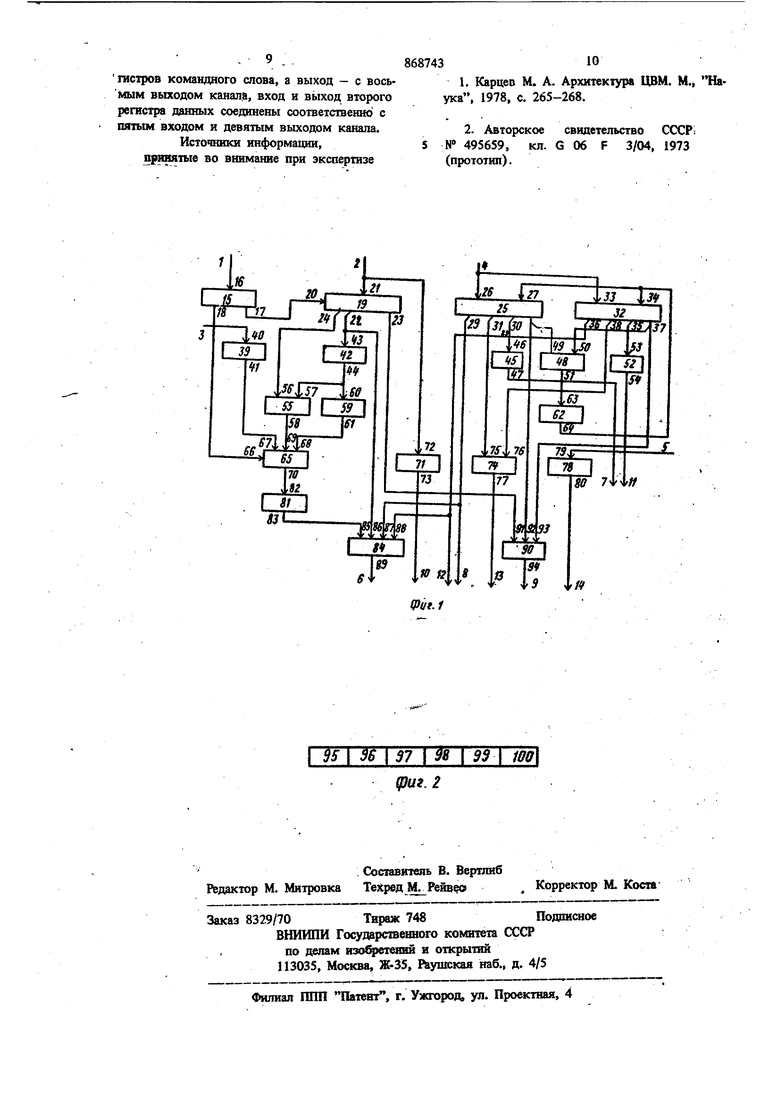

На фиг. 1 изображена блок-схема мультиплексного канала; на фиг. 2.- структура командного слова.

Мультиплексный канал содержит входы 1-5 канала, выходы 6-14 канала, блок 15 дешифрации команд центрального процессора со входом 16 и выходами 17 и 18, регистр 19 связи с центральным процессором со входами 20 и 21 и выходами 22, 23 и 24, первый регистр 25 командного слова со входами 26 и 77 и выходами 28-31, второй регистр 32 командного слова со входами 33 и 34 и выходами 35-38, регистр 39 запросов со входом 40 и выходом 41, деишфратор 42 номера внешнего устройства со входом 43 и выходом 44, первый формирователь 45 адреса размещения данных во внутренней памяти со входом 46 и выходом 47, коммутатор 48 со входами 49 и 50 и вььходом 51, второй формирователь 52 размещения данных во внутренней памяти со входом 53 и выходом 54, регистр 55 направления передачи информации со входами 56 и 57 и выходом 58, регистр 59 разрешения запросов со входом 60 и выходом 6 блок 62 модификации со входом 63 и выходом 64, блок 65 приоритетов со входами 66- 69 и выходом 70, первый регистр 71 да1шых со входом 72 и выходом 73, коммутатор 74 номера индикатора прерьйания программы центрального процессора со входами 75 и 76 и выходом 77, второй регистр 78 со входом 79 и выходом 80, ашфратор 81 адреса внешнего устройства со входом 82 и выходом 83, коммутатор 84 адресов обращения к памяти устройства со входами 85-88 и выходом 89, KOMAfytaTop 90 командных слов са входами 91, 91 и 93 н выходом 94.

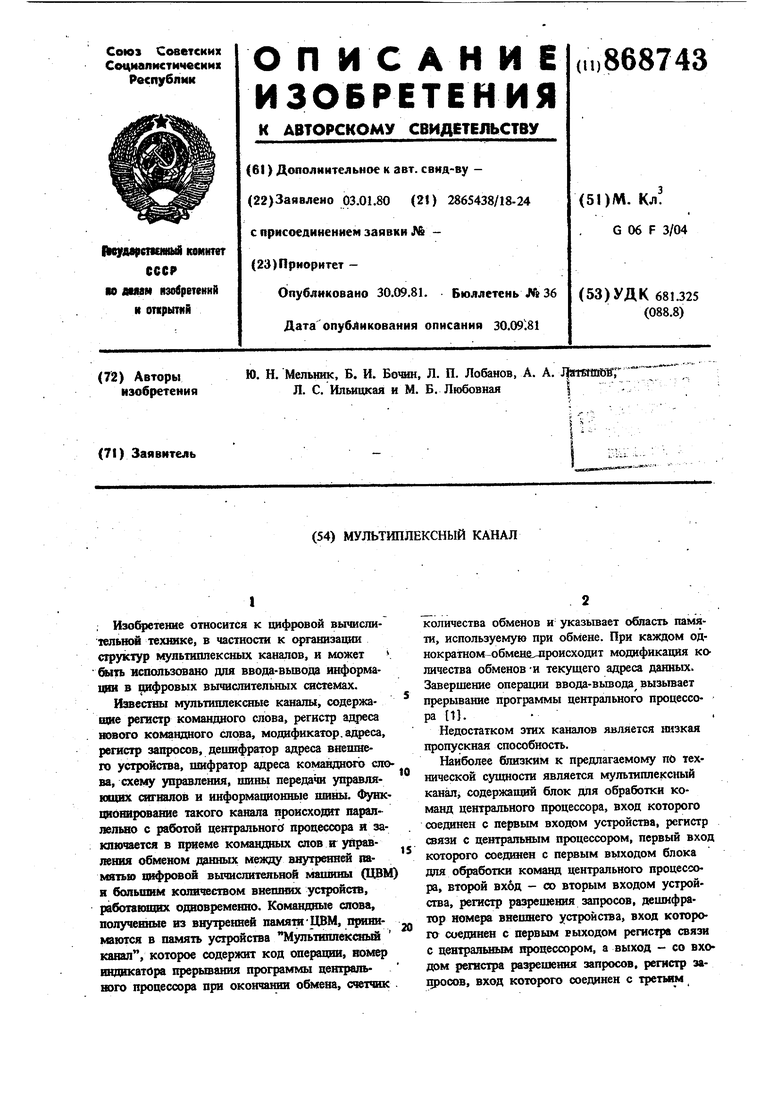

Структура командного слова включает поля направление 95 передата , номер 96 внешнего устройства, номер 97 шщщсатора прерьшания программы центрального процессора, счетчик 98 количества о&ленов, необходимых для завершения обмена, счетчик 99 адресов и начальный адрес 100 размещения данных во внутренней памяти ЦВМ.

Мультиплексный канал работает следующим образом.

Работа канала инициируется командой прием командного слова, поступающей из памяти

центрального процессора на вход блока 15, с выхода 17 которого в регистр 19 поступает сигнал приема командного слова, разрешая прием его из внутренней памяти через вход 2. 5 Запись командного слова в память канала осуществляется следующим образом. Номер внешнего устройства, одновременно являющийся адресом размещения командного слова в памяти, с выхода 22 регистра 19 поступает на вход 86 коммутатора 84 и далее в память с

10 выхода 6. Вслед за передачей адреса в память передается командное слово, которое с выходд 23 регистра 19 поступает на вход 91 коммутатора 90 и затем на выход 9. Во время запио командного слова работа блока 65 бло15кируется сигналами, поступающими с выхода 18 блока 15.

Наличие в памяти канала командного слова для некоторого внешнего устройства индицируется соответствующим разрядом регистра 59,

20 который возбуждается сигналами, поступающими на его входы с дешифратора 42. Направление передачи информации для некоторого внещнего устройства индивдруется соответствующим разрядом регистра 55, который возбуждается

25 сигналами, поступающими на его входы с вы-, хода 24 регистра 19 и сигналами с выхода де- шифратора 42.

Реализация запросов внешних устройств на обмен данных между каким-либо внешним уст30ройством и внутренней памятью ЦВМ осуществляется в следующей последовательности. .

Запросы внешних устройств на обмен данных поступают в регистр 39. При наличии сигнала разрешения запроса блок 65 пропускает старший

35 запрос на ввод (вывод) информации, который затем поступает на ишфратор 81. С выхода 83 последнего адрес размещения командного слова в памяти поступает на вход 85 коммутатора 84, с выхода которого - в память мультиплексно40го канала. По зтому адресу из памяти канала на регистр 25 (32) по входу 26 (33) читается командное слово , которое управляет вводом (выводом) данных. После этого блок 65 пропускает старший запрос на вывод (ввод) ин45формации. Командное слово, соответствующее зтому запросу, из памяти канала поступает на вход 4 и далее на регистр 25 (32).

Недобходимые для формирования адресов размещения данных во внутренней памяти по50ля 99 и 100 поступают на формирователи 45 и 52, с выходов которых адреса параллельно поступают в -различные блоки памяти ЦВМ: с выхода 7 - для ввода информации, а с выхода 11 - для вьшода информации.

55

Обмен происходит следующим образом. При записи данных во внутреннюю память 1ШМ информация от внешнего устройства, номер которого с выхода 29 регистра 25 посту«дет на выход 8 и далее к внешнему устройству, поступает на вход 5, а. затем через регистр 78 - на вь1ход 14 (во внутреннюю память ЦВМ). При чтении данных прочитанная из внутренней памяти информация поступает на вход 2 и далее через регистр 71 и выход 10 - к внешнему устройству, номер которого построгает с выхода 36 регистра 32 на выход 1 После завершения обмена данных выполняются модификации командных слов. С выходов30 и 37 регистров 25 и 32 поля 98, 99 поступают на входы коммутатора 48 и далее поочередно на блок 62. По окончании модификации новые значения этих полей записываются в регистры 25 и 32 по входам 27 и 3 соответственно, а затем командные слова через входы 92 и 93 коммутатора 90 последовательно записываются в память канала по адресам, хранящимся в полях 96 командных слов и по ступающим с выходов 29 и 36 регистров 25 и 32 через коммутатор 84 в память мулыи плексного канала. В , когда обмен данных завершен пол ностью и состояние поля 98 равно нулю, производится выдача номера индикатора прерывания программы Центрального процессора. Поля 97 каждого командного слова поступают на коммутатор 74 и далее с выхода 13 в центральный процессор. Таким образом, при равенстве интекйивностей потоков запросов внешних устройАв, работающих на запись и чтение, предлагаемый мультиплексньга канал по сравнению с известным позволяет увеличить пропускную оюсоб ность. Это обусловлено тем, что в предлагаемом канале в устаноШзшемся режиме одновременно ведется работа по .двум командным словам, тогда как в известном в каждый момент времени работа ведется только цо одному командному слову. Формулаизобрете ни я Мультиплексный канал, содержащий блок дешифрации команд центрального процессора, вход кот-рого соединен с первым входом канала, регистр связи с центральным процессоро первый вход которого. соединен с первым выходом блока дешифрации команд центрального процессора, второй вход - со вторым входом канала, регистр разрешения запросов, дешифратор номера внешнего устройства, вход которого соединен с первым выходом регистра связи с центральным процессором, а выход - со входом регистра разрешения запросов, регистр запросов, 18ход которого соединен с третьим входом канала, приоритетный блок, первый вход которого соединен со вторым 38 выходом блока дешифрации команд центрального процессора, второй вход - с выходом регистра запросов, третий вход - с выходом регастра разрешения запросов, а выход - со входом шифратора адреса внешнего уартпвл, коммутатор адресов обращения к памяти ка нала, первый вход которого соедашен с выходом amфpt opa арр&я внешнего устройства, второй вход - с первым выходом регистра связи с центральным процессором, а выход -. с первым выходом канала, первый регистр комайдного слова, первый вход которого соединен с четвертые входом канала, второй вход с выходом блока модификащд, первый вцход через первый формирователь адресов ра мещения данных во вн)ггренней памяти - со вторым выходом канала, второй выход с третьим входом коммутатора адресов обращения к памяти канала и третьим выходст канала, коммутатор командных слов, первый выход которого соединен со вторым выходом регистра связи с центральным процессором, второй вход - с треты1М выходом первого регистра командного слова, а выход - с четвертьпл выходом канала, первь1й регистр данных, вход которого соединен at вторым вхопом канала, а выход - с пятым выходом канал, отличающийся тем, чт, с ofjoaa повыц1ешш прояускж оюсобвости кашяа, в него введены решсгр комаидцого слова, регистр направлегам передата tm ofMaefa, еюрой регистр данных, коммутатор, формирователь адреса размещею я данных во внутренней памяти и коммутатор номера 1шдикатора {ферьгаания вр(нраммы цевтрального процессора, п1Я1чем первый вход регистра направления передачиинф мации соединен с треть}Ш1 выходом гистра связи с центральным процессором, второй вход - с выходом дешифратора номера внешнего ус1|Х)истаа, а выход - с четвертым входом приоритетного блока, первый вход второго регистра командного слова соединен с четвертым входом канала, первый выход через второй форкшрователь адресов размещения во внутренней памяти - с шестым .выходом канала, второй выход - с четвертым входом коммутатора ащ)есов обращения к памяти канала и седамь1м выходом канала, третий выход - с третьим входом коммутатора командных слов и с первым входом коммутатора, второй вход которого соединен с третьим выходом пертого регистра командного слова, выход соеданен со входом блока модафикации, выход которого соединен со вторым входом второго регистра командного слова, первый и второй входы коммутатора номера индикатора ареуывахтя программы центрального процессора соединены соответственно с четвертыми выходами пертого и второго регистров командного слова, а выход - с восьмым выходом канала, вход и выход второго рбтстр& данных соединены соответственно с пятым входом и девятым выходом канала. Источннкн ннформацин, пртяятые во внимание при экспертизе 6874310 1. Карцев М. А. Архитектура ЦВМ. М., Наука, 1978, с. 265-268. 2. Авторское свидетельство СССР: 5 N 495659, кл. G 06 F 3/04, 1973 (прототип).

I 9f 96 37 98 dS 1Щ (г. 2

Авторы

Даты

1981-09-30—Публикация

1980-01-03—Подача