1

Изобретение относится к цифровой., вычислительной технике и может быть f использовано для ввода-вывода инфсчэмзции в цифровых вычислительных системах.

Известны мультиплексные каналы, использующие стандартный интерфейс ввода-вывода, содержащий шины канала, шины абонента, цепи идентификации, цепи управления. По шине канала передаются коды команд канала, адреса внешних устройств (ВУ)и байты данных. По шине абонента передаются байты данных, адреса ВУ и информация о состоянии абонентов tl3.

Недостаток указанных устройств состоит в ограниченной области применения, так как последовательность действий, выполняемая через интерфейс, состоящая из последовательной начальной выборки ВУ, последовательности передачи данных и последовательности окончания, исключает возможность работы с ВУ, формирующими

запросы не в параллельном двоичном

коде.

Наиболее близким к предлагаемому является мультиплексный канал, содержащий блок обработки команд центрального процессора, выход которого соединен с первым входом устройства, регистр связи, первый вход которого соединен с первым выходом блока обработки команд центрального процес10сора, второй вход - с вторым входом устройства, два регистра хранения командных слов, первые входы которых соединены с третьим входом устройства, первые выходы - через последо15вательно соединенные коммутатор и модификатор командного слоёа с вторыми входами этих регистров, вторые выходы - через соответствующие формирователи адресу обращения к внут20ренней памяти соответственно с первым и вторым выходами устройства, третьи выходы - соответственно с третьим и четвертым выходами устройства, а

четвертые выходы - через коммутатор прерывания с пятым выходом устройства, коммутатор адресов обращения к памяти устройства, первый вход которого соединен с первым выходом регистра связи, второй и третий входы с третьими выходами регистров хранения командных слов, а выход и четвертый вход - соответственно с шестым выходом устройства и через шифратор адреса с выходом блока анализа приоритетов, коммутатор командных слов, первый вход которого соединен с первым выходом регистра связи а второй и третий вход - с первыми выходами регистров хранения командных слов, а выход - с седьмым выходом устройства, два регистра хранения данных, входы и выходы которых соединены с соответствующими входами и выходами устройства, регистр хранения запросов, вход которого соединен с пятым входом устройства, первый вход блока анализа приоритетов соединен с вторым выходом блока обработки команд центрального процессс а, второй вход - с выходом регистр хранения запросов, третий и четвертый - соответственно с выходами регистра разрешения запросов и регистра направления передачи 2 .

Недостаток известного канала состоит в ограниченной области примейения, так как устройство не может работать с внешними устройствами, запросы которых формируются в двоичном коде и передаются в канал по нескольким параллельным шинам.

Цель изобретения - расширение

области применения канала за счет обеспечения возможности дополнительного обслуживания внешних устройств, запросы которых поступают в двоичном коде.

«

Поставленная цель достигается тем

что в мультиплексный канал, содержащий регистр хранения запросов, блок обработки команд, вход которого соединен с первым входом канала, регистр связи с центральным процессором, первый вход которого соединен с первым выходом блока обработки команд, второй вход - с вторым входом канала, регистр хранения командных слов, первый вход которого соединен с третьим входом канала, первый выход и второй вход - соответственно с входом и выходом блока модификации командного слова, второй выход - через формиро,ватель адресов обращения к внутренней памяти соединен с первым выходом канала, третий выход - с вторым выходом канала, а четвертый выход с третьим выходом канала, коммутатор адресов обращения, первый вход которого соединен с первым выходом регисра связи с центральным профессором, второй вход - с четвертым выходом регистра хранения командного слова, .а выход - с четвертым выходом канала, коммутатор командных слов, первы вход которого соединен с вторым выходом регистра связи с центральным процессором, второй вход - с пятым выходом регистра хранения командного слова, а выход с пятым выходом канала, блок анализа приоритетов запросов, первый вход которого соединен с вторым выходом блока обработки команд, а второй вход - с выходом регистра хранения запросов, введены группа регистров хранения кодов запросов, коммутатор кодов запросов, дешифратор кодов запросов, коммутатор запросов, регистр хранения номер внешнего устройства и два блока анализа приоритетов кодов запросов, причем первый вход коммутатора запросов подключен к четвертому входу канала, а выход - к входу регистра хранения запросов. Входы регистров хранения запросов группы соединены с группой входов канала, вход первого блока анализа приоритетов кодов запросов соединен с вторым выходом блока обработки команд, группа входов - с выходами регистров хранения кодов запросов и группой входов коммутатора кодов запросов, выход которого соединен с входом дешифратора кодов запросов, выход которого соединен с вторым входом коммутатора запросов, первый вход второго блока анализа приоритетов кодов запросов соединен с выходом блока анализа приоритетов запросов, второй вход - с выходом первого блока анализа приоритетов кодов запросов, а выход через регистр хранения номера внешнего устройства соединен с третьим входом коммутатора адресов обращения .

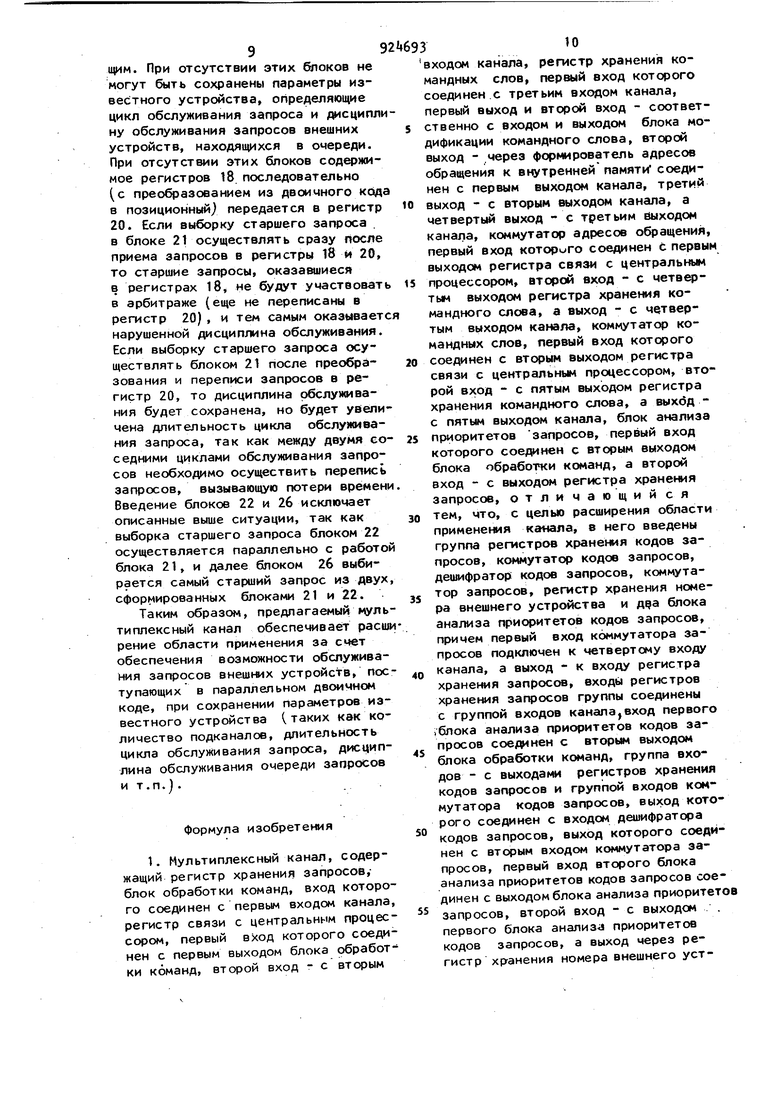

Каждый блок анализа приоритетов кодов запросов содержит k групп узлов сравнения, причем первый и второй входы i-го узла, сравнения J-ой группы .,, , , ,lt) соединены соответственно с выходами 2 -1-г6 и 2i-ro узлов сравнения j-l7n группы, первый и второй входы узлов сравнения первой группы подключены к группе входов блоков, выход узла сравнения К-и группы соединен с выходом блока.

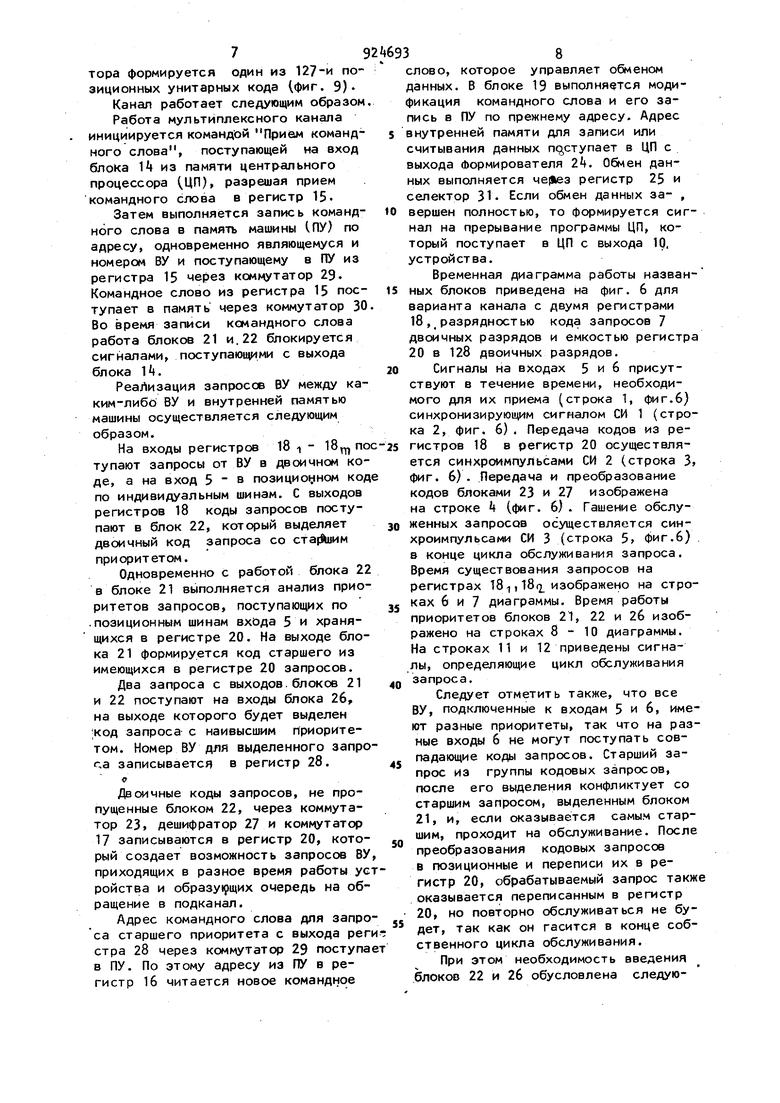

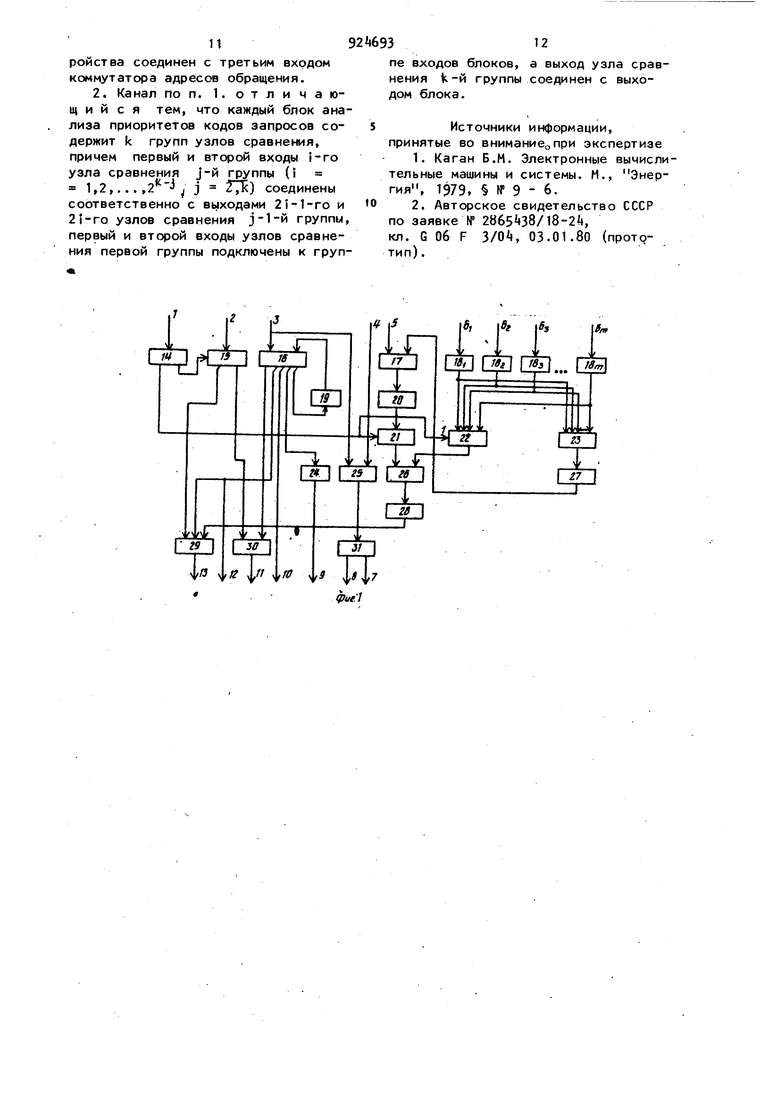

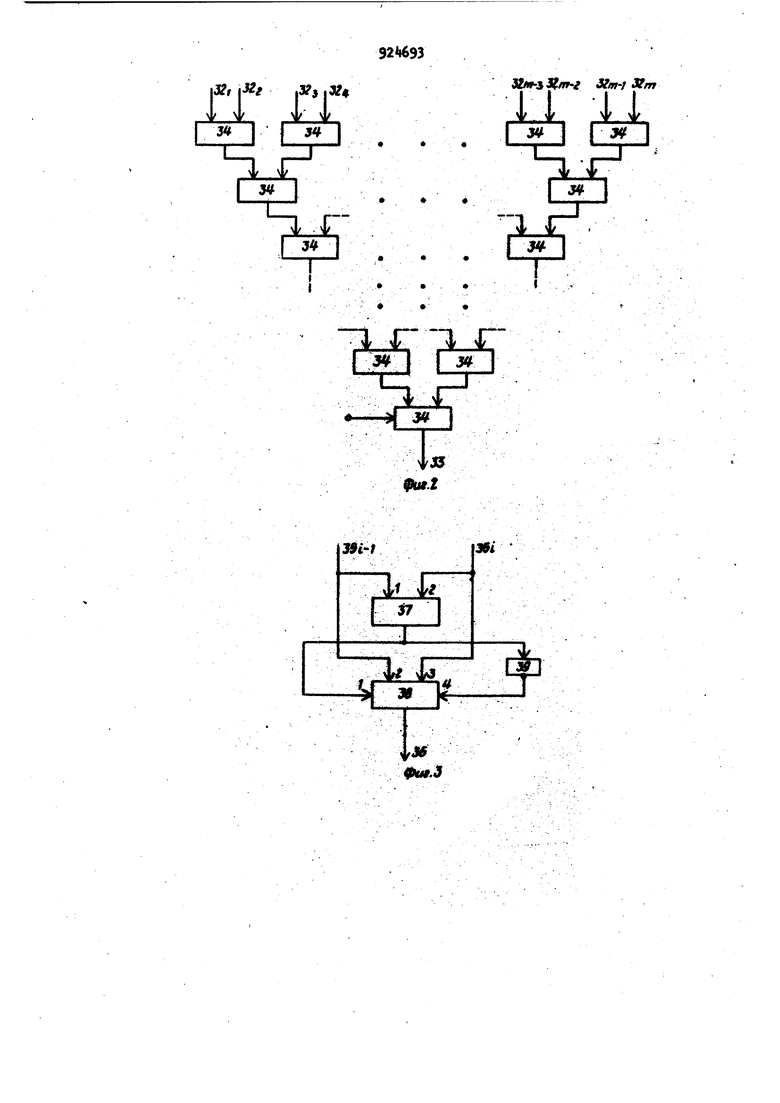

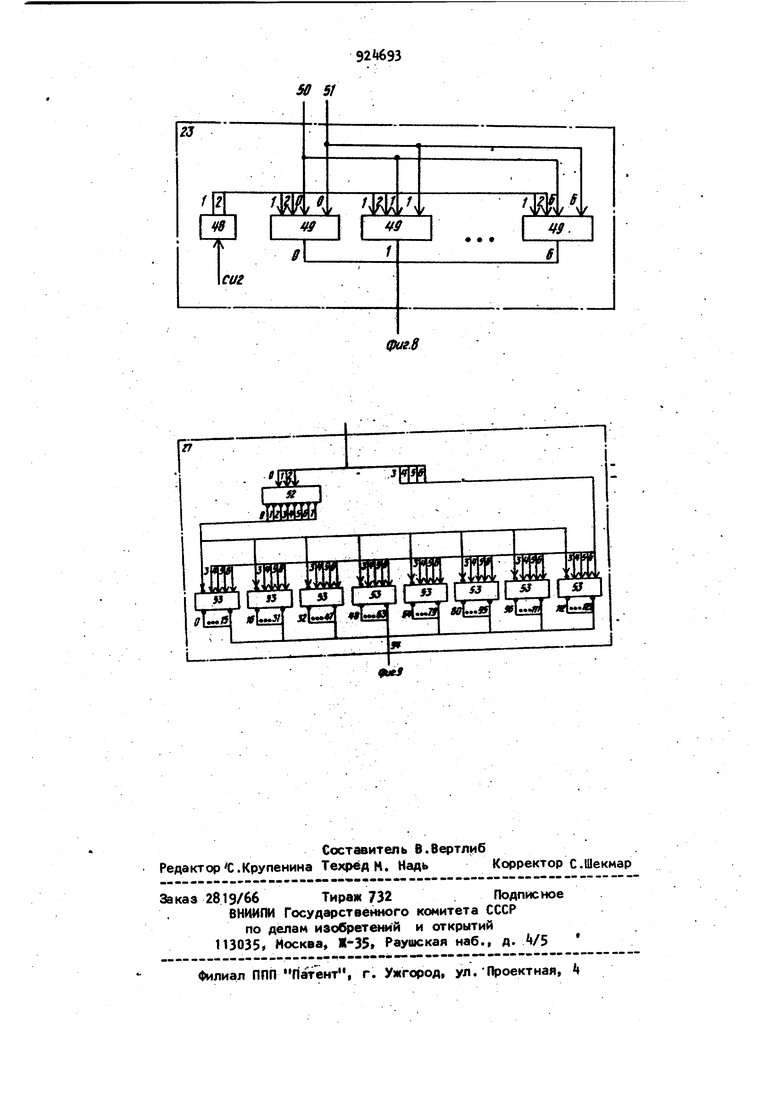

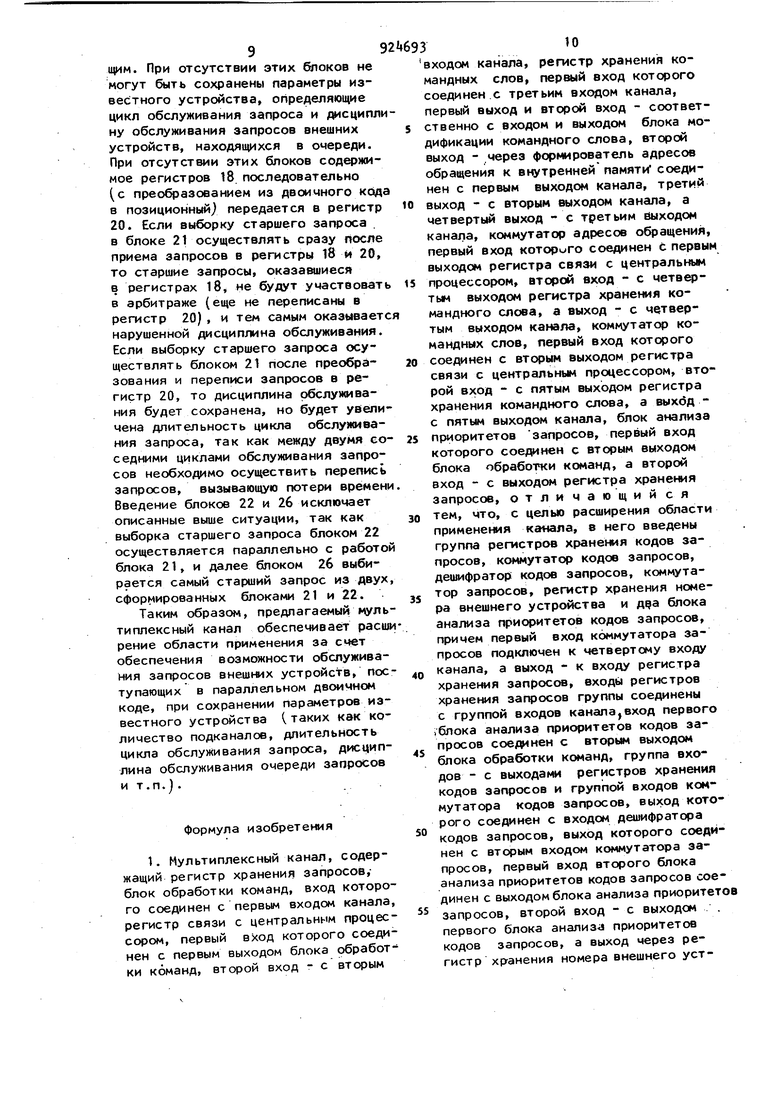

На фиг. 1 представлена блок-схема мультиплексного канала; на фиг.2 блок-схема блоков анализа приоритетов кодов запросов,- на фиг. 3 - схема узла сравнения блока анализа приоритетов кодов запросов-, на фиг. и 5 - функциональные схемы блоков обработки команд и модификации командного слова- на фиг. 6 - временная диаграмма работы канала , на фиг. 7 - 9 - функциональные схемы коммутатора запросов, коммутатора ко дов запросов и дешифратора кодов запросов. Мультиплексный канал содержит (фиг. 1 первый, второй, третий, четвертый и пятый входы 1 - 5 и группу входов 6 канала, шестой, седьмой, пе вый, второй, пятый, третий и четвертый выходы 7 - 13 канала, блок k обработки команд, регистр 15 связи с центральным процессором, регистр 16 хранения командного слова,, коммутатор 17 запросов, группа регистров 18 хранения кодов запросов, блок 19 модификации командного слова, регист 20 храненияГ запросов, блок 21 анализ приоритетов запросов, первый блок 22 анализа приоритетов кодов запро сов, коммутатор 23 кодов запросов, формирователь адресов -обращения к внутренней памяти, регистр 25 для хранения данных, второй блок 26 анализа приоритетов кодов запросов, дешифратор 27 кодов запросов, регистр 28 хранения номера внешнего устройс ва, коммутатор 29 адресов обращения к памяти устройства, коммутатор 30 командных слов, селектор 31. Блоки 22 и 26 анализа приоритетов кодов запросов предназначены дл выделения старшего по приоритету код из группы кодов запросов, поступивших на группу входов. Каждый из них содержит (фиг. 2) группу входов 32, выход 33 и узлы 3 сравнен1 я, осуществляющие сравнение пары кодов. Узлы З сравнения образуют пирамидальную структуру, состоящую из

k ступеней. Ступень с номером j включает в себя группу из 2 узлов 3 сравнения (j 1,1с) . Входы узлов З первой ступени (группы) соединены с соответствующими входами блока. Последняя ступень содержит ровно один узел З, выходом соединенный с выходом блока. В блоке 22 узел 3 последней ступени имеет также блокирующий третий вход, соединенный с входом блока 22, по которому поступает от блока Tt сигнал блокировки выдачи кода результата сравнения. Каждый узел 3 сравнения включает (фиг. 3) входы 35 выход 36, схему 37 сравнения, коммутатор 38 и элемент НЕ 39Блок 1 обработки команд предназначен для приема команд из центрального процессора, дешифрации поступивших команд, организации поступивших команд, организации приема командного слова в регистр 15 связи с центральным процессором и организации блокировки работы блоков 21 и 22. Блок I состоит из регистра 40 команды центрального процессора и дешиф эатора k ( фиг. 4) . Блок 19 модификации командного слова предназначен для формирования очередного адреса данных и уменьшения содержимого поля счетчика количества обенов. Блок 19 состоит из счетчика 2 адреса данных и счетчика k3 колич ства обменов (фиг. 5)Формирователь адресов обращения к внутренней памяти представляет собой группу усилителей мощности,, например группу микросхем К 155 ЛА 6, имеющих повышенную нагрузочную спообность. Коммутатор 17 запросов может быть выполнен на элементах И-НЕ tk и элементах НЕ со стробированием сигналов на входе серией СИ 1, а на входе k7 серией СИ 2 (фиг. 7). Коммутатор 23 кодов запросов содержит, например, двухразрядный счетчик fS синхроимпульсов СИ 2, его выходные состояния 01 и 10 управляют передачей запросов через элементы коммутации с входов 50 и 51 (фиг. 8). Дешифратор 27 кодов запросов выполняется на стандартных трехвходовом элементе 52 дешифрации и четырехвходовых элементах 53 дешифрации. На-выходных шинах 5 дешифратора формируется один из позиционных унитарных кода (фиг. 9). Канал работает следующим образом Работа мультиплексного канала инициируется команд&й Прием командного слова, поступающей на вход блока Т из памяти центрального процессора (ЦП), разрешая прием командного слова в регистр 15. Затем выполняется запись командного слова в память машины (ПУ) по адресу, одновременно являющемуся и номером ВУ и поступающему в ПУ из регистра 15 через коммутатор 29. Командное слово из регистра 15 поступает в память через коммутатор 30 Во время записи командного слова работа блоков 21 и.22 блокируется сигналами, поступающими с выхода блока 1А. Реализация запросов ВУ между каким-либо ВУ и внутренней памятью машины осуществляется следующим образом. На входы регистров 18 -i - 18 no тупают запросы от ВУ в двоичном коде, а на вход 5 - в позициоуном код по индивидуальным шинам. С выходов регистров 18 коды запросов поступают в блок 22, который выделяет двоичный код запроса со cTafftuHM приоритетом. Одновременно с работой блока 22 в блоке 21 выполняется анализ приоритетов запросов, поступающих по .позиционным шинам входа 5 и хранящихся в регистре 20. На выходе блока 21 формируется код старшего из имеющихся в регистре 20 запросов. Два запроса с выходов.блоков 21 и 22 поступают на входы блока 26, на выходе которого будет выделен ;код запроса с наивысшим приоритетом. Номер ВУ для выделенного запро са записывается в регистр 28. Двоичные коды запросов, не пропущенные блоком 22, через коммутатор 23, дешифратор 27 и коммутатор 17 записываются в регистр 20, который создает возможность запросов ВУ приходящих в разное время работы ус ройства и образующих очередь на обращение в подканал. Адрес командного слова для запро са старшего приоритета с выхода рег стра 28 через коммутатор 29 поступа в ПУ. По этому адресу из ПУ в регистр 16 читается новое командное СЛОВО, которое управляет обменом данных. В блоке 19 выполняется модификация командного слова и его запись в ПУ по прежнему адресу. Адрес внутренней памяти для записи или считывания данных поступает в ЦП с выхода Формирователя 2k, Обмен данных выполняется регистр 25 и селектор 31. Если обмен данных за- , вершен полностью, то формируется сигнал на прерывание программы ЦП, который поступает в ЦП с выхода 10. устройства. Временная диаграмма работы названных блоков приведена на фиг. 6 для варианта канала с двумя регистрами 18,разрядностью кода запросов 7 двоичных разрядов и емкостью регистра 20 в 128 двоичных разрядов. Сигналы на входах 5 и 6 присутствуют в течение времени, необходимого для их приема (строка 1, фиг.6) синхронизирующим сигналом СИ 1 (строка 2, фиг. 6). Передача кодов из регистров 18 в регистр 20 осуществляется синхроимпульсами СИ 2 (строка 3 фиг. 6). Передача и преобразование кодов блоками 23 и 27 изображена на строке (фиг. 6). Гашение обслуженных запросов осуществляется синхроимпульсами СИ 3 (строка 5 фиг.6) в конце цикла обслуживания запроса. Время существования запросов на регистрах 18 , 18(2 изображено на строках 6 и 7 диаграммы. Время работы приоритетов блоков 21, 22 и 2б изображено на строках 8-10 диаграммы. На строках 11 и 12 приведены сигналы, определяющие цикл обслуживания запроса. Следует отметить также, что все ВУ, подключенные к входам 5 и 6, имеют разные приоритеты, так что на разные входы 6 не могут поступать совпадающие коды запросов. Старший запрос из группы кодовых запросов, после его выделения конфликтует со старшим запросом, выделенным блоком 21, и, если оказывается самым старшим, проходит на обслуживание. После преобразования кодовых запросов в позиционные и переписи их в регистр 20, обрабатываемый запрос также оказывается переписанным в регистр 20, но повторно обслуживаться не будет, так как он гасится в конце собственного цикла обслуживания. При этом необходимость введения блоков 22 и 26 обусловлена следующим. При отсутствии этих блоков не могут быть сохранены параметры известного устройства, определяющие цикл обслуживания запроса и да1сципл ну обслуживания запросов внешних устройств, находящихся в очереди. При отсутствии этих блоков содержимое регистров 18 последовательно (с преобразованием из двоичного код в позиционный передается в регистр 20. Если выборку старшего запроса в блоке 21 осуществлять сразу после приема запросов в регистры 18 и 20, то старшие запросы, оказавшиеся в регистрах 18, не будут участвоват в арбитраже (еще не переписаны в регистр 20), и тем самым оказывает нарушенной дисциплина обслуживания. Если выборку старшего запроса осуществлять блоком 21 после преобразования и переписи запросов в регистр 20, то дисциплина обслуживания будет сохранена, но будет увепи чена длительность цикла обслуживания запроса, так как между двумя со седними циклами обслу)Ю1вания запросов необходимо осуществить перепись запросов, вызывающую потери времен Введение блоков 22 и 26 исключает описанные выше ситуации, так как выборка старшего запроса блоком 22 осуществляется параллельно с работо блока 21, и далее блоком 26 выбирается самый старший запрос из двух сформированных блоками 21 и 22. Таким образом, предлагаемый муль типлексный канал обеспечивает расши рение области применения за смет обеспечения возможности обслуживания запросов внешшх устройств, Пос тупагощих в параллельном двоичном коде, при сохранении параметров известного устройства (.таких как количество подканалов, длительность цикла обслуживания запроса, дисциплина обслуживания очереди запросов и т.п.). формула изобретения 1. Мультиплексный канал, содержащий регистр хранения запросов,блок обработки команд, вход которого соединен с первым входом канала, регистр связи с центральным процессором, первый вход которого соединен с первым выходом блока обработ ки команд, второй вход - с вторым ВХОДОМ канала, регистр хранени1Ч командных слов, первый вход которого соединен с третьим входом канала, первый выход и второй вход - соответственно с входом и выходом блока модификации командного слова, второй выход - .через формирователь адресов обращения к внутренней памяти соединен с первым выходом канала, третий выход - с вторым выходом канала, а четвертый выход - с третьим выходом канала, коммутатор адресов обращения, первый вход коториго соединен с первым выходом регистра связи с центральным процессорюм, второй вход - с четвертым выходом регистра хранения командного слова, а выход - с четвертым выходом канала, коммутатор командных слов, первый вход которого соединен с вторым выходом регистра связи с центральным процессором, второй вход - с пятым выходом регистра хранения командного слова, а выхбд с пятым выходом канала, блок анализа приоритетов запросов, первый вход которого с вторым выходом блока обработки команд, а второй вход - с выходом регистра хране1 1Я запросов, отличающийся тем, что, с целью расширения области применения канала, в него введены группа регистров хранения кодов запросов, коммутатор кодов запросов, дешифратор кодов запросов, коммутатор запросов, регистр хранения номера внешнего устройства и блока анализа приоритетов кодов запросов, причем первый вход коммутатора запросов подключен к четвертому входу канала, а выход - к входу регистра хранения зап(осов, входы регистров хранения запросов группы соединены с группой входов канала,вход первого блока анализа приоритетов кодов запросов coejc HeH с вторьм выходом блока обработки команд, группа входов - с выходами регистров хранения кодов запросов и группой входов коммутатора кодов запросов, выход которого соединен с входом дешифратора кодов запросов, выход которого соединен с вторым входом коммутатора запросов, первый вход второго блока анализа приоритетов кодов запросов соединен с выходом блока анализа приоритетов запросов, второй вход - с выходом первого блока анализа приоритетов кодов запросов, а выход через регистр хранения номера внешнего устроиства соединен с третьим входом коммутатора адресов обращения.

2. Канал по п. 1. отличающийся тем, что каждый блок анализа приоритетов кодов запросов содержит k групп узлов сравнения, причем первый и второй входы i-ro узла сравнения j-й группы (i ,2,... , j 27R) соединены соответственно с выходами 2i-1-ro и узлов сравнения j-1-й группы, первый и второй входы узлов сравнения первой группы подключены к группе входов блоков, а выход узла сравнения -и группы соединен с выходом блока.

Источники информации, принятые во вниманиеопри экспертизе

1.Каган Б.М. Электронные вычислительные машины и системы. М., Энер. 1979, § № 9 - 6.

гия.

2.Авторское свидетельство СССР по заявке № 28б5 38/18-2{,

кл. G Об F З/О, 03.01.80 (npOTQтип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал | 1980 |

|

SU868744A1 |

| Мультиплексный канал | 1980 |

|

SU868743A1 |

| Байт-мультиплексный канал | 1981 |

|

SU972496A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Мультиплексный канал | 1980 |

|

SU938277A2 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

ГГ ffr

LEJ i: %

сю

S Г

Lp

-CHJ

Jft-r

31лг-зЗ(аг-г Хт-1 Хт fФ Ф

m 71 г-

L.

jfr Ф 4

IS ш

; 4

I

г л

9kir.2

j$i

лИ i

E5

i sU

П

vJff DM.

(риг.Ч

(риг.В

Авторы

Даты

1982-04-30—Публикация

1980-05-08—Подача