1

Изобретение относится к вычислительной технике, точнее к устройст- у вам контроля цифровых вычислительных машин.

В любой современной цифровой вычислительной машине имеется возможность произвести останов по заранее заданному адресу. Режим останова по адресу реализуется путем сравнения текущего адреса выполняемой программы с заранее заданным на пульте управления 1.

Существенным недостатком данного режима является то, что им сложно а иногда и невозможно пользоваться при работе с цилиндрическими или разветвленными программами и с программами по обработке прерываний вычислительного процесса.

Наиболее близким к предлагаемому является устройство останова ЭВМ родержащее схему формирования выходного сигнала, схему сравнения, схему задания кода, счетчик, схему ИЛИ, схемы задания кода согласования и схемы сравнения, первые входы которых соединены с выходами соответствующих схем задания, кода, вторые - с выходами схем согласования, а выходы схем сравнения - с -соответствующими

(входами схемы ИЛИ, выход которой Соединен со счетным входом счетчика выход счетчика соединен с первым входом схемы сравнения, второй вход :которой соединен со схемой задания кода, а выход - со входом схемы формирования выходного сигнала, расширены возможности применения его для циклических и разветвленных задач и программ с повторяющимися адресами|2}.

Однако при работе с устройством необходимо точно высчитывать число повторений заданного адреса или другого задания кода, встречающиеся в программе до момента, когда необходимо произвести останов цифровой вычислительной машины, что является задачей трудоемкой/ а часто и нераз решимой для циклических программ, программ с повторяющимися адресами и программ по обработке прерываний вычислительного процесса.

Цель изобретения - расширение функциональных возможностей устройства за счет реализаций останова цифровой вычислительной мгииины по ,заданному адресу при работе с циклическими программами, программами с повторяющимися адресами и с програм;,мами по обработке прерываний вычислительного процесса.

Поставленная цель достигается тем что в устройство останова цифровой вычислительной машины содер)) первый, второй и третий блоки задания кода, блок согласования нагрузки, первый, второй и третий блоки сравнения,блок временного согласования, элемент ИЛИ, счетчик, блок формирования выходного сигнала, причем выходы первого и второго блоков задания кода соединены соответственно с первыми входами первого и второго блоков сравнения, вторые входы которых соединены соответственно с выходом блока согласования нагрузки и блока временного согласования, вход блока согласования является адресным входом устройства, вход блока временного согласования является сигнальным входом устройства, выходы первого и второго блоков сравнения соединены соответственно с первыгд и вторым входами элемента ИЛИ, выход которого соединен с первым входом счетчика, выход счетчика соединен с первым входом третьего блока сравнения, второй вход которого соединен с выходом третьего блока задания кода, выход третьего блока сравнения соединен со входом блока, формирования выходного сигнала выход которого является выходом устройства, введены четвертый и пятый блоки задания кода, четвертый и пятый блоки сравнения и триггер, причем выходы четвертого и пятого блоков задания кода соединены соответственно с первыми входами четвертого и пятого блоков сравнения, вторые входы которых соединены с выходом блока электрического согласования нагрузки, выход четвертого блока сравнения соединен с единичным входом триггера, выход пятого блока сравнения соединен с нулевым входом триггера, выход которого соединен со вторым входом счетчика.

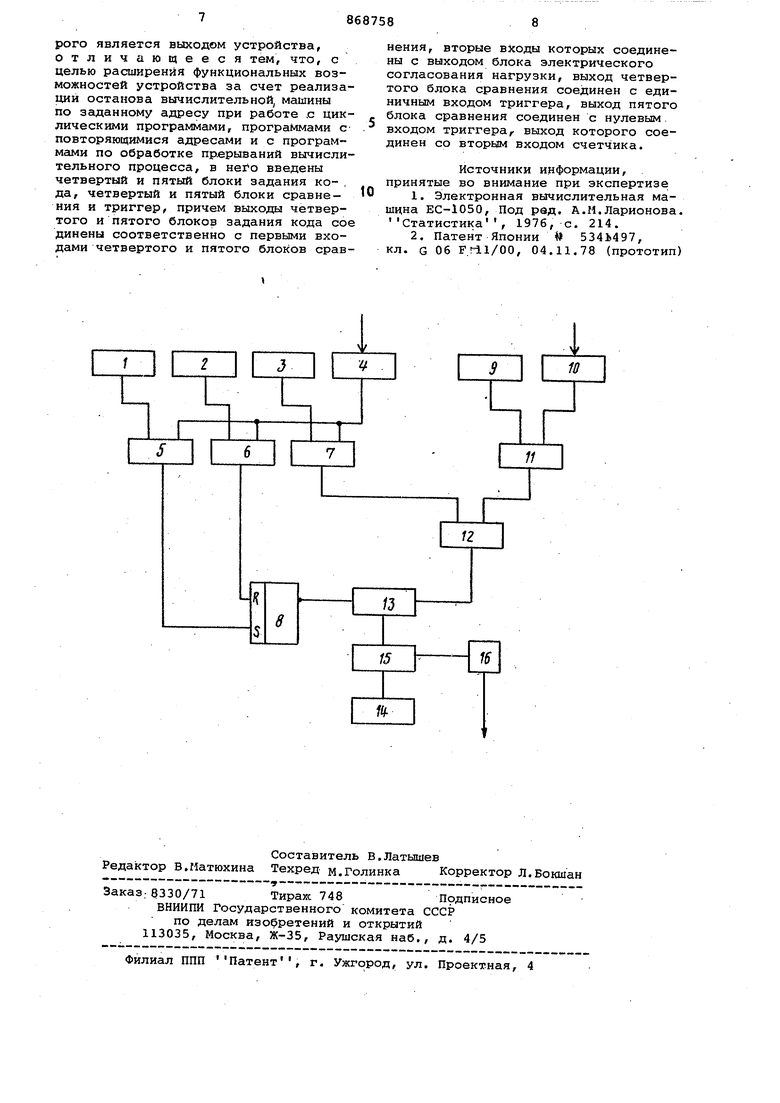

На чертеже представлена блок-схем устройства останова цифровой вычислительной машины (ЦВМ).

Устройство дляуправления остановом цифровой вычислительной машины содержит четвертый 1 и пятый 2, и первый 3 блоки задания кода, блок 4 электрического согласования нагрузки, етвертый 5, пятый б и перрый 7 блоки сравнения, триггер 8, второй бло 9 задания кода, бл6к10 времен1ного согласования, второй бйок 11 сравнения, элемент ИЛИ 12, счетчик 13, третий, блок 14 задания кода, третий блок 15 сравнения и блок 16 формирования выходного сигнала. Блоки 1,2,3,9 и 14 задания кода представляют собой набор переключателей с элементами согласования на интегральных микросхемах. Блоки 5,6,7,11

и 15 сравнения представляют собой многоразряд 1ые схемы сравнения на интегральных микросхемах.

Блок 4 согласования нагрузки служит для согласования нагрузочной способности и уровней выходов цифровой вычислительной машины со входом блоков 5-7 сравнения. Он представляе собой набор интегральных микросхем содержащих инверторы с малым входным током и нагрузочной способностью, достаточной для подключения к ним входов блоков 5-7 сравнения.

Блок 10 временного согласования кроме согласования,по нагрузочной способности, служит для временного согласования сигналов, поступающих на его вход и представляет собой набор триггеров. На блок 10 согласования могут подаваться произвольные сигналы, которые имеют различную временную привязку внутри такта работы ЦВМ, эти сигналы запоминаются триггерами. В конце такта информация с триггера сравнивается с информацией из блока 9 задания кода, посл чего триггеры обнуляются.

Устройство работает следующим образом.

В четвертом блоке 1 задания кода задается начальный адрес А нет/ в пятом блоке 2 задания кода - конечный адрес участка программы, на котором необходимо остановить работу ЦВМ. На вход блока 4 согласования нагрузки поступает значение текущего адреса программы. При сравнении-Ау,дц с текущим адресом на выходе четвертого блока 5 сравнения появляется сигнал сравнения, который воздействует на первый вход триггера 8, и триггер переходит в состояние,что обеспечивает снятие со счетчика 13 сигнала обнуления. При сравнении Ац с текущимадресом появляется сигнал на выходе пятого блока б сравнения который во.здействует на второй вход триггера 8 и триггер переходит в О состояние, при этом.нулевой выход триггера 8 обнуляет счетчик 13. Таким образом работа, счетчика 13 разрешена только в диапазоне текущих адресов программы от до . Если внутри указанного диапазона произойдет сравнение текущего адреса из блока 4 согласования нагрузки с адресом останова, который задается первым блоком 3 задания кода, на выходе первого блока 7 сравнения появляется сигнал, который через элемент ИЛИ 12 воздействует на счетный вход счетчика 13, состояние которого увеличивается на 1 . Если в заданном интервале адреса .произойдет сравнение комбинации входных сиг.налов из блока 10 временного согласования с кодом из блока 9 задания код на выходе второго блока 11 сравнения появляется сигнал, который также

воздействует на счетный вход счетчика 13 через элемент ИЛИ 12. Состояние счетчика 13 увеличивается после прихода каждого сигнала от элемента ИЛИ 12. В третьем блоке 14 задания

.кода задается код, который соответствует требуемому числу сравнений всех входных сигналов с заданным в течение интервала от Ацач ло А Qц Если содержимое счетчика 13 стает равно коду, заданному в третьем блоке 14 задания кода, то на выходе третьего блока 15 сравнения появляется сигнал, который преобразовывается блоком 11 формирования выходного сигнала в сигнал останова ЦВМ. Если счетчик 13 не достигает до заданного третьим блоком 14 задания кодом числа и происходит сравнение в пятом блоке 6 сравнения текущего адреса с Ацон г триггер 8 переходит в О состояние и тем самым обнуляет счетчик 13.

Работа устройства с циклическими и разветвленными программами, програмами с повторяющимися адресами и с программами по обработке прерываний вычислительного процесса определчется соответствующим выбором начального Ацдц и конечного адресов. Например при работе с циклическими

.программами необходимо остановить . ЦВМ на таком цикле, в котором некоторый адрес А встречается К-ый раз (например, А - адрес из подпрограммы исправления ошибок). В этом случа в качестве A,|-,ц выбирается адрес конца цикла (набираются в блоках 1 и 2 соответственно). В первом блоке 3 задания кода набирается адрес А, в третьем блоке 14 задания кода число К.

В случае работы с разветвленными программами в зависимости от условий задачи пpoгpaм.a можей пойти по любой ветке. В качестве Aц и ) выбирается адрес начала и конца той ветки програь1мы, в пределах которой необходимо остановить ЦВМ. Если .программа не идет по выбранной ветке то останов ЦВМ не формируется.

При работе с программами, в которых один и тот же адрес А повторяется многократно, и например, адреса микрокоманд, а нам необходимо остановить ЦВМ в определенном месте программы, где встречается эгот адрес,в качестве , выбирается такой адрес, который встречается наиболее близко к требуемому месту останова ЦВМ. А в этом случае можно не задавать. Число повторений адреса А считается от адреса А. Таким образом, отпадает необходимость считать число повторений адреса А по всей программе что является трудоемкой, а часто неразрешимой задачей.

При работе с программами, в которых может происходить прерывание вычислительного процесса, как правило, неизвестно в какой момент придет требование на прерывание. В этом случае, если необходимо остановить ЦВМ, когда на участке от А„д до А произойдет К-прерываний, в четвертом блоке 1 задания кода набирается в пятом блоке 2 задания кода А

нац

,выбранного участка. В первом блоке 3 задания кода набирается адрес из подпрограммы обработки прерываoний, на котором необходимо остановить ЦВМ, в третьем блоке 14 задания кода набирается число К.

Введение в устройство останова цифровой, вычислительной машины новых

5 блоков задания кода, двух блоков сравнения и триггера позволяет значительно сузить зону адресов программы, на которой осуществляется контроль условий останова. В результате

0 значительно упрощается процесс работы с устройством, так как отпадает необходимость анализировать всю программу на предмет повторения условий, по которым задан останов, За счет соответствующего выбора-АНЯЧ и АХ.ОИ

5 устройство останова; цифровой вычислительной машины может эффективно использоваться при работе с циклическими и разветвленными программами, программами с повторяющимися адресами и программами по обработке прерываний вычислительного процесса.

Формула изобретения

Устройство для управления остановом цифровой вычислительной машины, содержащее первый, второй и третий блоки задания кода, блок электрического согласования нагрузки первый, второй и третий блоки сравнения, блок временного согласования, элемент ИЛИ, счетчик, блок формирования импульсов, причем выходы первого и второго блоков задания кода соединены соответственно с первыми входами первого и второго блоков сравнения, вторые входы которых соединены соответственно с выходом . блока электрического согласования нагрузки и блока временного согласования, вход блока электрического согласования нагрузки является адpecHbiM входом устройства, вход блока временного согласования является сигнальным входом устройства, выxo первого и второго блоков сравнения соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с первым входом счетчика, выход счетчика соединен с первым входом третьего -бло- ка сравнения, второй вход которого соединен с выходом третьег о блока задания кода, выход третьего блока сравнения срединен со входом блока формирования импульсов, выход которого является выходом устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет реализаций останова вычислительной, машины по заданному адресу при работе с циклическими программами, программами сповторяющимися адресами и с программами по обработке прерываний вычислительного процесса, в неГо введены четвертый и пятый блоки задания ко- . да, четвертый и пятый блоки сравнения и триггер, причем выходы четвертого и пятого блоков задания кода сое динены соответственно с первыми входами четвертого и пятого блоков сравнения, вторые входы которых соединены с выходом блока электрического согласования нагрузки, выход четвертого блока сравнения соединен с единичным входом триггера, выход пятого блока сравнения соединен с нулевым. входом триггера,- выход которого соединен со вторым входом счетчика.

Источники информации, принятые во внимание при экспертизе

1.Электронная вычислительная машина ЕС-1050, Под ред. А.М.Ларионова Статистика, 1976, с. 214.

2.Патент Японии ,

кл. G Об F.MLl/OO, 04.11.78 (прототип

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых вычислительных машин | 1981 |

|

SU964647A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1221666A1 |

| Устройство для сопряжения ведущей и N ведомых цифровых вычислительных машин | 1988 |

|

SU1531104A1 |

| Устройство для отладки и контроля хода программ | 1988 |

|

SU1529227A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1986 |

|

SU1348844A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для отладки программ | 1986 |

|

SU1363221A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| Устройство для контроля времени выполнения программ | 1984 |

|

SU1223235A1 |

LiJ Сл

Авторы

Даты

1981-09-30—Публикация

1979-09-10—Подача