( УСТРОЙСТВО ДЛЯ ТЕСТОВОГО КОНТРОЛЯ ЦИФРОВЫХ

1

Изобретение относится к вычислительной технике и может 6Mtb использовано для контроля и поиска неисправностей в цифровых вычислительных машинах.

Известно устройство для полуавтоматического контроля цифровых управляющих систем, содержащее блок задания операций, блок управления, блок переключения частоты, сдвигающий регистр и блок индикации, входом связанный с первым выходом контролируемой цифровой управляющей системы, первый вход которой соединен с первым выходом блока управления, а второй выход блока управления подключен к первому входу блока переключения частоты, взаимосвязанного также со сдвигающим регистром. Второй вход контролируемой цифровой управляющей системы подключен к выходу блока задания операций. Взаимосвязан ного со сдвигающим регистром р. ВЫЧИСПИТЕЛЬНЫХ МАШИН

Известноеустройство не контроли,рует датчик микроопераций командного процессора цифровой управляющей системы, кроме того, в этом устройстве проверяется выполнение только одной операции, а не реальное сочетание исполнения операций,- Его недостатком является также большое количество связей.

0 Наиболее близким по своей технической сущности и достигаемому положительному эффекту к данному изобретению является устройство для контроля цифровых управляющих систем

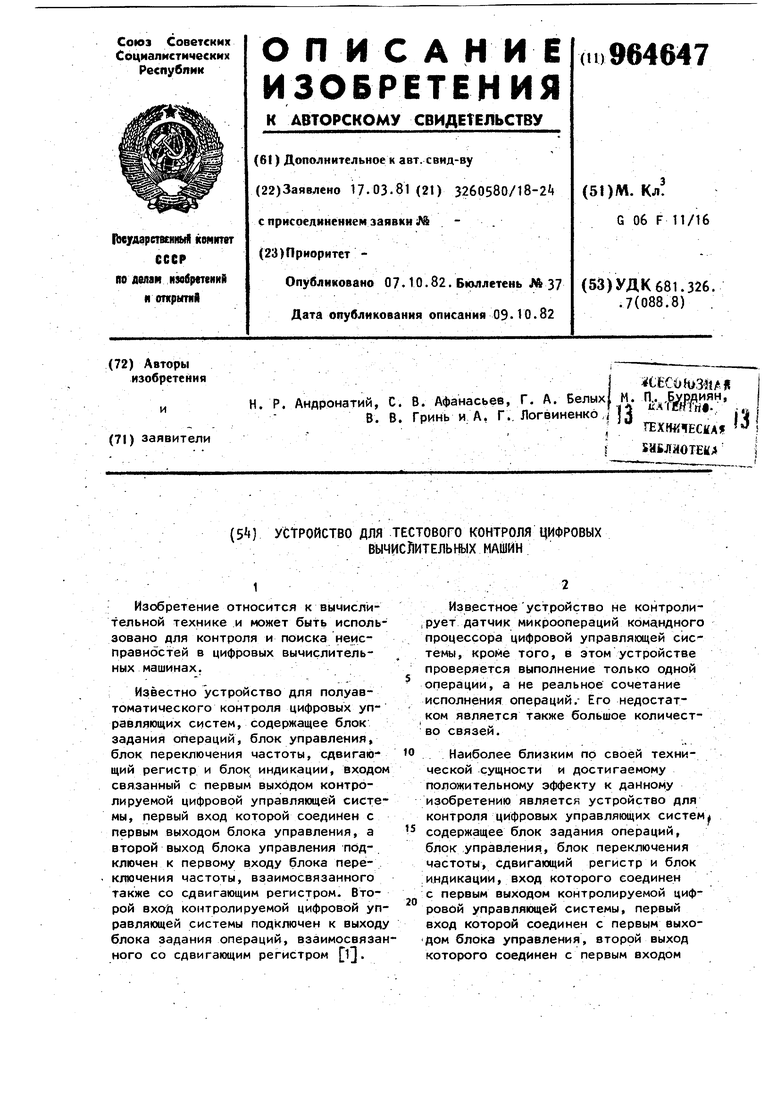

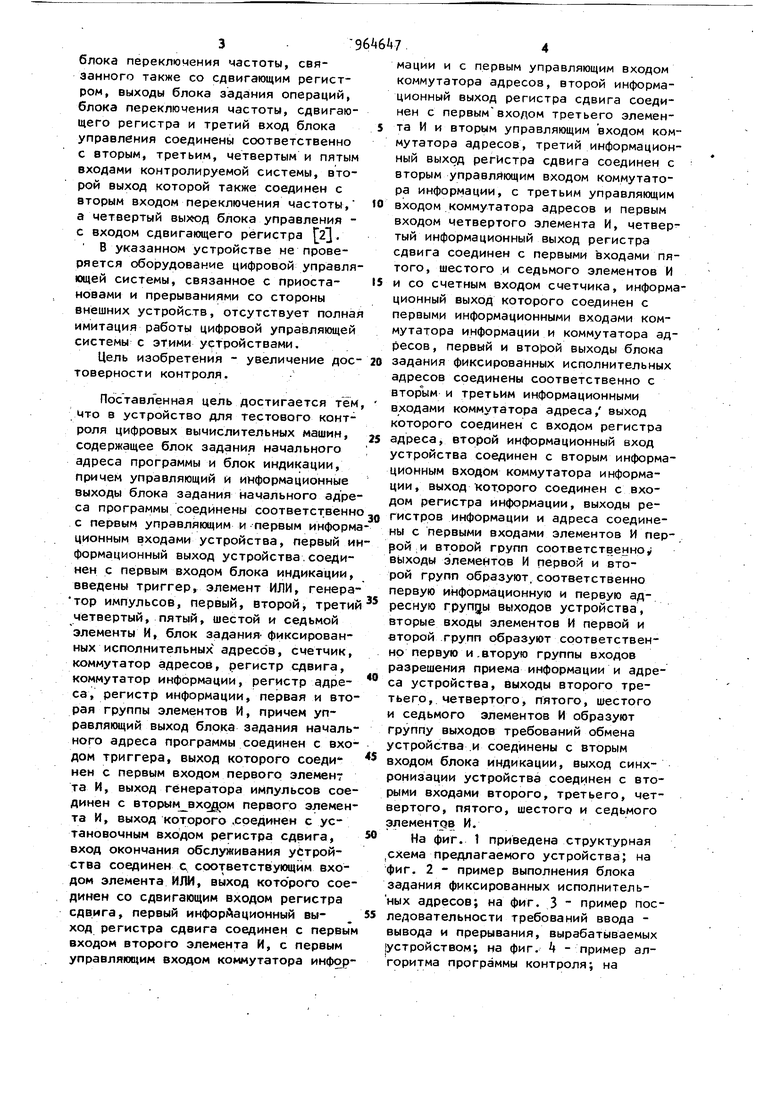

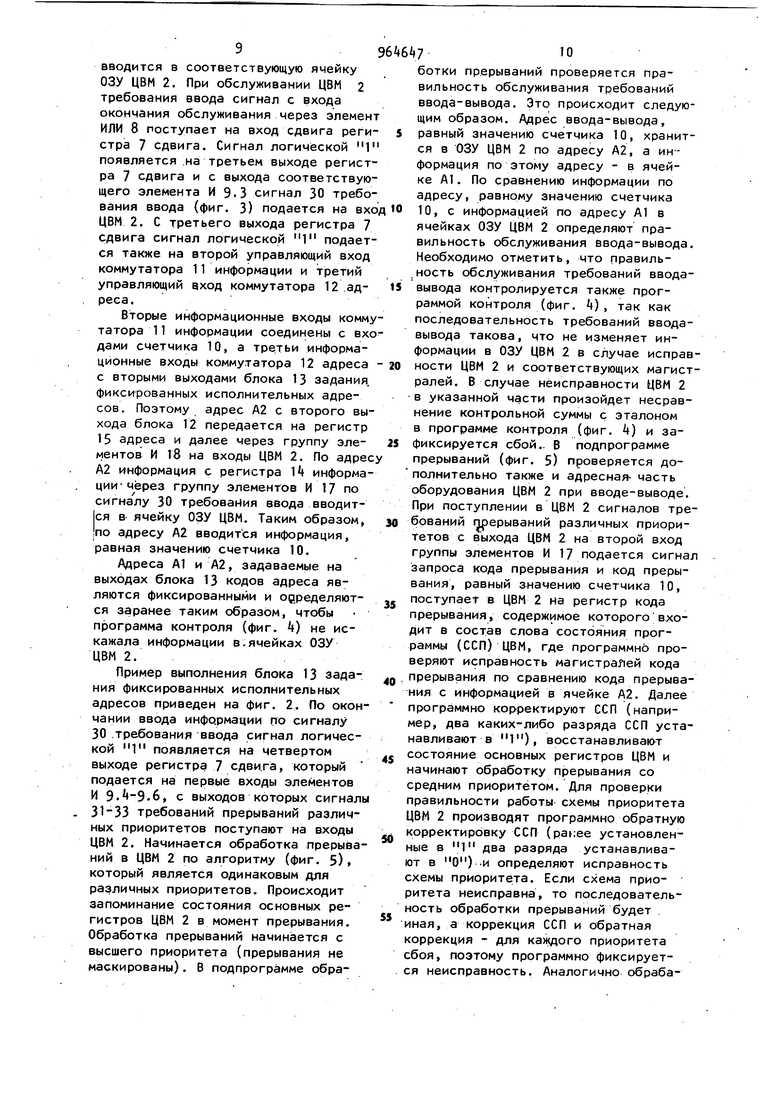

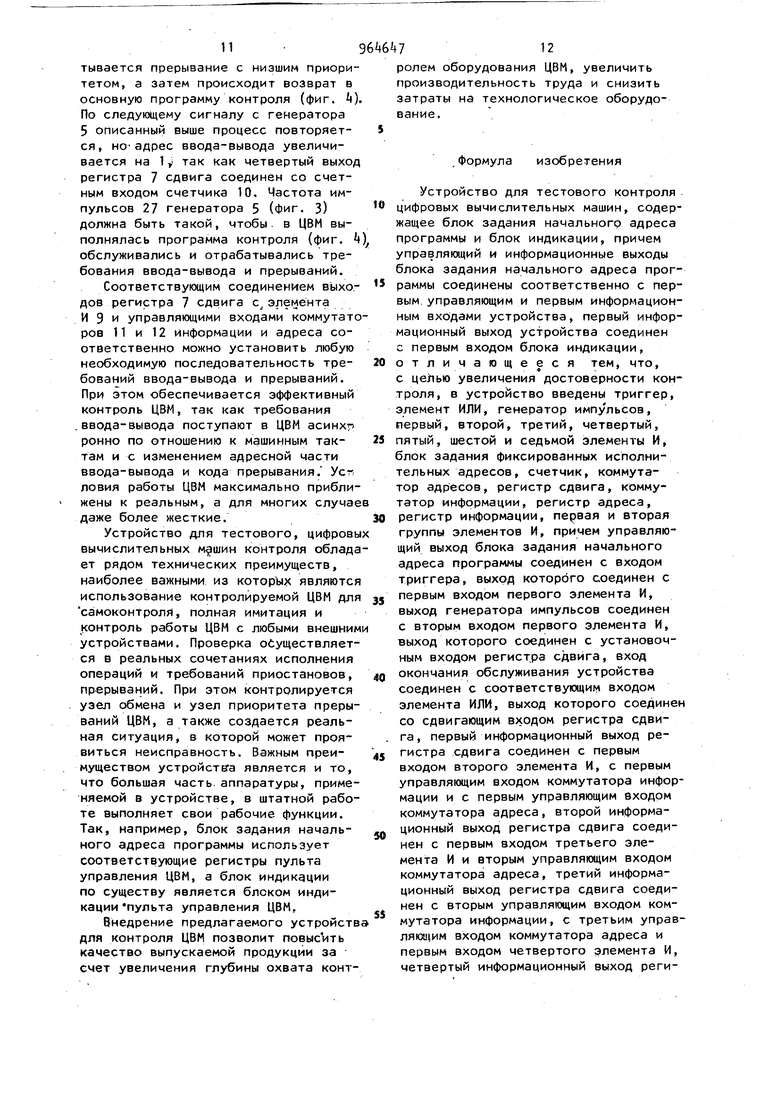

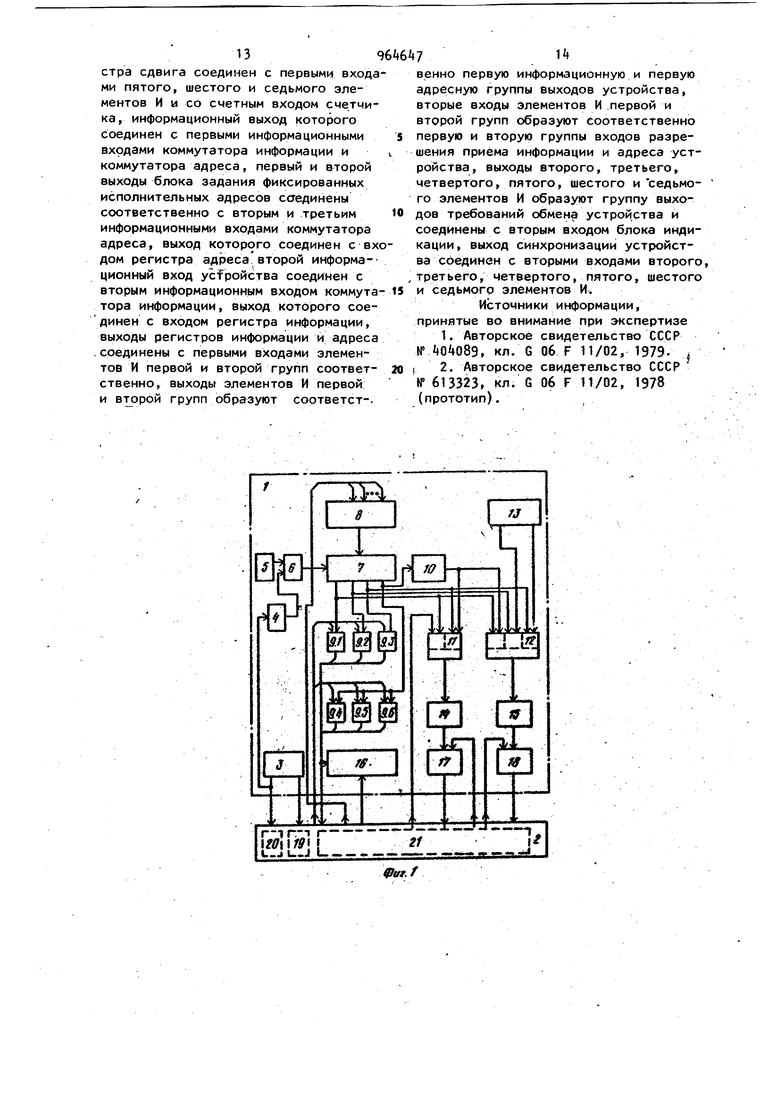

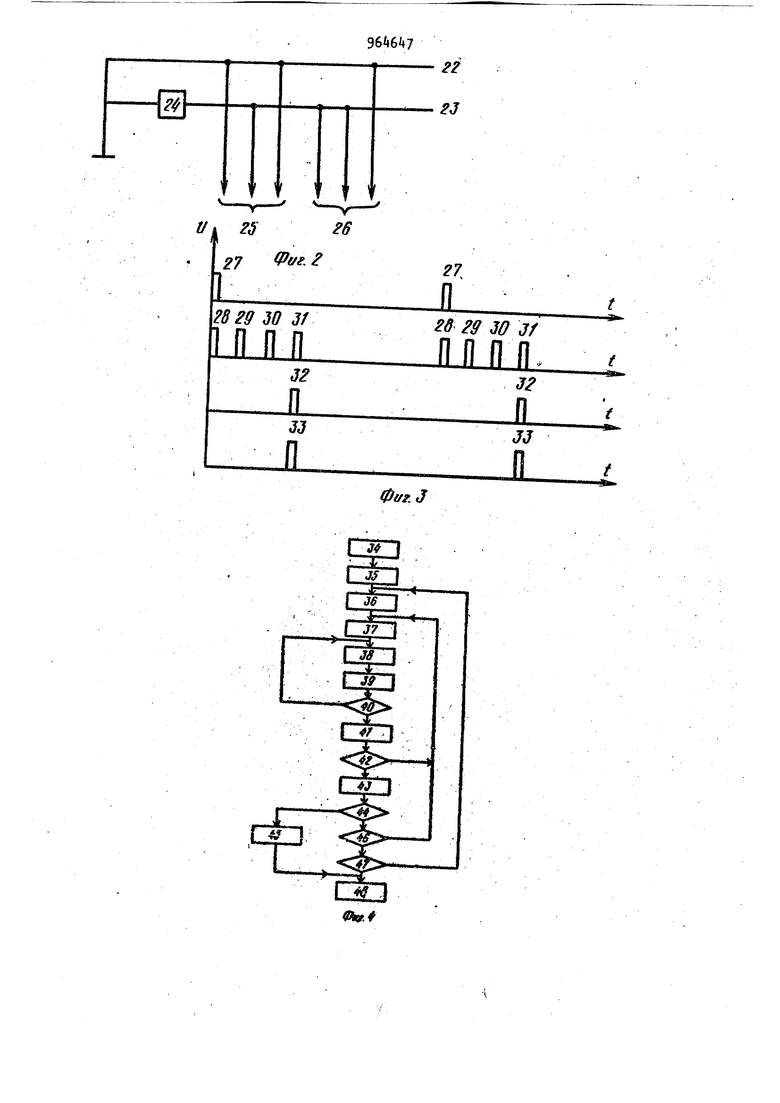

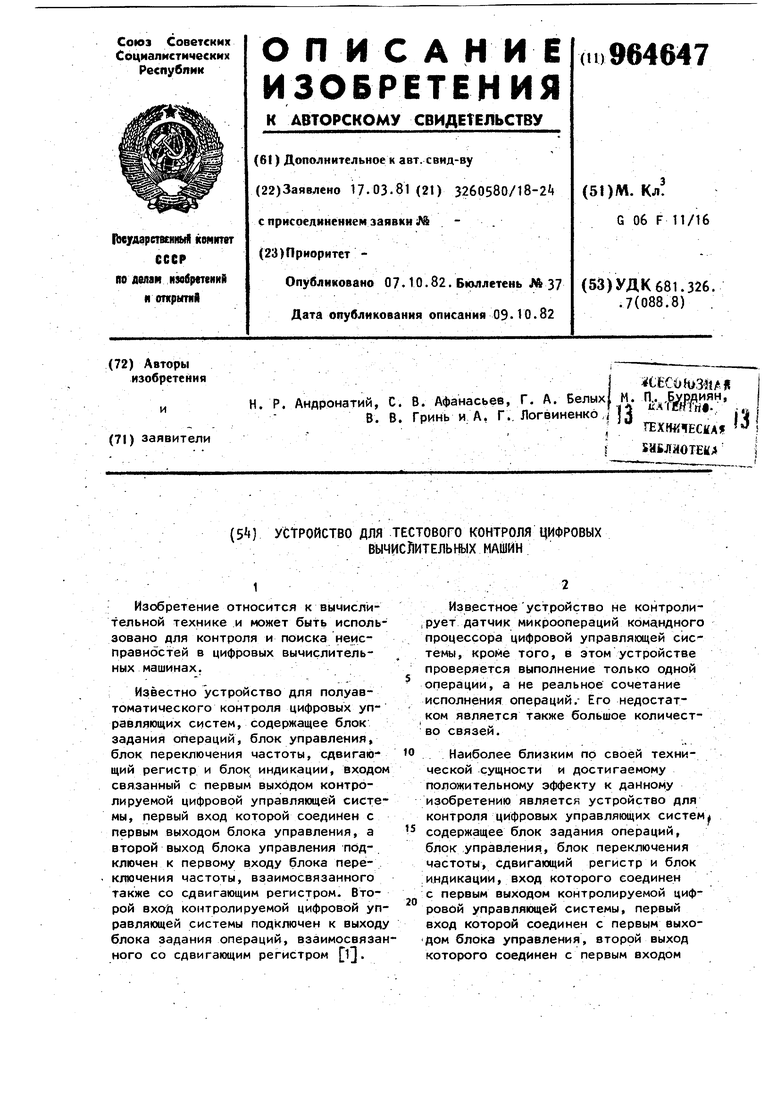

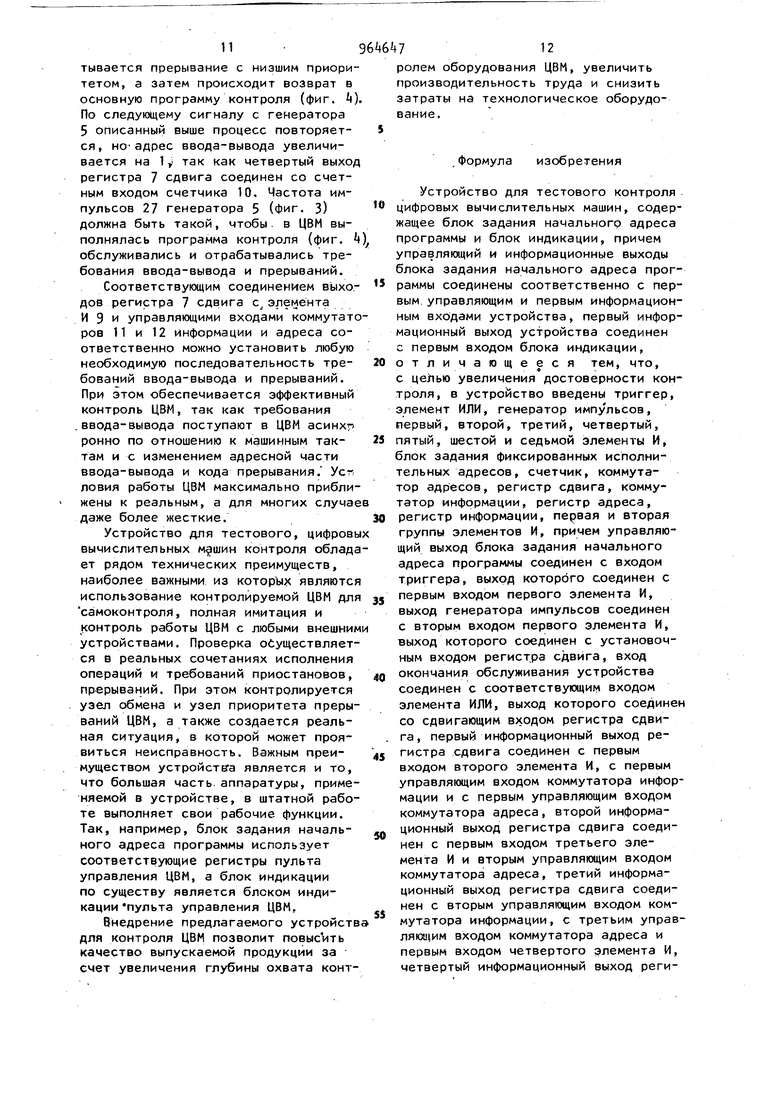

5 содержащее блок задания операций, блок управления, блок переключения частоты, сдвигающий регистр и блок индикации, вход которого соединен с первым выходом контролируемой циф20ровой управляющей системы, первый вход которой соединен с первым выходом блока управления, второй выход которого соединен с первым входом 3 . -9 блока переключения частоты, связанного также со сдвигающим регистром, выходы блока задания операций, блока переключения частоты, сдвигающего регистра и третий вход блока управления соединены соответственно с вторым, третьим, четвертым и пятым входами контролируемой системы, второй выход которой также соединен с вторым входом переключения частоты, а четвертый выж5Д блока управления с входом сдвигающего регистра 2. В указанном устройстве не проверяется оборудование цифровой управля ющей системы, связанное с приостановами и прерываниями со стороны внешних устройств, отсутствует полна имитация работы цифровой управляющей системы с этими устройствами. Цель изобретения - увеличение достоверности контроля. Поставленная цель достигается тем, Что в устройство для тестового контроля цифровых вычислительных машин, содержащее блок задания начального адреса программы и блок индикации, причем управляющий и информационные выходы блока задания начального адреса программы соединены соответственно с первым управляющим и первым информа ционным входами устройства, первый ин формационный выход устройства.соединен с первым входом блока индикации, введены триггер, элемент ИЛИ, генератор импульсов, первый, второй, третий четвертый, пятый, шестой и седьмой элементы И, блок задания фиксированных исполнительных адресов, счетчик, коммутатор адресов, регистр сдвига, коммутатор информации, регистр адреса, регистр информации, первая и вторая группы элементов И, причем управляющий выход блока задания начального адреса программы соединен с входом триггера, выход которого соеди нен с первым входом первого элемент та И, выход генератора импульсов соединен с втррым вхо§рм первого элемента И, выход которого .соединен с установочным входом регистра сдвига, вход окончания обслуживания устройства соединен с соответствующим входом элемента ИЛИ, выход которого соединен со сдвигающим входом регистра сдвига, первый информационный выход регистра сдвига соединен с первым входом вторюГо элемента И, с первым управляющим входом коммутатора инфор7мации и с первым управляющим входом коммутатора адресов, второй информационный выход регистра сдвига соединен с первымвходом третьего элемента И и вторым управляющим входом коммутатора адресов, третий информационный выход регистра сдвига соединен с вторым управляющим входом коммутатора информации, с третьим управляющим входом коммутатора адресов и первым входом четвертого элемента И, четвер тый информационный выход регистра сдвига соединен с первыми входами пятого, шестого и седьмого элементов И и со счетным входом счетчика, информационный выход которого соединен с первыми информационными входами коммутатора информации и коммутатора адресов , первый и второй выходы блока задания фиксированных исполнительных адресов соединены соответственно с втор°ым и третьим информационными в ходами коммутатора адреса, выход которого соединен с входом регистра второй информационный вход адреса. устройства соединен с вторым информационным входом коммутатора информации, выход которого соединен с входом регистра информации, выходы регистров информации и адреса соедине„ с первыми входами элементов И перрои И ВТОРОЙ групп соответственно,; выходы элементов И первой и второй групп образуют, соответственно первую информационную и первую адресную групцы выходов устройства, вторые входы элементов И первой и второй групп образуют соответственно первую и .вторую группы входов разрешения приема информации и адреса устройства, выходы второго третьего, четвертого, пятого, шестого и седьмого элементов И образуют группу выходов требований обмена устройства .и соединены с вторым входом блока индикации, выход синхронизации устройства соединен с вторыми входами второго, третьего, четвертого, пятого, шестого и седьмого элементов И. На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - пример выполнения блока задания фиксированных исполнительных адресов; на фиг. 3 пример последовательности требований ввода вывода и прерывания, вырабатываемых устройством; на фиг. k - пример алгоритма программы контроля; на фиг. 5 алгоритм программы обработки прерываний. Устройство 1 для контроля ЦВМ 2 содержит блок 3 задания начального адреса программы, триггер 4, генератор-5 импульсов, элементов, регистр 7сдвига, элемент ИЛИ 8, элементы И 9..6, счетчик 10, коммутатор 11 информации, коммутатор 12 адресов блок 13 задания фиксированных исполнительных адресов, регистр 1 информации, регистр 15 адреса, блок 16 индикации, первую группу элементов И 17, вторую группу элементов И 18. 8ЦВМ 2 условно показаны счетчик 19 команд, устройство 20 управления, блок 21 обмена и прерываний. Управля ющий и информационные выходы блока 3 задания начального адреса программы соединены соответственно с первым управляющим и первым информационным выходами устройства, причем управляю щий выход блока 3 задания начального адреса программы соединен также с входом триггера 4, выход которого со единен с первым входом элемента И 6, Второй вход которого соединен с выхо дом генератора 5 импульсов выход элемента И 6 - с установочным входом регистра 7 сдвига, вход окончания обслуживания устройства - с соответствующим входом элемента ИЛИ 6, выход которого соединен со сдвигающим входом регистра 7 сдвига, первый информационный выход которого соединен с первым входом элемента И 9.1-, с первым управляющим входом коммутатора 11 .информации и. с первым управЛЯЮ1ДИМ входом коммутатора 12 адресов , второй информационный выход регистра .7 сдвига - с первым вторым эл ментом И 9.2 и вторым управляющим входом коммутатора 12 адресов, трети .информационный выход регистра 7 сдви га - с вторым управляющим входом коммутатора 11 информации, с третьим управляющим входом коммутатора 12 адресов и первым входом элемента И 9-3, четвертый информационный выход регистра 7 сдвига - с первыми входами элементов И 9..2, 9«3, и со счетным входом счетчика 10, информационный выход которого соединен .с первыми информационными входами коммутатора 11 информации и коммутатора 12 адресов, первый и второй выходы блока 13 задания фиксированных исполнительных адресов соединены соответственно с вторым и третьим. информационным входами коммутатора 12 адреса, выход которого соединен с входом регистра 15 адреса, первый информационный вход устройства соединен с первым входом блока 16 индикации , а второй информационный вход устройства - с вторым информационным входом коммутатора 11 информации, выход которого соединен с входом регистра 1 информации. Выходы регистра 1Ц информации и регистра 15 адреса соединены с первыми входами элементов И первой 17 и второй 18 групп соответственно, выходы элементов И первой 17 и второй 18 групп образуют соответственно первую информационную и первую адресную группы выходов устройства. Вторые входы элементов И первой 17 и второй 18 групп образуют соответственно первую и вторую группы разрешения приема информации и адреса устройства. Выходы элементов И 9..6 образуют группу выходов требований обмена устройства и соединены с вторым входом блока 16 индикации, а вход.синхронизации устройства - с вторыми входами элементов И 9.1-9.6. Блок 13 задания фиксированных исполнительных адресов для выдачи в восьмеричном коде адреса 2б состоит из шины 22 логического нуля, шины 23логической единицы; элемента И-НЕ 24и шины 25 и 26 адреса. Последовательность требований ввода-вывода и прер1ивания вырабатыва ют устройством 1 для контроля ЦВМ на выходах элементов 2И 9 и подают в контролируемую ЦВМ 2 на третий вход. На фиг. 2 изображены сигналы 27 на выходе генератора 5i сигналы 28 требований вывода, сигналы 30 требований ввода, сигналы требований прерываний различных приоритетов. Алгоритм программы контроля, по которой работает контролируемая ЦВМ 2, указывает следующие блочные символы; 34 - начало программы; 35 формирование слов состояния программы; 36 занесение адреса строки списка команд в ячейку хранения адреса строки списка команд; 37 обнуление счетчика повторения исполнения команды из списка команд; 38 - исполнение команды, выбранной по содержимому ячейки хранения адреса строки списка команд и записи результата в ячейку оперативного запоминающего устройства (ОЗУ); 39 увеличение на единицу содержимого счетчика повторения исполнения команд и адресной части команды; Q - условие равенства содержимого счетчика повторения команды с требуемым числом повторений; k - увеличение на един цу содержимого ячейки адреса строки списка команд; 42 - условие готовности к контролю группы команд; 3 суммирование полученной в результате исполнения группы команд информации в ОЗУ; 4 - условие равенства полученной суммы с этало. ном; kS - формирование признака сбоя; 6 - условие окончания списка команд; kj - условие зацикливания программы; 8 - конец программы В алгоритме программы обработки прерываний указаны следующие блочные символы: 49 - начало программы; 50- запоминание состояния основных регистров ЦВМ в момент прерывания; 51 проверка правильности обслуживания требований ввода-вывода; 52- проверка исправности магистралей ввода кода прерывания; 53 - про верка правильности работы схемы при ритета контролируемой ЦВМ; 5 вос становление состояния основных регистров контролируемой ЦВМ и уход в программу контроля; 55 выработка сигналов неисправности; 5б - останова; 57 конца программы. Устройство для тестового контрол ЦВМ работает следующим образом. Блок 3 задания начального адреса программы и блок t6 индикации представляет по своей сути инженерный пульт управления ЦВМ 2. С клавиатур блока 3 задания начального адреса программы начальный адрес программы контроля заносится на счетчик 19 ко манд ЦВМ 2 путем воздействия управл ющих сигналов . блока 3 задания начального адреса программы на устройство 20 управления ЦВМ 2 и произ водится запуск программы контроля, (фиг. ). Контролируемая ЦВМ 2 на чинает работу по программе контроля реализующей многократ ное исполнение каждой команды из системы команд ЦВМ 2 с изменением адресной части команды и записью результатов каждого исполнения в ячейки ОЗУ ЦВМ. После исполнения :сгруппы команд содержимое указанных ячеек ОЗУ ЦВМ суммируется и сравнивается с эталоном, полученным на заведомо испра ной ЦВМ. 7 .8 Одновременно с запуском программы контроля в ЦВМ 2 сигнал с второго выхода блока 3 задания начального адреса программ;устанавливает в единичное состояние триггер Ц и сигналы с выхода генератора 5 через элемент И 6 поступают на установочный вход первого разряда регистра 7 сдвига. Частота импульсов 27 генератора 5 (фиг. 3) примерно на два порядка ниже частоты машинных тактов ЦВМ 2. На первом выходе регистра 7 сдвига появляется сигнал логической единицы, который поступает на первый вход элемента И 9.1. На выходе элемента И 9-1 появляется сигнал 28 требования вывода (фиг. 3), который подается в блок 21 обмена и прерываний. Сигнал с первого выхода регистра 7 сдвига одновременно подается также на первые управляющие входы коммутатора 11 информации и коммутатора 12 адреса. Код адреса со счетчика 10 поступает на первые информационные входы коммутатора 12 адреса и далее в регистр 15 адреса. Этот адрес с регистра 15 адреса через группу элементов И 17 передается в момент времени, задаваемый с входа синхронизации, на вход ЦВМ 2. По этому адресу по сигналу 28 требования вывода (фиг. 3) информация из ячейки ОЗУ с ЦВМ 2 передается на первые информационные входы коммутатора 11 информации и далее в регистр информации. ЦВМ 2 выдает также по второму выходу сигнал об обслуживании требования вывода, который через элемент ИЛИ 8 поступает на вход сдвига регистра 7 сдвига. Сигнал логической 1, который появляется уже на втором выходе регистра 7 сдвига, подаётся на первый вход элемента И 9.2, по второму входу поступает сигнал синхронизации с входа синхрЬнизаци 1 с выхода элемента И , сигнал 29 требования ввода (фиг. 3) подается на вход ЦВМ 2. Сигнал логической 1 с второго выхода регистра 7 сдвига подается на второй управляющий вход коммутатора 12 адреса, на вторые информационные входы которого с блока 13 задания фиксированных исполнительных адресов подается код адреса А1. Код адреса А1 передается в регистр 15 адреса и далее через группу элементов И 18 на входы ЦВМ 2. По адресу А1 по сигналу 29 требования ввода (фиг. 3) информация с регистра И информации вводится в соответствующую ячейку ОЗУ ЦВМ 2. При обслуживании ЦВМ 2 требования ввода сигнал с входа окончания обслуживания через элемен ИЛИ 8 поступает на вход сдвига реги стра 7 сдвига. Сигнал логической 1 появляется на третьем выходе регист ра 7 сдвига и с выхода соответствую щего элемента И 9.3 сигнал 30 требо вания ввода (фиг. 3) подается на вх ЦВМ 2. С третьего выхода регистра 7 сдвига сигнал логической 1 подает ся также на второй управляющий вход коммутатора 11 информации и третий управляющий вход коммутатора 12 адреса. Вторые информационные входы комм татора 11 информации соединены с вх дами счетчика 10, а информационные входы коммутатора 12 адреса с вторыми выходами блока 13 задания фиксированных исполнительных адресов. Поэтому адрес А2 с второго вы хода блока 12 передается на регистр 15 адреса и далее через группу элементов И 18 на входы ЦВМ 2, По адре А2 информация с регистра 14 информа ции -через группу элементов И 17 по сигналу 30 требования ввода вводится в ячейку ОЗУ ЦВМ. Таким образом, по адресу А2 вводится информация, равная значению счетчика 10. Адреса А1 и А2, задаваемые на выходах блока 13 кодов адреса являются фиксированными и орределяются заранее таким образом, чтобы программа контроля (фиг. 4) не искажала информации в.ячейках ОЗУ ЦВМ 2. Пример выполнения блока 13 задания фиксированных исполнительных адресов приведен на фиг. 2. По окон чании ввода информации по сигналу 30 .требования ввода сигнал логической 1 появляется на четвертом выходе регистра 7 сдви.га, который подается на первые входы элементов И (, с выходов которых сигнал 31-33 требований прерываний различных приоритетов поступают на входы ЦВМ 2. Начинается обработка прерыва ний в ЦВМ 2 по алгоритму (фиг. 5) который является одинаковым для различных приоритетов. Происходит запоминание состояния основных регистров ЦВМ 2 в момент прерывания. Обработка прерываний начинается с высшего приоритета (прерывания не маскированы). В подпрограмме обраОботки прерываний проверяется правильность обслуживания требований ввода-вывода. Это происходит следующим образом. Адрес ввода-вывода, равный значению счетчика 10, хранится в ОЗУ ЦВМ 2 по адресу А2, а информация по этому адресу - в ячейке А1. По сравнению информации по адресу, разному значению счетчика 10, с информацией по адресу А1 в ячейках ОЗУ ЦВМ 2 определяют правильность обслуживания ввода-вывода. Необходимо отметить, что правильность обслуживания требований вводавывода контролируется также программой контроля (фиг. t) , так как последовательность требований вводавывода такова, что не изменяет информации в ОЗУ ЦВМ 2 в случае исправности ЦВМ 2 и соответствующих магистралей. В случае неисправности ЦВМ 2 в указанной части произойдет несравнение контрольной суммы с эталоном в программе контроля (фиг. 4) и зафиксируется сбой.. В подпрограмме прерываний (фиг. 5) проверяется дополнительно также и aдpecнaя часть оборудования ЦВМ 2 при вводе-выводе. При поступлении в ЦВМ 2 сигналов требованийпрерывании различных приоритетов с выхода ЦВМ 2 на второй вход группы элементов И 17 подается сигнал запроса кода прерывания и код прерывания, равный значению счетчика 10, поступает в ЦВМ 2 на регистр кода прерывания, содержимое которого входит в состав слова состояния программы (ССП) ЦВМ, где программно проверяют исправность магистралей кода прерывания по сравнению кода прерывания с информацией в ячейке А2. Далее программно корректируют ССП (например, два каких-либо разряда ССП устанавливают а 1), восстанавливают состояние основных регистров ЦВМ и начинают обработку прерывания со средним приоритетом. Для проверки правильности работы схемы приоритета ЦВМ 2 производят программно обратную корректировку ССП (ракее установленные в 1 два разряда устанавливают в О) -и определяют исправность схемы приоритета. Если схема приоритета неисправна, то последовательность обработки прерываний будет иная, а коррекция ССП и обратная коррекция - для каждого приоритета сбоя, поэтому программно фиксируется неисправность. Аналогично обрабатывается прерывание с низшим приоритетом, а затем происходит возврат в основную программу контроля (фиг. it) По следующему сигналу с генератора 5 описанный выше процесс повторяется, но-адрес ввода-вывода увеличивается на 1V так как четвертый выход регистра 7 сдвига соединен со сметным входом счетчика 10. Частота импульсов 27 генератора 5 (фиг. 3) должна быть такой, чтобы, в ЦВМ выполнялась программа контроля (фиг. обслуживались и отрабатывались требования ввода-вывода и прерываний. Соответствующим соединением выходов регистра 7 сдвига с.элемента И 9 и управляющими входами коммутато ров 11 и 12 информации и адреса соответственно можно установить любую необходимую последовательность требований ввода-вывода и прерываний. При этом обеспечивается эффективный контроль ЦВМ, так как требования .ввода-вывода поступают в ЦВМ асинхронно по отношению к машинным тактам и с изменением адресной части ввода-вывода и кода прерывания. Усг ловия работы ЦВМ максимально приближены к реальным, а для многих случае даже более жесткие. Устройство для тестового, цифровы вычислительных контроля облада ет рядом технических преимуществ, наиболее важными из которЪ1 являются использование контролируемой ЦВМ для самоконтроля, полная имитация и контроль работы ЦВМ с любыми внешним устройствами. Проверка осуществляется в реальных сочетаниях исполнения операций и требований приостановов, прерываний. При этом контролируется узел обмена и узел приоритета прерываний ЦВМ, а также создается реальная ситуация, в которой может проявиться неисправность. Важным преймуществом устройства является и то, что большая часть аппаратуры, применяемой а устройстве, в штатной работе выполняет свои рабочие функции. Так, например, блок задания начального адреса программы использует соответствующие регистры пульта управления ЦВМ, а блок индикации по существу является блоком индикации пульта управления ЦВМ, Внедрение предлагаемого устройств для контроля ЦВМ позволит повысить качество выпускаемой продукции за счет увеличения глубины охвата контролем оборудования ЦВМ, увеличить производительность труда и снизить затраты на технологическое оборудование. .Формула изобретения Устройство для тестового контроля цифровых вычислительных машин, содержащее блок задания начального адреса программы и блок индикации, причем управляющий и информационные выходы блока задания начального адреса программы соединены соответственно с первым, управляющим и первым информационным входами устройства, первый информационный выход устройства соединен с первым входом блока индикации, отличающееся тем, что, с целью увеличения достоверности контроля, в устройство введены триггер, элемент ИЛИ, генератор импульсов, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И, блок задания фиксированных исполнительных адресов, счетчик, коммутатор адресов, регистр сдвига, коммутатор информации, регистр адреса, регистр информации, первая и вторая группы элементов И, причем управляющий выход блока задания начального адреса программы соединен с входом триггера, выход которого соединен с первым входом первого элемента И, выход генератора импульсов соединен с вторым входом первого элемента И, выход которого соединен с установочным входом регистра сдвига, вход окончания обслуживания устройства соединен с соответствующим входом элемента ИЛИ, выход которого соединен со сдвигающим входом регистра сдвига, первый информационный выход регистра сдвига соединен с первым входом второго элемента И, с первым управляющим входом коммутатора информации и с первым управляющим входом коммутатора адреса, второй информационный выход регистра сдвига соединен с первым входом третьего элемента И и вторым управляющим входом коммутатора адреса, третий информационный выход регистра сдвига соединен с вторым управляющим входом коммутатора информации, с третьим управляющим входом коммутатора адреса и первым входом четвертого элемента И, четвертый информационный выход региcTpa сдвига соединен с первыми вход ми пятого, шестого и седьмого элементов И и со счетным входом счетчи ка, информационный выход которого соединен с первыми информационными входами коммутатора информации и коммутатора адреса, первый и второй выходы блока задания фиксированных исполнительных адресов соединены соответственно с вторым и третьим информационными входами коммутатора адреса, выход которого соединен с вх дом регистра адресавторой информационный вход устройства соединен с вторым информационным входом коммута тора информации, выход которого соединен с входом регистра информации, выходы регистров информации и адреса .соединены с первыми входами элементов И первой и второй групп соответственно, выходы элементов И первой и второй групп образуют соответст-. 7 венно первую информационную и первую адресную группы выходов устройства, вторые входы элементов И первой и второй групп образуют соответственно первую и вторую группы входов разрешения приёма информации и адреса устройства, выходы второго, третьего, четвертого, пятого, шестого и седьмого элементов И образуют группу выходов требований обмена устрой.ства и соединены с вторым входом блока индикации, выход синхронизации устройства соединен с вторыми входами второго, третьего, четвертого, пятого, шестого и седьмого элементов И. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № i 04o89, кл. G 06 F 11/02, 19792, Авторское свидетельство СССР 613323 кл. G 06 F 11/02, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля магистралей в ЭВМ | 1981 |

|

SU970376A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для контроля цифровых интегральных схем | 1978 |

|

SU943747A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1661779A1 |

| Устройство для проверки функциональных блоков | 1980 |

|

SU1008745A1 |

| Устройство для контроля хода программы | 1988 |

|

SU1663612A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

//1 /J

Фг/г.5

Авторы

Даты

1982-10-07—Публикация

1981-03-17—Подача