Изобретение относится к вычислительной технике и может быть использовано для отладки в реальном масштабе времени программ специализированных вычислительных машин (СЦВМ).

Цель изобретения - повышение быстродействия.

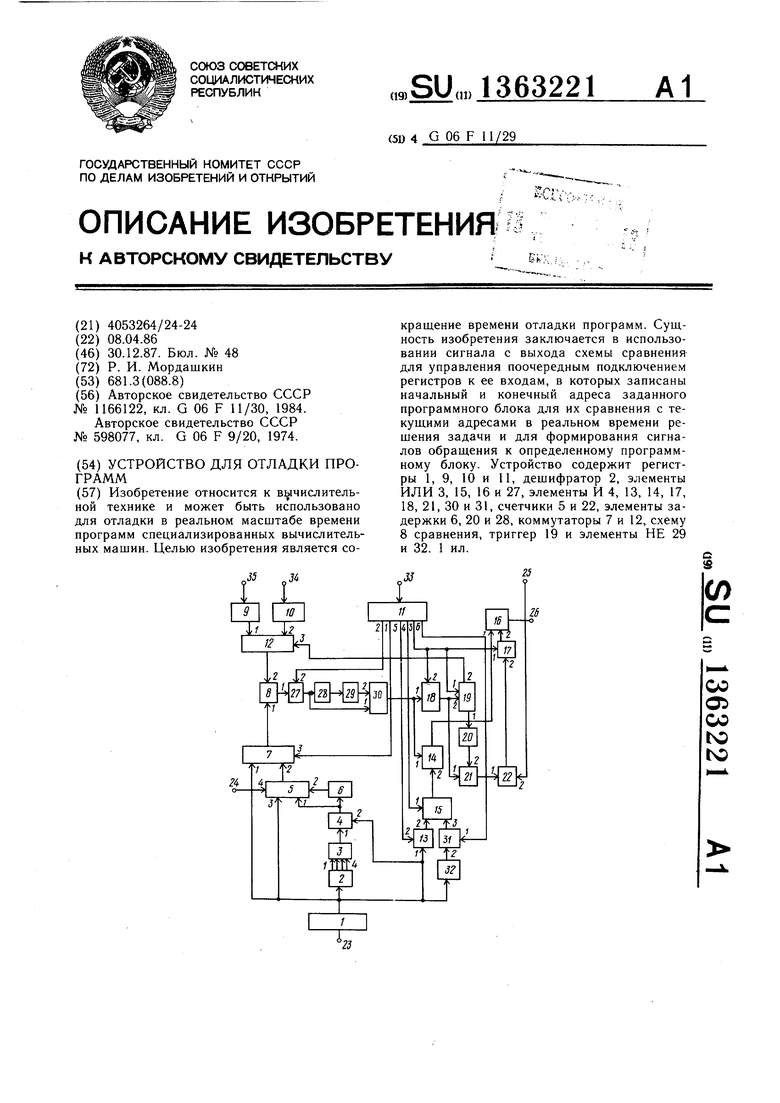

На чертеже приведена схема устройства для отладки программ.

Устройство содержит регистр 1 команд, дешифратор 2, первый элемент ИЛИ 3, первый элемент И 4, счетчик 5 команд, первый элемент б задержки, первый коммутатор 7, схему 8 сравнения, регистр 9 первого перехода, регистр 10 второго перехода, регистр 11 управления, второй коммутатор 12, второй 13 и третий 14 элементы И, третий 15 и четвертый 16 элементы ИЛИ, седьмой 7 и шестой 18 элементы И, триггер 19, третий элемент 20 задержки, восьмой элемент И 21, счетчик 22 циклов, вход 23 команды, вход 24-признака команды, вход 25 задания количества циклов устройства, выход 26 прерывания устройства, второй элемент ИЛИ 27, второй элемент 28 задержки, элемент НЕ 29, четвертый элемент И 30, третий элемент И 31,, первый элемент НЕ 32, вход 33 задания режима устройства, вход 34 второго перехода устройства и вход 35 первого перехода устройства.

Устройство может работать в режиме фиксации количества последовательных прохождений программы, проверяемой СЦВЧ через программно-устанавливаемые границы, и в режиме фиксации обраш,ения СЦВМ к полю памяти по заданному числу, команде или адресу. Режим работы определяется текуш,ими задачами отладки программ и устанавливается кодом на выходах регистра 11 управления, который через вход 33 устройства подключен к ЦВМ, управляющей отладкой программ СЦВМ.

В режиме фиксации количества проходов программы через заданные границы в регистры 9 и 10 через входы устройства 35 и 34 соответственно ЦВМ, управляюш,ая отладкой, записывает коды начального и конечного адресов заданного программного блока, а в регистр 11 управления через вход 33 - код, который на первом выходе регистра 11 управления формирует сигнал, разрешающий подключение выхода счетчика 5 к второму канальному входу коммутатора 7, а на третьем выходе - сигнал, разрешающий прохождение сигналов через элементы И 17 и 18, передний фронт которого устанавливает триггер 19 в исходное состояние, при этом с первого выхода триггера 19 через элемент 20 задержки устанавливается сигнал запрета на элемент И 21, а с второго выхода - сигнал на вход управления коммутатора 12, разрешающий подключение через коммутатор 12 регистра 9, в котором записан начальный адрес программного блока, к второму входу схемы 8

сравнения. При этом пятый, шестой и четвертый выходы регистра 11 управления запрещают соответственно прохождение сигналов через элементы И 13 и 31 и формируют сигнал на выходе элемента ИЛИ 15, запрещающий прохождение через элемент И 14 сигналов с выхода схемы 8 сравнения. В счетчик 22 через вход 25 устройства ЦВМ, управляющая отладкой, записывает код, соответ„ ствующий предполагаемому числу циклов программы через заданные границы.

В процессе отладки из проверяемой СЦВМ командная и числовая информация поступает в устройство по входу 23 в регистр 1 команд. Цо входу 24 устройства из

проверяемой СЦВМ в каждом цикле ее работы поступает признак команды, увеличивающий показания счетчика 5 команд на единицу. С выхода регистра 1 разряды, которые определяют команды условного и безусловного переходов, подключены к входу дешифра0 тора 2, а разряд, квалифицирующий код в регистре 1 как число или команду - к вторым входам элементов 4 и 13 и через элемент НЕ 32 к второму входу элемента И 31. Таким образом, при появлении в регистре 1

5 команд команды условного или безусловного перехода, сигнал с выхода элемента ИЛИ 3 проходит через элемент И 4, так как на его второй вход подается разрешение от квалифицирующего разряда из регистра 1 команд, и своим передним фронтом обнуляет счет0 чик 5 через первый вход, а через элемент 6 задержки передним фронтом разрешает через второй вход запись адресной части кода из регистра 1 на информационный вход 3 счетчика 5 команд. В следующем цикле после прихода сигнала на входах (приз5 нак команды) содержимое счетчика увеличивается на единицу и соответствует адресу числа или команды, который поступает на приемный регистр 1 по входу 23. В данном режиме выход счетчика 5 через коммутатор 7 подключен к первому входу схемы 8 сравнения. При совпадении кодов на первом и втором входах схемы 8 сравнения вырабатывается сигнал, который через элемент И 27 поступает на элемент 28 задержки, который вместе с элемен5 том НЕ 29 и элементом И 30 образует схему формирования и.мпульса от переднего фронта сигнала, с выхода которой импульс через элемент 18 И поступает на счетный вход триггера 19 и переводит его в единичное состояние, при этом сигнал второго выхода

0 триггера 19 подключает к схеме 8 сравнения через коммутатор 12 регистр 10, в котором записан код конечного адреса программного- блока.

Сигнал через элемент И 21 не прох9дит, так как в данный момент на его второй вход

5 подается через элемент 20 задержки запрет, сохранивщийся от предыдущего состояния триггера 19. При этом время задержки на элементе 20 задержки больше, чем дли0

тельность импульса на входе триггера 19. Таким образом с первого выхода триггера через элемент 20 задержки поступает на второй вход элемента И 21 разрешение на прохождение следующего сигнала с выхода схемы 8 сравнения, который фиксирует конечный адрес программного блока и уменьшает содержимое счетчика 22 на единицу.

Когда содержимое счетчика становится равным О, с его выхода через элемент И 17 и элемент ИЛИ 16 поступает сигнал на выход 26 устройства, который можно использовать для организации прерывания в ЦВМ, управляющей отладкой, или в отлаживаемой СЦВМ.

Если при рещении задачи количество проходов программы через заданные границы меньше, чем предполагалось, и содержимое счетчика 22 не равно О, то, сохраняя в регистре 11 управления код организации данного режима и последовательность, меняя во втором разряде «О на «1 и т.д., можно довести содержимое счетчика 22 до 0. При этом можно определить количество проходов программы через заданные границы, изменяя значение во втором разряде регистра 11 управления через промежутки времени, достаточные на обработку прерывания ЭВМ, управляющей отладкой, или подключая выход 26 устройства к ЭВМ через дополнительный регистр, состояние которого ЭВМ анализирует после каждого изменения содержимого второго разряда в регистре 11 управления.

В режиме фиксации обрашения СЦВМ к заданному числу, адресу или команде в регистр 11 управления записывается «Г в 6-й, 4-й или 5-й разряды соответственно, в 3-й разряд записывается «1, а затем «О, чтобы ввести в исходное состояние триггер 19 и подключить регистр 9 через коммутатор 12 к второму входу схемы 8 сравнения. В регистр 9 записывается заданный код. При фиксации числа или команды к первому входу коммутатора 7 подключается выход регистра 1 команд, при фиксации адреса - выход счетчика 5. Разряд, квалифицирующий код в регистре 1 как команду, через элемент И 13 и элемент ИЛИ 15 разрешает прохождение импульса через элемент И 14 и элемент ИЛИ 16 при совпадении кодов на первом и втором входах схемы 8 сравнения. Аналогично при квалификации кода в регистре 1 как числа сигнал через элемент НЕ 32, элемент И 31 и элемент ИЛИ 15 выдает разрешение на элемент И 14.

При фиксации заданного адреса к коммутатору 7 подключается выход счетчика 5 и на элемент ИЛИ 15 подается с четвертого разряда регистра 11 управления постоянное разрешение для прохождения импульса через элемент И 14.

Формула изобретения

Устройство для отладки программ, содержащее регистры первого и второго пере- ходов, два элемента задержки, дешифратор, счетчик команд, схему сравнения и регистр команд, причем вход команды устройства соединен с информационным входом регистра команд, отличающе еся тем.

0

0

что, с целью повышения быстродействия.

в него введены триггер, первый и второй коммутаторы, первый и второй элементы НЕ, счетчик циклов, восе.мь элементов И, четыре элемента ИЛИ, третий элемент задержки и регистр управления, причем вхо5 ды первого, второго переходов и задания режима устройства соединены с информационными входами соответственно регистров первого, второго переходов и регистра управления, первый выход которого соединен с управляющим входом первого коммутатора, вход признака команд устройства соединен со счетным входом счетчика команд, адресный выход регистра команд соединен с информационным входом счетчика команд и первым информационным входом счетчи5 ка команд, выход кода команды регистра команд соединен с дешифратором, выходы которого соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с первым входом первого элемента И, выход идентификатора команды ре0 гистра команд соединен с первым входом второго элемента И, с вторым входом первого элемента И и через первый элемент НЕ с вторым входом третьего элемента И, выход первого элемента И соединен с входом обнуления счетчика команд и через первый

5 элемент задержки - с входом записи счетчика команд, выход которого соединен с вторым информационным входом первого коммутатора, выход первого коммутатора соединен с входом первого сравниваемого числа

„ схемы сравнения, выход равенства которой соединен с первым входом второго элемента ИЛИ, выходы регистров первого и второго переходов соединены соответственно с первым и вторым информационными входами второго коммутатора, выход кото5 рого соединен с входом второго сравниваемого числа схемы сравнения, второй выход регистра управления соединен с вторым входом второго элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И и через последовательно сое0 диненные второй элемент задержки и второй элемент НЕ с вторым входом четвертого элемента И, выход которого соединен с первыми входами пятого и шестого элементов И, третий выход регистра управления соединен с вторы.м входом шестого

элемента И, нулевым входом триггера и первым входом седьмого элемента И, четвертый, пятый и шестой выходы регистра управления соединены соответственно с первым входом третьего элемента, вторыми входами второго и третьего элементов И, выходы которых соединены соответственно с вторым и третьими входами третьего элемента ИЛИ, выход которого соединен с вторым входом пятого элемента И, выход пятого элемента И соединен с первым входом четвертого элемента ИЛИ, выход которого является сигналом прерывания устройства, выход шестого элемента И соединен с первым входом восьмого элемента И и счетным входом триггера, единичный и нулевой выхо

ды которого соединены соответственно с управляющим входом второго коммутатора и через третий элемент задержки - с вторым входом восьмого элемента И, выход восьмого элемента И и вход задания количества циклов устройства соединены соответственно со счетным входом счетчика циклов и информационным входом счтчика циклов, выход переполнения которого соединен с вторым входом седьмого элемента И, выход которого соединен с вторым входом четвертого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для отладки программ | 1988 |

|

SU1583744A1 |

| Устройство для отладки программ | 1985 |

|

SU1280636A1 |

| Устройство для отладки программ | 1982 |

|

SU1083194A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Устройство для отладки программ | 1989 |

|

SU1689955A1 |

| Устройство для отладки программ | 1983 |

|

SU1104521A1 |

| Устройство для отладки программ | 1989 |

|

SU1674135A1 |

| Устройство для отладки программ | 1985 |

|

SU1251087A1 |

Изобретение относится к в 1числитель- ной технике и может быть использовано для отладки в реальном масштабе времени программ специализированных вычислительных машин. Целью изобретения является сокращение времени отладки программ. Сущность изобретения заключается в использовании сигнала с выхода схемы сравнения для управления поочередным подключением регистров к ее входам, в которых записаны начальный и конечный адреса заданного программного блока для их сравнения с текущими адресами в реальном времени решения задачи и для формирования сигналов обращения к определенному программному блоку. Устройство содержит регистры 1, 9, 10 и 11, дешифратор 2, элементы ИЛИ 3, 15, 16 и 27, элементы И 4, 13, 14, 17, 18, 21, 30 и 31, счетчики 5 и 22, элементы задержки 6, 20 и 28, коммутаторы 7 и 12, схему 8 сравнения, триггер 19 и элементы НЕ 29 и 32. 1 ил. (Л со ot со го го

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки программ | 1974 |

|

SU598077A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1986-04-08—Подача