(54) ПРЕОБРАЗОВАТЕЛЬ КОДОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов (его варианты) | 1980 |

|

SU1005307A1 |

| Преобразователь единичного кода | 1970 |

|

SU1354422A1 |

| Матричное устройство для вычисления тригонометрических функций | 1984 |

|

SU1226448A1 |

| Матричное вычислительное устройство | 1979 |

|

SU809173A1 |

| Устройство для считывания изображений | 1986 |

|

SU1429142A1 |

| Матричное вычислительное устройство | 1979 |

|

SU809174A1 |

| Преобразователь кодов | 1977 |

|

SU779998A1 |

| Преобразователь двоичного кода в уплотненный код | 1988 |

|

SU1562975A1 |

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

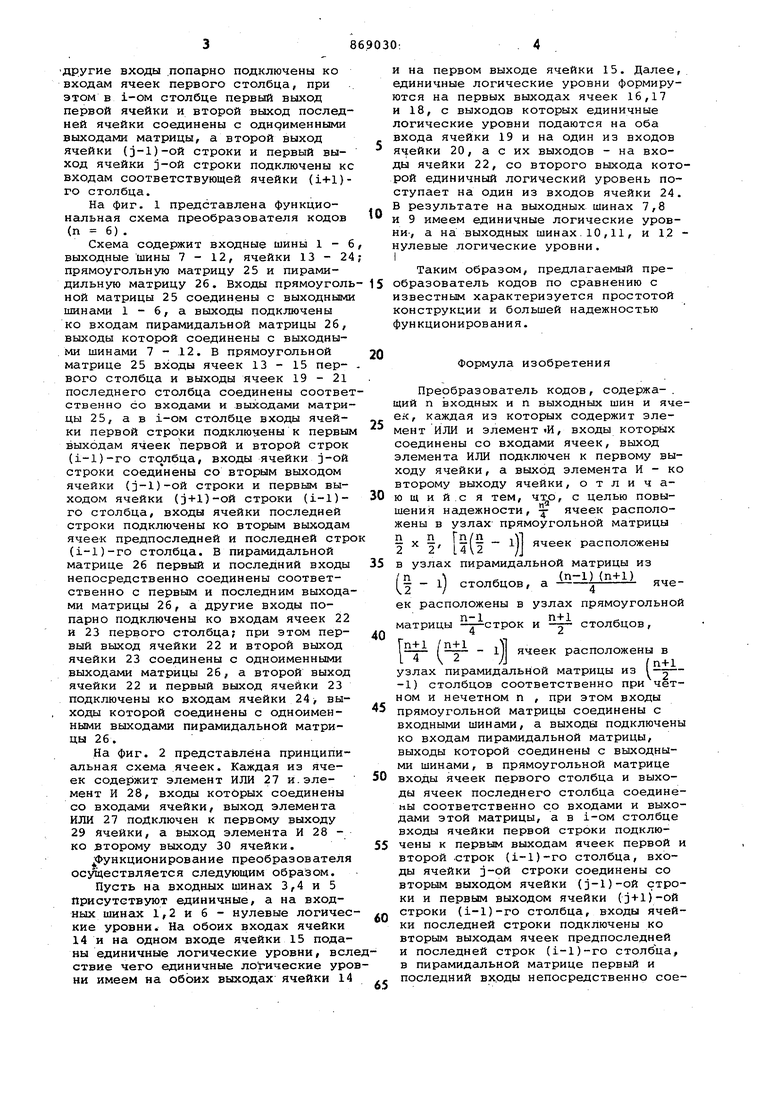

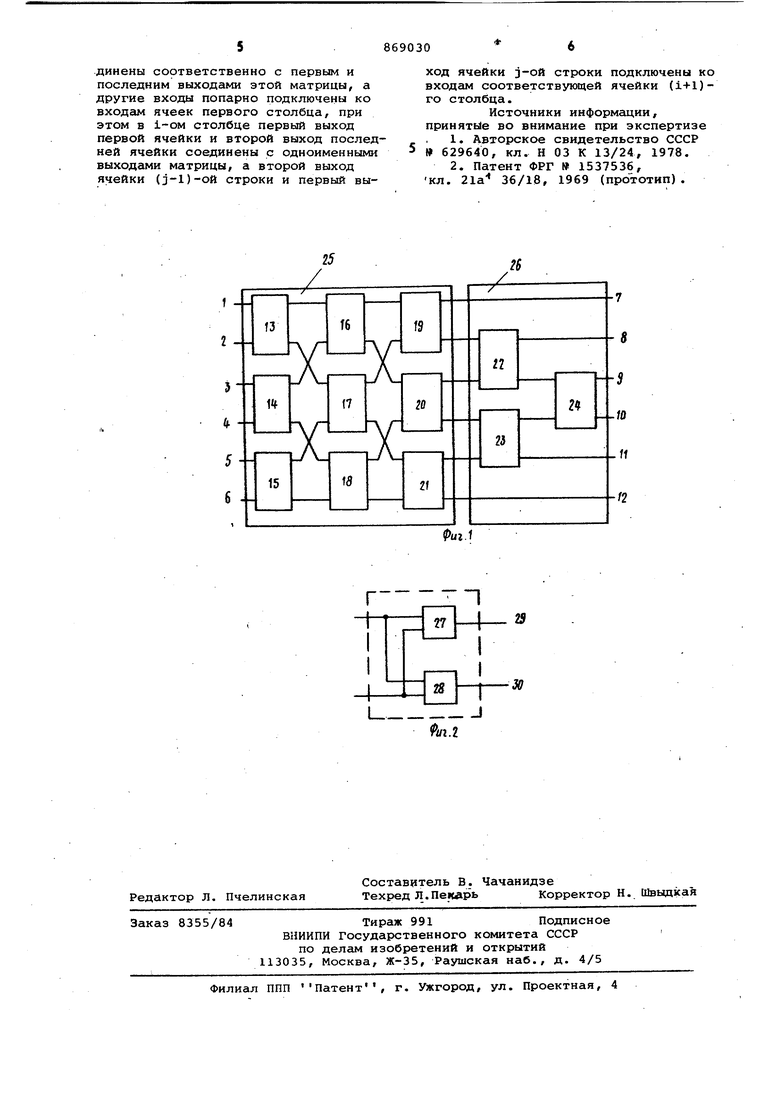

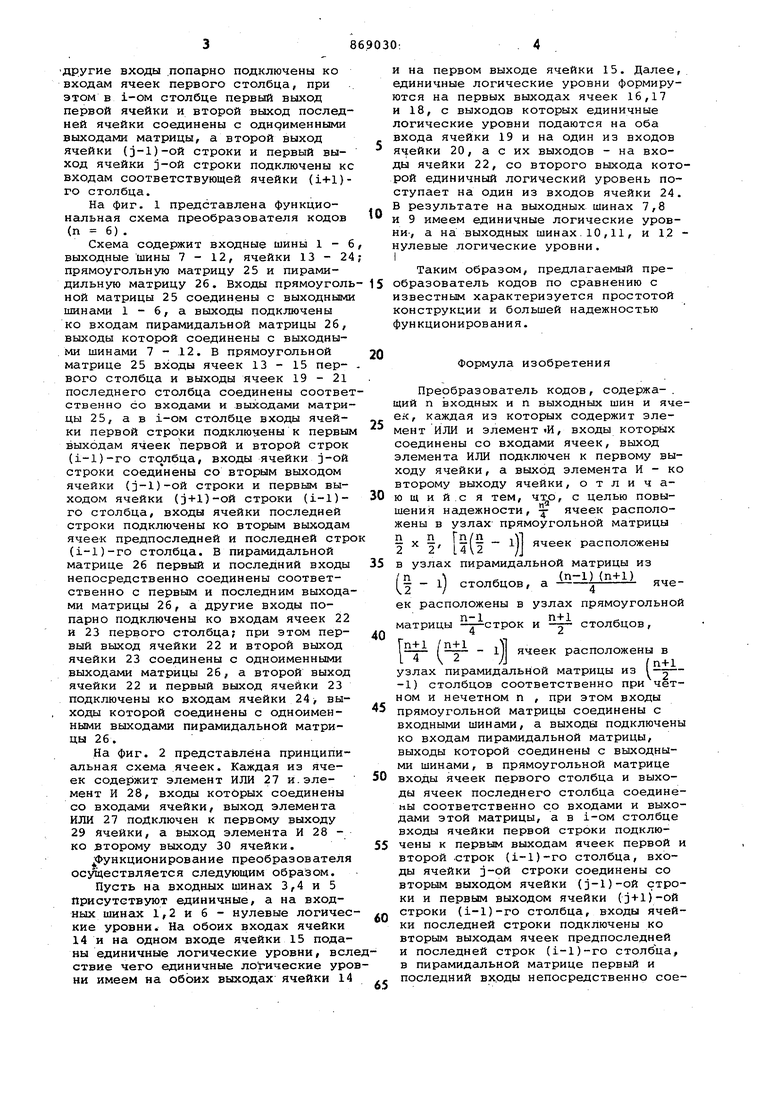

Изобретение относится к автоматике и вычислительной технике. Известны преобразователи кодов, содержащие п входных и п выходных шин и однотипных ячеек на элементах ИЛИ и И 1. Наиболее близок к предлагаемому преобразователь кодов, содержащий п входных и п выходных шин и ячеек, каждая из которых содержит элемент ИЛИ и элемент И, входы которых соеди нены со входами ячейки, выход элемента ИЛИ подключен к первому выходу ячейки, а выход элемента И - к второму выходу ячейки 2. Недостаток известных устройств низкая надежность функционирования. Цель изобретения - повышение надежности преобразования кодов. Указанная цель достигается за сч того, что в преобразователе кодов ячеек расположены в узлах прямоп п Гп / п .V угольной матрицы 2 2 1 4 i I /J ячеек расположены в узлах пирамидгш ной матрицы из (- - i столбцов, а (п-1) (n+lj ggj расположены в узла прямоугольной матрицы из п+1 Гп-И fn+i fl и -j- столбцов, I-T;(2 Ч расположены в узлах пирамидальной матрицы из (Ц- - l столбцов соответственно при четном и нечетном П|При этом входы прямоугольной матрицы соединены с входными шинг1ми, а выходы подключены ко входс1М пирамидальной матрицы, выходы которой соединены с выходными шинами, в прямоугольной матрице входы ячеек первого столбца и выходы ячеек последнего столбца соединены соответственно со входами этой матрицы, а в i-ом столбце входы ячейки первой строки подключены к первым выходам ячеек первой и второй строк (i-l)-ro столбца, входы ячейки j-ой строки соединены со вторым выходом ячейки (j-l)-oй строки и первым выходом ячейки (j+l)-ofl строки (1-1)-го столбца, входы ячейки последней строки подключены ко вторым выходам ячеек предпоследней и последней .строк (1-1)-го столбца, в пирамидальной матрице первый и последний входы непосредственно соединены соответственно с первым и .последним выходами этой матрицы,,а другие входы попарно подключены ко входам ячеек первого столбца, при этом в i-OM столбце первый выход первой ячейки и второй выход последней ячейки соединены с однрименными выходами матрицы, а второй выход ячейки (j-l)-oй строки и первый выход ячейки j-ой строки подключены ко входам соответствующей ячейки (i+1)го столбца. На фиг, 1 представлена функциональная схема преобразователя кодов (п 6) , Схема содержит входные шины i выходные шины 7 - 12, ячейки 13 - 2 прямоугольную матрицу 25 и пирамидильную матрицу 26. Входы прямоуголь ной матрицы 25 соединены с выходными шинами 1 - 6, а выходы подключены ко входам пирамидальной матрицы 26, выходы которой соединены с выходными шинами 7-12. В прямоугольной матрице 25 входы ячеек 13 - 15 первого столбца и выходы ячеек 19 - 21 последнего столбца соединены соотве ственно со входами и выходами матри цы 25, а в i-OM столбце входы ячейки первой строки подключены к первым выходам ячеек первой и второй строк (i-l)-ro столбца, входы ячейки j-ой строки соединены со вторым выходом ячейки (j-l)-oй строки и первым выходом ячейки (j+l)-oй строки (i-1)го столбца, входы ячейки последней строки подключены ко вторым выходам ячеек предпоследней и последней стр (i-l)-ro столбца. В пирамидальной матрице 26 первый и последний входы непосредственно соединены соответственно с первым и последним выхода ми матрицы 26, а другие входы попарно подключены ко входам ячеек 22 и 23 первого столбца при этом первый выход ячейки 22 и второй выход ячейки 23 соединены с одноименными выходами матрицы 26, а второй выход ячейки 22 и первый выход ячейки 23 подключены ко входам ячейки 24 выходы которой соединены с одноименными выходами пирамидальной матрицы 26. На фиг. 2 представлена принципиальная схема ячеек. Каждая из ячеек содержит элемент ИЛИ 27 и.элемент И 28, входы которых соединены со входами ячейки, выход элемента ИЛИ 27 подключен к первому выходу 29 ячейки, а выход элемента И 28 ко второму выходу 30 ячейки. .Функционирование преобразователя осуществляется следующим образом. Пусть на входных шинах 3,4 и 5 присутствуют единичные, а на входных шинах 1,2 и 6 - нулевые логичес кие уровни. На обоих входах ячейки 14 и на одном входе ячейки 15 поданы единичные логические уровни, всл ствие чего единичные ло1гические уро ни имеем на обоих выходах ячейки 14 и на первом выходе ячейки 15. Далее, единичные логические уровни формируются на первых выходах ячеек 16,17 и 18, с выходов которых единичные логические уровни подаются на оба входа ячейки 19 и на один из входов ячейки 20, а с их выходов - на входы ячейки 22, со второго выхода которой единичный логический уровень поступает на один из входов ячейки 24. В результате на выходных шинах 7,8 и 9 имеем единичные логические уровни-, а на выходных шинах.10,11, и 12 нулевые логические уровни. I Таким образом, предлагаемый преобразователь кодов по сравнению с известным характеризуется простотой конструкции и большей надежностью функционирования. Формула изобретения Преобразователь кодов, содержа-, щий п входных и п выходных шин и ячеек, каждая из которых содержит элемент ИЛИ и элемент И, входы которых соединены со входами ячеек, выход элемента ИЛИ подключен к первому выходу ячейки, а выход элемента И - ко второму выходу ячейки, о т л и ч аю щ и и с я тем, , с целью повышения надежности, ячеек расположены в узлах прямоугольной матрицы X , z(§ расположены в узлах пирамидальной матрицы из (п-1)(п+1) §-) столбцов, а 4 ек расположены в узлах прямоугольной столбцов, строк и матрицы Гп+1 /п+1 L 4 2 ,j , , ячеек расположены в узлах пирамидальной матрицы из 1-2- -1) столбцов соответственно при четном и нечетном п , при этом входы прямоугольной матрицы соединены с входными шинами, а выхода подключены ко входам пирамидальной матрицы, выходы которюй соединены с выходными шинами, в прямоугольной матрице входы ячеек первого столбца и выходы ячеек последнего столбца соединены соответственно со входами и выходами этой матрицы, а в i-ом столбце входы ячейки первой строки подключены к первым выходам ячеек первой и второй .строк (i-l)-ro столбца, входы ячейки j-ой строки соединены со вторым выходом ячейки (j-l)-oй строки и первым выходом ячейки (j+l)-oй строки (i-l)-ro столбца, входы ячейки последней строки подключены ко вторым выходам ячеек предпоследней и последней строк (i-l)-ro столбца, в пирамидальной матрице первый и последний входы непосредственно соединены соответственно с первым и последним выходами этой матрицы, а другие входы попарно подключены ко входам ячеек первого столбца, при этом Б 1-ом столбце первый выход первой ячейки и второй выход последней ячейки соединены с одноименными выходами матрицы, а второй выход ячейки (j-l)-oй строки и первый вы25

ход ячейки j-ой строки подключены ко входам соответствующей ячейки (i+1)го столбца.

Источники информации, принятые во внимание при экспертизе

КЛ. 21а 36/18, 1969 (прототип) .

26

/

Авторы

Даты

1981-09-30—Публикация

1980-01-24—Подача