(54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство для тактовой синхронизации и регенерации дискретных сигналов | 1975 |

|

SU536610A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1059689A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Устройство для тактовой синхронизации с регенерацией дискретных сигналов | 1976 |

|

SU594595A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для синхронизации цифровых систем управления тиристорными выпрямителями | 1981 |

|

SU989741A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Устройство дискретной фазовой синхронизации | 1978 |

|

SU748894A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

1

Изйбретение относится к технике связи и.может использоваться в аппаратуре tiep едачи данных,

Известно устройство тактовой синхронизации, содержащее последов тельно соединенные задакяций генератор, блок управления, делитель частоты, фазовый дискриминатор и блок усреднений, выходы которого подсоединены к соответствующим входам блока управления ГП.

В описанном устройстве перерыв приема дискретных сигналов, например, по -причине фединга или воздействия помех на время 17 л ж -Т , вызывает нарушение синхронизма и как следствие нарушение циклового фазирования (&f разность частот опорных генераторов приемного и передающего устройств, f - номинал частоты задающих генераторов, Т - длительность элементарной посылки). Для восстановления приема информации по истечении перерыва необходим прием фазирующей комбинации.

Цель изобретения - повышение помехоустойчивости.

Поставленная цель достигается тем, что в устройство тактовой синхронизации, содержащее последовательно соединенные задающий генератор, блок управления, делитель частоты, фазовый дискриминатор и блок усреднения, выходы которого подсоединены к соответствующим входам блока управления, введены последовательносоединенные дополнительньШ делитель частоты, блок задержки, реверсивный счетчик, объединенньй по входу с входом адресного счетчика, блок сравнения и блок памяти, к другому входу которого под- ч ключен другой выход блока задержки, а к соответствующим входам подключены Ш11ХОДЫ адресного счетчика, выходы блока памяти подключены к другим входам блока усреднения, к дополнительному входу которого подсоединен выход дополнительного делителя частоты.

вход которого подключен к входу фазового дискриминатора.

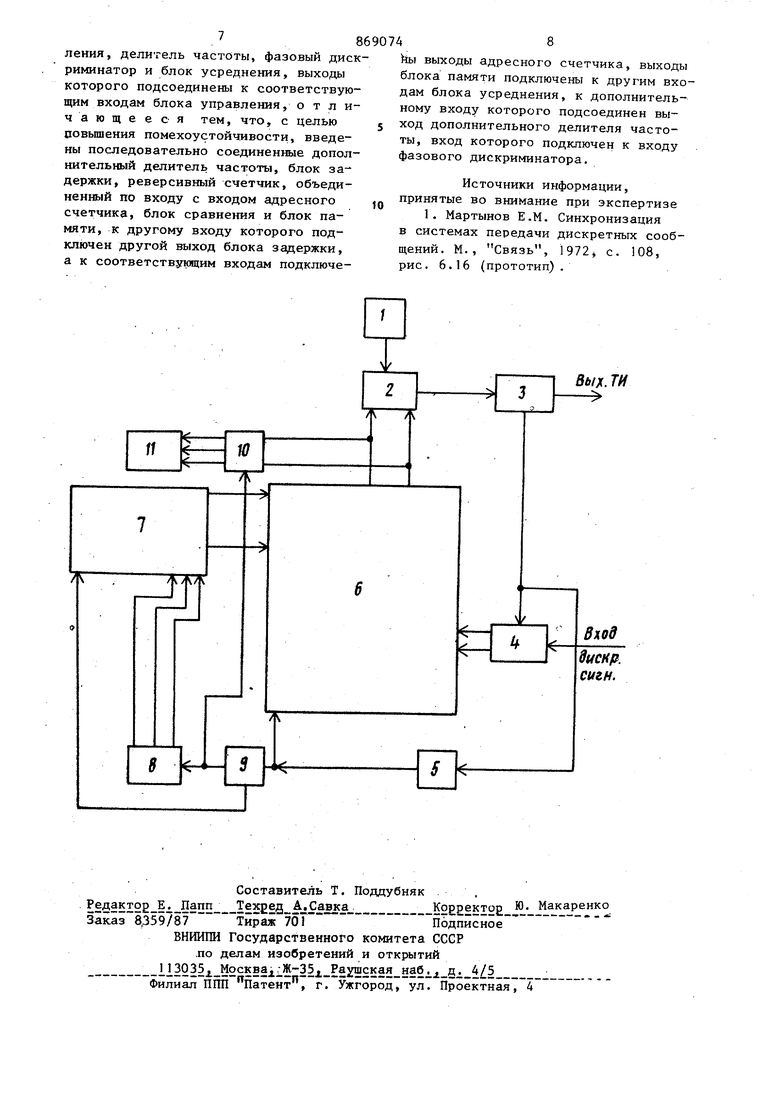

На чертеже представлена структурноэлектрическая схема устройства.

Устройство тактовой синхронизации содержит задающий генератор 1, блок 2 управления, делитель 3 частоты, фазовый дискриминатор 4, дополнительный делитель 5 частоты, блок 6 усреднения, блок 7 памяти, адресный счетчик 8, блок 9 задержки, реверсивный счетчик 0 и блок 11 сравнения.

Устройство тактовой синхронизации работает следующим образом.

Импульсы задакяцего генератора 1 через блок 2 управления поступают на счетный вход делителя 3 частоты. С выхода делителя 3 частоты импульсы опорного напряжения поступают на один вход фазового дискриминатора 4, на его второй вход поступают принимаемые дискретные сигналы. В зависимости от знака временного рассогласования между импульсами опорного напряжения и фронтами дискретных сигналов фазовым дискриминатором 4 вырабатывается команда на добавление или исключение одного импульса.

Предположим, что фазовым дискриминатором 4 вырабатываются команды на добавление. Эти команды поступают на вход блока 6 усреднения и заполняют его. Одновременно каждая команда добавления устанавливает по установочному входу исходное состояние блока.6 усреднения. После заполнения блока 6 усреднения каждая команда на добавление импульса с его выхода поступает на вход блока 2 управления и суммирующий вход реверсивного счетчика 10. Блок управления вырабатывает дополнительный импульс в последовательность импульсов, поступающих от задающего .генератора 1 на счетный вход делителя 3 частоты. Выработанные фазовым дискриминатором 4 команды на исключение импульсов аналЪгично описанному вьппе через блок 6 усреднения поступают на блок 2 управления и вычитакиций вход реверсивного счетчика 10.

Блок 2 управления исключает из последовательности импульсов, поступающих на счетшзШ вход делителя 3 частоты, один импульс. Каждый исключенный или добавленный импульс в зависимости от знака рассогласования сокращает величину фазового рассогласования между опорным напряжением и фронтами инфЪрмационной последовательности на

где F - скорость перевеличину

nf

дачи, п - коэффициент деления делитгля. 3 частоты.

Реверсивный счетчик 10 считает команды добавления, поступащие на его суммирукнций вход и команды исключения, поступающие на его вычитающий вход. Емкость реверсивного счетчика определяется действуняцей нестационарностью коррекций, которая может быть вызвана краевыьш искажениями, многолучевостью и другими факторами. Выходы всех разрядов реверсивного счетчика 10 соединены со входами блока 1 сравнения, выходы которой соединены с информационными входами блка 7 памяти. Емкость блока 7 памяти определяет, с какой точностью подлежит компенсации разность приемной и передающей опорных частот. Если реверсивный счетчик 10 насчитываем болше команд на добавление, чем на исключение, на выходе блока 11 сравнения вырабатывается потенциал записи 1 и О в блок 7 памяти. Если реверсивный счетчик 10 насчитывает болше команд на исключение, чем на добавление, на выходе блотса 11 сравнения вырабатывается потенциал записи О и 1 в блок 7 памяти. Если реверсивный счетчик 10 находится в нулевом состоянии, на обоих выходах блока 11 сравнения вырабатываются потенциалы логического О. Указанны потен1щаль1 поступают на информационные входы блока памяти.

Импульсы опорной частоты с делителя 3 частоты поступают также на , счетный вход дополнительного делителя 5 частоты, коэффициент деления ковыбирается

по соотнощению:

К

где К - коэффициент деления дополнительного делителя 5;

if максимально возможная разность частот передающего и приемного опорных генераторов;

f номинальная частота опорных генераторов; п - коэффициент деления делителя

частоты 3.

По своей физической су1дности коэффициент К определяет, на сколько тактов приема информации должен вырабатываться один импульс коррекции частоты при максимальной разности частот передающего и приемного опорных генераторов. Сигнал с выхода дополнительного д лителя частоты 5 поступает на вход блока усреднения 6 и разрешает прохождение через блок 7 памяти запомненной усредненной команды коррекции Применение блока 7 памяти позволяет компенсировать рассогласования опорных частот любого знака при величине рассогласования меньшей или равной максимальной. Команда коррекции поступает непосредственно на блок 2 и изменяет на величину шага коррекции фазу следова ния тактовых импульсов. Сигнал с выхода дополнительного д лителя 5 частоты поступает также на блок 9 задержки. Сигнал с первого вы хода блока 9 задержки, спустя время t, поступает на вход управления записью блока 7 памяти. Происходит перезапись в блок 7 памяти усредненного сигнала коррекции. Сигнал со второго выхода блока за держки 9, спустя время t(t-, , поступает, во-первых, на установочньй вхо реверсивного счетчика 10 и устанавли вает егоисходное состояние и, во-вт рых, на счетный вход адресного счетч ка 8 и изменяет на I выбранный адрес Таким образом блок 7 памяти подготав ливается к записи коррекции в следую щий интервал усреднения, а реверсивный с етчик 10 к усреднению следукице коррекции. nocjTie некоторого времени приема дискретных сигналов весь необходиьялй объем коррекции записан в блоке 7 па мяти, а По цепи фазовый дискриминатор 4, блок 6 усреднения, реверсивш 1Й счетчик 10 вносятся исправления запомненных коррекций, вызванные изменением абсолютной разницы частот приемного и передающего опорных генераторов. Наличие корректирующей цепи, сост ящей из блока 7 памяти, блока 6 усреднения, реверсивного счетчика 10 и блока 11 сравнения практически не влияет на время вхождения в синхро1шзм, так как корректирукяцие импульсы данной цепи поступают на блок 2 уяравления не чаще, чем 1/. Таким образом, в период вхождения в синхронизацию, признаком чего является повторяющееся следование одноименных команд из фазового дискриминатора 4, коррекция тактовой частоты производится аналогично известному устройству. Во время приема информации в блок 7 памяти записывается усредненная коррекция. Во время перерыва приема дискретных сигналов, например при нарушении канала связи, признаком чего является поочередное следование от фазового дискриминатора 4 разноименных команд управления, коррекция частоты от фазового дискриминатора 4 прекращается благодаря блоку усреднения. При этом коррекция частоты осуществляется по усредненным за определенный период и запомненным в блоке 7 памяти командам коррекции. Технико-экономическая эффективность устройства состоит в том, что кратковременная нестабильность частоты опорного генератора на 2-4 порядка меньше действующего отклонения частоты от номинала; продолжительность сохранения тактовой синхронизации определяется, в основном, разностью приемной и передающей опорных частот. Кроме того, в устройстве запоминается и после прекращения приема дискретных сигналов продолжается ранее действовавшая усредненная коррекция частоты следования приемных тактовых импульсов, которая компенсирует ранее действовавшую разность приемной и передающей опорных частот. Выше сказанное увеличивает на несколько порядков продолжительность сохранения тактовой синхронизации после прекращения приема дискретных сигналов, вызванных, например, воздействием помех или совмещенных использованием канала для передачи дискретных сигналов и информации в аналоговой форме. Продолжительное сохранение тактовой синхронизации повьшает помехоустойчивость и позволяет не передавать ополнительные сигналы для тактовой синхронизации и циклового фазирования после кратковремениого нарушения приема. Это сокращает время передачи искретных сигналов и повышает эфективность использования канала. Формула изобретения Устройство тактовой синхронизации, одержащее последовательио соединеиые задакжций генератор, блок управления, делитель частоты, фазовый дискриминатор и блок усреднения, выходы которого подсоединены к соответствующим входам блока управления, отличающееся тем, что, с целью оовьпиения помехоустойчивости, введены последовательно соединенные дополнительный делитель частоты, блок за- держки, реверсивный счетчик, объединенный по входу с входом адресного счетчика, блок сравнения и блок памяти, к другому входу которого подключен другой выход блока задержки, а к соответствующим входам подключеkbi выходы адресного счетчика, выходы блока памяти подключены к другим входам блока усреднения, к дополнительному входу которого подсоединен выход дополнительного делителя частоты, вход которого подключен к входу фазового дискриминатора.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-09-30—Публикация

1980-01-21—Подача