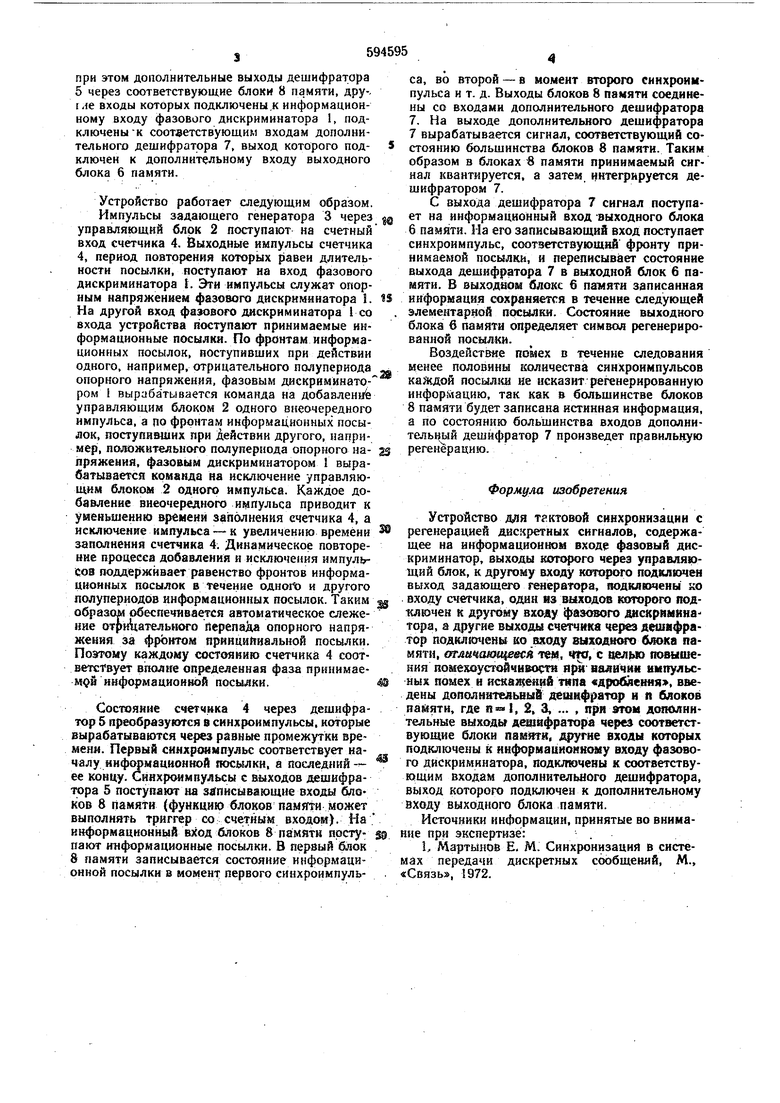

Изобретение относится к радиотехнике и может использоваться в системах радио- и проводной связи, телемеханике, вычислительной технике, в системах автоматического управления. Известно устройство для тактовой синхронизации с регенерацией дискретных сигналов, содержащее на информационном входе фазовый дискриминатор, выходы которого через управляющий блок, к другому входу которого подключен выход задающего генератора, по,дг ключены ко входу счетчика, один из выходов которого подключен к другому входу фазового дискриминатора, а другие выходы счетчика через дешифратор подключены ко входу выходного блока памяти 1. Однако в известном устройстве при искажениях типа «дробления и импульсных помехах возможно искажение регенерации принимаемых сигналов. Цель изобретения - повышение помехоустойчивости при наличии импульсных помех и искажений типа «дробления. Для этого в устройство для тактовой синхронизации с регенерацией дискретных сигналов, содержащее на информационном входе фазовой дискриминатор, выходы которого через управляющий блок, к другому входу которого подключен выход задающего генератора, подключены ко .входу счетчика, один из выходов которого подключен к другому входу фазового дискриминатора, а другие выходы счетчика через дешифратор подключены ко входу выходного блока памяти, введены дополнительный дешифратор и п блоков памяти, где п 1, 2, 3 ... , при это.м дополнительные вы.ходы дешифратора через соответствующие блоки памяти, другие входы которых подключены к информационному входу фазового дискриминатора, подключены к соответствующим входам дополнительного дешифратора, выход которого подключен к дополнительному входу выходного блока памяти. На чертеже приведена структурная электрическая схема предлагаемого устройства. Устройство для тактовой синхронизации с регенерацией дискретных сигналов содержит на информационном входе фазовый дискриминатор 1, выходы которого через управляющий блок 2, к другому входу которого подключен выход задающего генератора 3, подключены ко входу счетчика 4, один из выходов которого подключен к другому входу фазовогодискриминатора 1, а другие выходы счетчика 4 через дещифратор 5 подключены ко входу выходного блока 6 памяти, дополнительный дешифратор 7 и п блоков 8 памяти, где , 2, 3 ... ,

при этом дополнительные выходы дешифратора 5 через соответствующие блоки 8 памяти, дру-ые входы которых подключены.к информационному входу фазового дискриминатора 1, подключены к соответствующим входам дополнительного дешифратора 7, выход которого подключен к дополнительному входу выходного блока 6 памяти.

Устройство работает следующим образом.

Импульсы задающего генератора 3 через управляющий блок 2 поступают на счетный вход счетчика 4. Выходные импульсы счетчика 4, период повторения которых равен длительности посылки, поступают на вход фазового дискриминатора I. Эти импульсы служат опорным напряжением фазового дискриминатора . На другой вход фазового дискриминатора 1 со входа устройства яоступают принимаемые информационные посылки. По фронтам информационных посылок, поступивших при действии одного, например, отрицательного полупериода опорного напряжения, фазовым дискриминатором 1 вырабатывается команда на добавленнЬ управляющим блоком 2 одного внеочередного импульса, а по фронтам информационных посылок, поступивших при Действии другого, например, положительного полупернода опорного напряжения, фазовым дискриминатором 1 вырабатывается команда на исключение управляющим блоком 2 одного импульса. Каждое добавление внеочередного импульса приводит к уменьшению времени заполнения счетчика 4, а исключемие импульса - к увеличению времени заполнення счетчика 4. Динамическое повторение процесса добавления и исключения импул гCOS поддерживает равенство фронтов информационных посылок в течение одиоШ и другого лолупериодов информационных посылок. Таким образец обеспечивается автоматическое слежение отрицательного Перепада опорного напряжения за фронтом принцийнальной посылки. Поэтому каждому состоянию счетчика 4 соответствует вполне определенная фаза принимаеtm}& информационной посылки.

Состояние счетчнка 4 через дешифратор 5 преобразуются а синхроимпульсы, ноторые вырабатываются через равные промежутки времени. Первый синхроимпульс соответствует началу имфшмациомной (юсылки, а последний ее концу. €иихроимпульсы с выходов дешифратора 5 поступают на записывающие входы блв ков 8 памяти (функцию блоков памягти может выполнять триггер со счетным входом). На информационный вход блоков 8 памяти прсту пают информационные посылки. В первый блок 8 памяти записывается состояние информационной посылки в момент первого синхроимпульса, во второй - в момент второго синхроимпульса и т. д. Выходы блоков 8 памяти соединены со входами дополнительного дешифратора 7. На выходе дополнительного дешифратора

7вырабатывается сигнал, соответствующий состоянию большинства блоков 8 памяти. Таким

образом в блоках в памяти принимаемый сигнал квантируется, а затем интегрируется дешифратором 7.

С выхода дешифратора 7 сигнал поступает на информационный вход -выходного блока б памяти. Ма его записывающий вход поступает синхроимпульс, соответствующий фронту принимаемой посылки, и переписывает состояние выхода дешифратора 7 в выходной блок 6 памяти. В выходяом блоке 6 памяти записанная

информация сохраняется в течение следующей элементарной шхылкя. Состояние выходного блока в памяти определяет символ регенерированной посылки.

Воздействие помех в течение следования

менее половины количества синхроимпульсов

каждой ПОСЫЛ1Ш не исказит регенерированную информацию, так как в большинстве блоков

8памяти будет записана истинная информация, а по состоянию большинства входов дополиительвый дешифратор 7 произведет правильную

регенерацию..

Формула изобретения

Устро{ ство для тактовой синхронизации с регенерацией дискретных сигиалов, содержащее на информационном входе фазовый дискриминатор, выходы которого через упрааяяющий блок, к другому входу которого подключен выход задающего генератора, водключены ко входу счетчика, один вз шаткой которого подключен к другому входу фазового двскримйнз тора, а другие выходы счетчика через дешифратор подклюг|еяы ко входу 8ыходш го блока памяти, отличаищевс тем, что, с «елмо noKiiiueния помехоустойчивости я{ж иадичик импульсных помех и искажений типа «дробления, введены дополийтельвыЙ дешифратор и п блоков , где ««I, 2, 3, ... , при этой дополиительные выходы дешифратора черед соответствующие блоки павйти, другие входы которых под1и1ючены к информационному входу фазового дискриминатора, подключены к соответствующим входам дополнительного дешифратора, выход которого подключен к дополнительиому входу выходного блока памяти.

Источники информации, принятые во внимание при экспертизе:.

I, Мартынов Б, М. Синхронизация в системах передачи дискретных сообщений, М., «Связь, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тактовой синхронизации и регенерации дискретных сигналов | 1975 |

|

SU536610A1 |

| Устройство для приема дискретной информации | 1983 |

|

SU1111260A1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU886290A1 |

| Регенератор приемника стартстопных телеграфных сигналов | 1976 |

|

SU641671A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU869074A1 |

| Устройство восстановления дискрет-НОй иНфОРМАции | 1979 |

|

SU813807A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU965005A2 |

nri-i

J

I-.

Авторы

Даты

1978-02-25—Публикация

1976-05-10—Подача