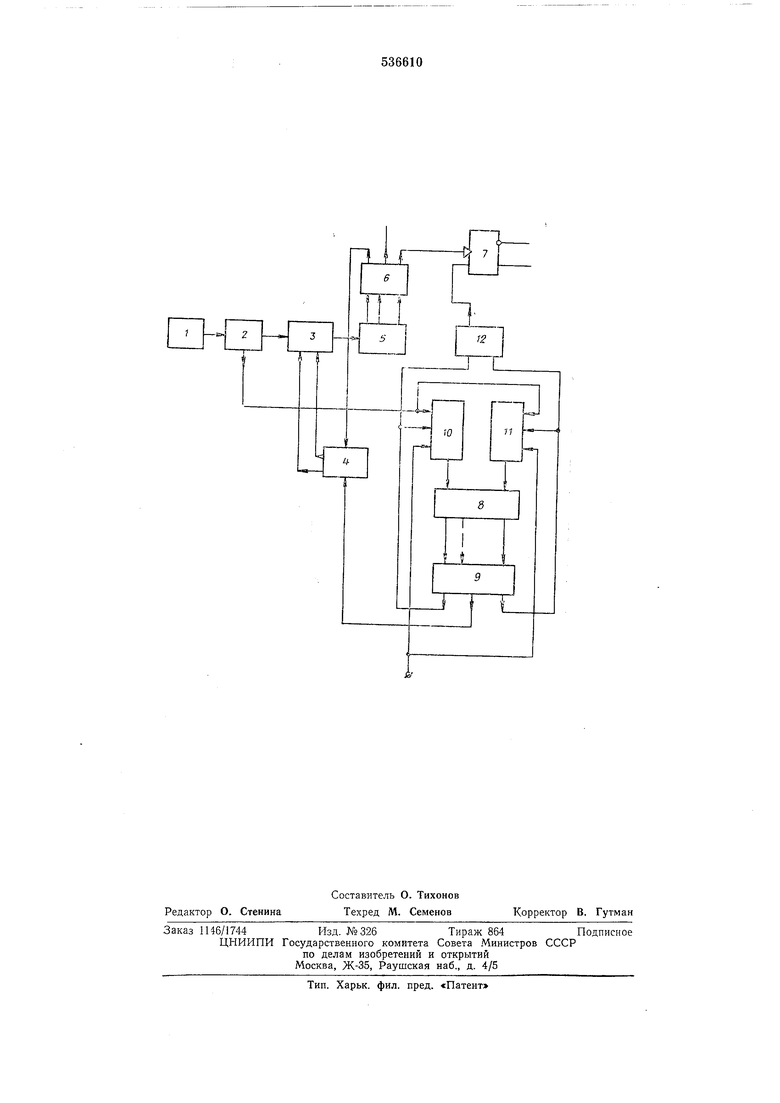

регенерации дискретных сигналов содержит последовательно соединенные задающий генератор /, делитель 2 частоты, управляющий элелчент 3, соединенный с фазовым дискриминатором 4, .счетчик 5, дешифратор 6, выходы которого подключены к соответствующим входам выходного триггера 7 и фазового дискриминатора 4, реверсивный счетчик 8, дополнительный дешифратор 9, иервый 10, второй 11 элементы запрета, управляющий триггер 12, при этом выход делителя 2 частоты подключен через первый 10 и второй 11 элементы Запрета к суммирующе1му и вычитающему входам реверсивного счетчика 8, выходы которого через дополнительиый дешифратор 9 подключены к дополнительному входу фазового дискр-иМИнатора 4, к управляющим входал первого JO и второго // элементов запрета и к установочньгм входам управляющего триггера 12, выход которого подключен к информацнонному входу выходного триггера 7. Устройство для тактовой синхронизации и регенерации дискретных сигналов работа:ет следующим образом. Частота колебаний генератора / через делитель 2 и элемент 3 поступает на вход счетчика 5, выходы которого соединены с дешифратором 6. При заполнении счетчика 5 на выходе дешифратора 6 появляется сигнал, поступающий на вход триггера 7 и считывающий регенерированные ииформациоииые посылки. При заатолнепии счетчика 5 до числа 2 на выходе дешифратора 6 появляется сигнал, поступающий на вход дискриминатора 4. Со входа устройства информационная последовательность поступает на один из входов первого 10 и второго // элементов запрета. Если входная информация соответствует единичному сиМволу, то элемент 11 запрещает вычитание счетчика 8, а элемент 10 разрещает заполнение счетчика 8, который выключается при занолиении сигналом, поступающим с выхода дешифратора 9 и элемента 10. Одновременно сигнал о заполнении счетчика 8 поступает на ВХОД триггера 12 и переводит его в состояние, определяющее символ регенерированной посылки на триггере 7. При заполнении счетчи:ка 8 до Числа (2 - емкость счетчика) на выходе дешифратора 9 появляется сигнал, поступающий на вход диокримииатора 4. Если входная информация соответствует нулевому символу, то заполнение счетчика 8 через элемент .10 прекращается и начинается через элемент // отсчет в обратном направлении. При заполнении счетчика 8 до числа «О на выходе дешифратора 9 появляется сигнал, воздействующий на элемент 11, запрещающий дальнейшее цоступление имнульсов на вход счетчика 8 и устанавливающий триггер 12 в другое положение. В зависимости от зна1ка .временного рассогласования сигналов на выходе дешифратора 6 и дещифратора 9 фазовым дискри минатором 4 вырабатывается команда элементу 3 на добавление или вычитание одного импульса. Если сигнал с выхода дешифратора 6 опережает сигнал на выходе дешифратора 9 менее чем на половину длнтельности элементарной посылки, то дцскриминатором 4 вырабатывается команда на добавление одного за период заполнения счетчика 5 внеочередного имиульса. При этом каждый добавленный импульс приводит к уменьшению величины временного рассогласования между дешифраторами 6 и 9. Если сигнал на выходе дешифратора 9 опережает сигнал, поступающий с выхода дешифратора 6 менее чем на половину периода, то дискриминатором 4 вырабатывается команда иа вычитаиие импульса. При воздействии импульсиых по-мех с искажений типа дроблений искажения символов на входе устройства вызывают переключение направления отсчета счетчика 8. Фронт информационных посылок передается на фазовый дискриминатор 4 после пересчета счетчиком 8 имтульсав. .Поэтому имлульсные помехи и искажепия типа дро-блений (при их длительности меиее времени .пересчета счетчиком 8 И1мтулысов) не |П01Ступают па вход фазового дискриминатора - и не влияют на тактовое фазирование. Формула изобретения Устройство для тактовой 1сиихронизации и регенерации дискретных сигналов, содержащее последовательно соединенные задающий генератор, делитель частоты, управляющий элемент, соединенный с фазовым дискриминатором, счетчик и дешифратор, выходы которого .подключеиы к соответствующим входам выходного триггера и фазового дискриминатора, отличающееся тем, что, с целью уменьшения вероятности нарушения тактовой синхронизации и повышения вероятности неискаженной регенерации принимаемых инqbopмaционных посылок при наличии импульсных помех и искажений тина дроблений, введены реверсивный счетчик, дополнительный дешифратор, объединенные по входу первый и второй элементы запрета и управляющий триггер, лри этом выход делителя частоты подключен через первый и второй элементы запрета к суммирующему и вычитающему входа.м реверсивного счетчика, выходы которого через дополнительный дешифратор подключены к дополнительному входу фазоволо дискриминатора, к управляющему входам первого и второго элементов запрета и к установочным входам управляющего триггера, выход которого подключен к информационному входу выходного триггера. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 321952 М. Кл.2 Н 04 L 7/02, 24.06.70. 2.Мартынов Е. М. Синхронизация в системах передачи дискретных сообщений. М., «Связь, 1972, с. 108 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тактовой синхронизации с регенерацией дискретных сигналов | 1976 |

|

SU594595A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| Регенератор приемника стартстопных телеграфных сигналов | 1976 |

|

SU641671A1 |

| Устройство синхронизации с дискретным управлением | 1978 |

|

SU856028A2 |

| Устройство тактовой синхронизации | 1980 |

|

SU869074A1 |

| Устройство для измерения преобладаний двоичных сигналов | 1985 |

|

SU1246396A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Устройство синхронизации сигналов | 1981 |

|

SU1021005A2 |

Авторы

Даты

1976-11-25—Публикация

1975-04-07—Подача