t

Изобретение относится к вычислительной технике, и может применятьсн для обнаружения ошибок при передаче информации в двоичном коде.

Известны устройства для контроля передач двоичной информации, состоящее из элементов И,ИЛИ и усилительного элемента с парафаэным вьпсодом и устройства, состоящие из регистра, элементов И, ИЛИ и счетного триг-. гера 11.

Недостатком известных устройств является их сложность, Которая возрастает с ростом разрядности контролируемого кода.

Наиболее близким техническим решением к изобретению является устройство для контроля параллельного двоичного кода на четность, содержащее два элемента И, регистр сдвига, триггер со счетным входом, причем инфор- : мационными входами устройства являются паралл&льные входы регистра сдвига, нулевые разрядные выхода которого соединены с входами первого элемента И, выход которого соединен с первым входом втсфого элемента И, с шиной тактовой частоту, а его выход - с входом сдвига регистра сдвига, выход которого соединен со

счетным входом триггера, выход которого является выходом устройства 2.

Недостаточно высокое быстродействие известного устройства определяется тем, что количество сдвигающих импульсов, необходимых для проверки кода нд четность, определяется номером старшего разряда, содержащего логическую .

fO

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для контроля Параллельного двоичного кода на четность, содержгицее элемент И, триггер четности и регистр сдвига, каждый разряд которого содержит триггер,, единичный вход которого является информационным входом устройства,

20 причем выход элемента И соединен со счетным вхсдаом триггера четности, выход которого является выходом устройства, первый вход элемента И соединен с выходом регистра сдвига,

25 а второй вход - с синхронизирующим входом устройства, в Кс1ждый разряд регистра сдвига введены дополнительный элемент И и элемент ИЛИ, единичный выход триггера каждого разряда

30 соединен с первыми входами соответютвунлдего дополнительного элемента и элемента ИЛИ, выход которого соединен со сдвигающим входом триггера последующего разряда регистра, и с вторым входом элемен а ИЛИ последующего разряда, сдвигающий вход триггера старшего разряда соединен со вторым входом элемента ИЛИ данного разряда и с входом сигнала логического О устройства. Выход элемента ИЛИ младшего разряда являеся выходом регистра. Синхронизирующий вход устройства соединен с вторыми входами дополнительных элементов И, выходы которых соединены с нулевыми входами триггеров соответствующих разрядов.

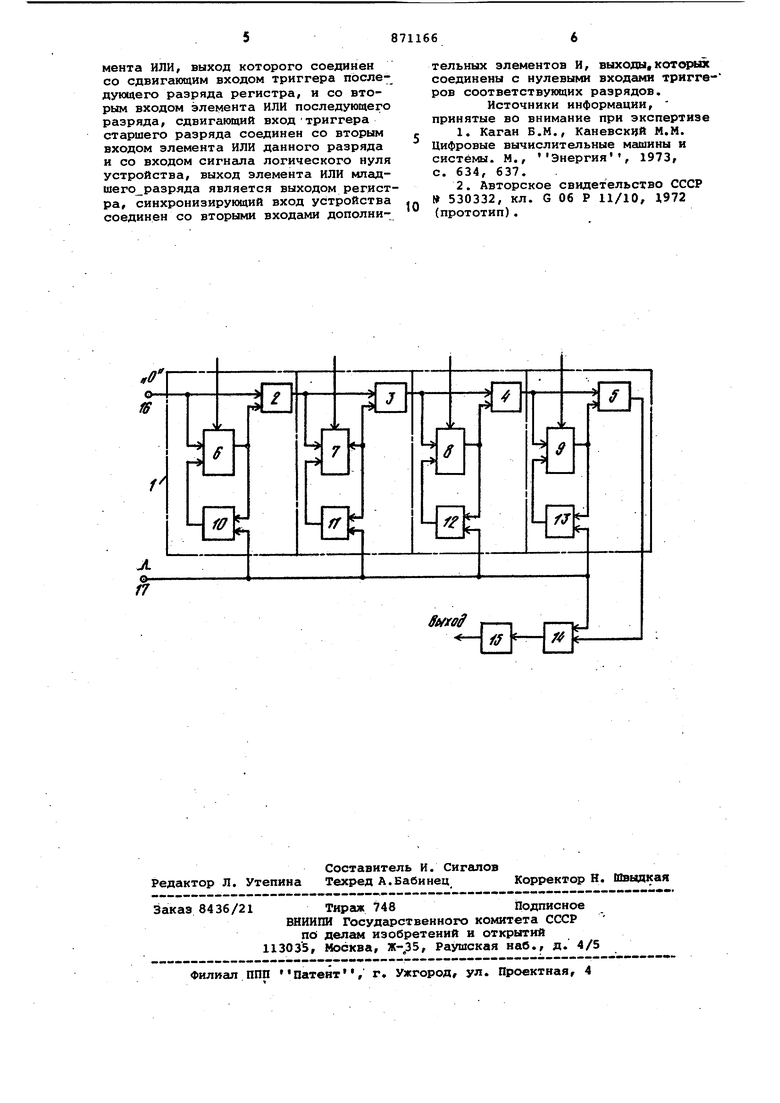

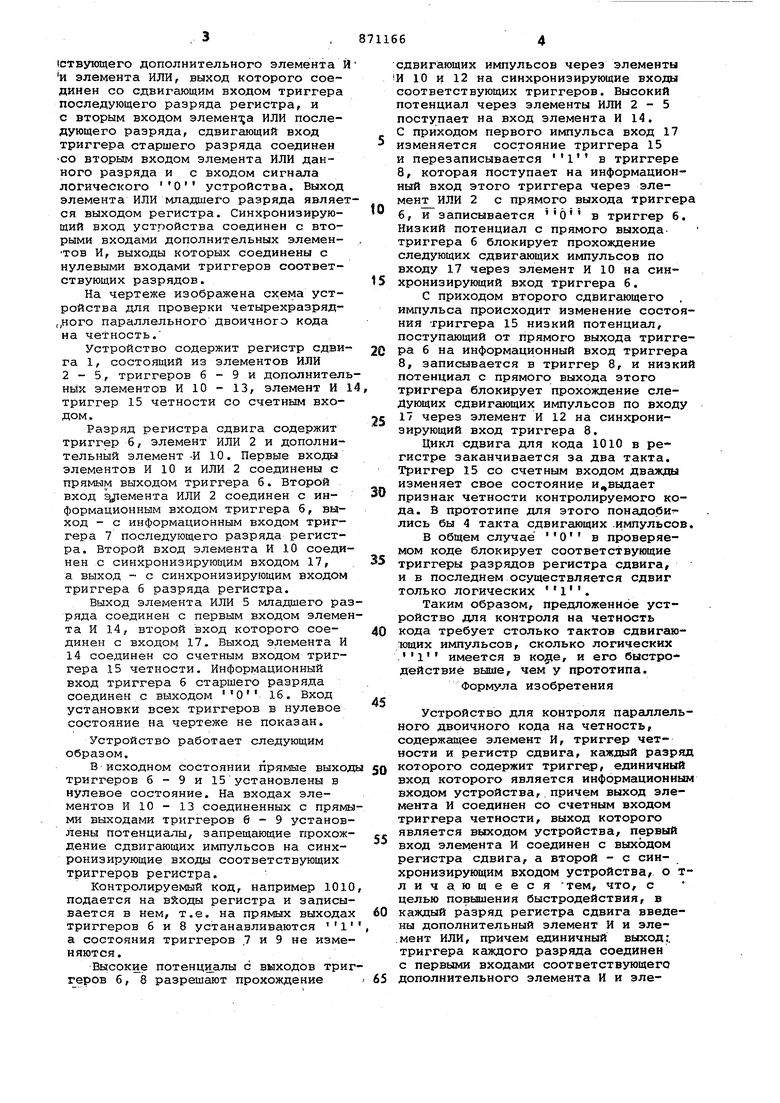

На чертеже изображена схема устройства для проверки четырехразряд,,ного параллельного двоичного кода на четность.

Устройство содержит регистр сдвига 1, состоящий из элементов ИЛИ 2 - 5, триггеров 6 - 9 и дополнителнь1х элементов И 10 - 13, элемент И триггер 15 четности со счетным входом.

Разряд регистра сдвига содержит триггер 6, элемент ИЛИ 2 и дополнительный элемент .И 10. Первые входы элементов И 10 и ИЛИ 2 соединены с прямым выходом триггера б. Второй вход э темента ИЛИ 2 соединен с информационным входом триггера 6, выход - с информационным входом три1- гера 7 последующего разряда регистра. Второй вход элемента И 10 соединен с синхронизирующим входом 17, а выход - с синхронизирующим входом триггера б разряда регистра.

Выход элемента ИЛИ 5 младшего раряда соединен с первым входом элемета И 14, второй вход которого соединен с входом 17. Выход элемента И 14 соединен со счетным входом триггера 15 четности. Информационный вход триггера б старшего разряда

О

16. Вход

соединен с выходом

установки всех триггеров в нулевое состояние на чертеже не показан.

Устройство работает следующим образом.

В-исходном состоянии прямые выходы триггеров б - 9 и 15 установлены в нулевое состояние. На входах элементов И 10 - 13 соединенных с прямыми: выходами триггеров 6-9 установлены потенциалы, запрещающие прохождение сдвигающих импульсов на синхронизирующие входы соответствующих триггеров регистра.

Контролируемый код, например 1010 подается на регистра и записывается в нем, т.е. на прямых выходах триггеров 6 и 8 устанавливаются а состояния триггеров 7 и 9 не изменяются.

Высокие потенциалы с выходов триггеров б, 8 разрешают прохождение

сдвигающих импульсов через элементы iH 10 и 12 на синхронизирующие входы соответствующих триггеров. Высокий потенциал через элементы ИЛИ 2-5 поступает на вход элемента И 14. С приходом первого импульса вход 17 изменяется состояние триггера 15 и перезаписывается i в триггере 8, которая поступает на информационный вход этого триггера через элемент ИЛИ 2 с прямого выхода триггер 6, и записывается 6 в триггер 6. Низкий потенциал с прямого выхода триггера б блокирует прохождение следующих сдвигающих импульсов по входу 17 через элемент И 10 на синхронизирующий вход триггера 6.

С приходом второго сдвигающего импульса происходит изменение состояния триггера 15 низкий потенциал, поступающий от прямого выхода триггера 6 на информационный вход триггера 8, записывается в триггер 8, и низки потенциал с прямого выхода этого триггера блокирует прохождение следующих сдвигающих импульсов по входу 17 через элемент И 12 на синхронизирующий вход триггера 8.

Цикл сдвига для кода 1010 в регистре заканчивается за два такта. Триггер 15 со счетным входом дважды изменяет свое состояние и выдает признак четности контролируемого кода. В прототипе для этого понадоби лись бы 4 такта сдвигающих .импульсов

В общем случае О в проверяемом коде блокирует соответствующие триггеры разрядов регистра сдвига, и в последнем осуществляется сдвиг только логических .

Таким образом, предложенное устройство для контроля на четность кода требует столько тактов сдвигаюющих импульсов, сколько логических имеется в , и его быстродействие выше, чему прототипа. Формула изобретения

Устройство для контроля параллельного двоичного кода на четность, содержащее элемент И, триггер четности и регистр сдвига, каждый разряд которого содержит триггерг единичный вход которого является информационным входом устройства, причем выход элемента И соединен со счетным входом триггера четности, выход которого является выходом устройства, первый вход элемента И соединен с выходом регистра сдвига, а второй - с синхронизирующим входом устройства, о тличающееся тем, что, с целью повышения быстродействия, в каждый разряд регистра сдвига введены дополнительный элемент И и элемент ИЛИ, причем единичный выход;, триггера каждого разряда соединен с первыми входами соответствующего дополнительного элемента И и элемента ИЛИ, выход которого соединен со сдвигающим входом триггера последующего разряда регистра, и со вторым входом элемента ИЛИ последующего разряда, сдвигающий входтриггера старшего разряда соединен со вторым входом элемента ИЛИ данного разряда и со входом сигнала логического нуля устройства, выход элемента ИЛИ младшего разряда является выходом регистра, синхронизирующий вход устройства соединен со вторыми входами дополнительных элементов И, ъыхощл,которых соединены с нулевыми входами триггеров соответствующих разрядов.

Источники информации, принятые во внимание при экспертизе

1.Каган Б.М., Каневский М.М. Цифровые вычислительные машины и системы. М., Энергия, 1973, с. 634, 637.

2.Авторское свидетельство СССР 530332, кл. G 06 Р 11/10, 1,972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU997038A1 |

| Устройство для формирования контрольного кода по четности | 1980 |

|

SU934477A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1023334A2 |

| Регистр сдвига | 1980 |

|

SU875462A1 |

| Устройство для определения количества единиц в двоичном числе | 1982 |

|

SU1023335A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Устройство для контроля двоичного кода на нечетность | 1981 |

|

SU1012261A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1084800A2 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1985 |

|

SU1291989A1 |

| Электропривод постоянного тока | 1983 |

|

SU1100697A1 |

Авторы

Даты

1981-10-07—Публикация

1980-01-07—Подача