(54) РЕГИСТР СДВИГА

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1979 |

|

SU849303A1 |

| Регистр сдвига | 1982 |

|

SU1111207A1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| Запоминающее устройство | 1980 |

|

SU868835A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU822292A1 |

| ЦИФРОВОЙ КОРРЕЛЯТОР С ЗАПОМИНАЮЩИМ УСТРОЙСТВОМ НА МАГНИТНОМ БАРАБАНЕ | 1966 |

|

SU182414A1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА С ДВУСЛОЙНОЙ ПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1998 |

|

RU2134448C1 |

| Устройство для считывания и обработки изображений | 1988 |

|

SU1513486A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| Шифратор | 1985 |

|

SU1298802A2 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах для контроля па раллельного двоичного кода на четность или в цифровых корреляторах для обнаружения кодового слова. Известен регистр сдвига, каждый разряд которого содержит триггер и элементы И и ИЛИ fl Наиболееблизким из известных по технической сущности является регист каждый разряд которого содержит триг гер с асинхронным информационным и синхронизирующим входом, причем информационный вхоД триггера последующего разряда соединен .с пряквлм выходом триггера предыдущего разряда, а информация вводится о все разряды регистра параллель но терез асинхронные входы триггеров разрядов, синхронизирующие входы все триггеров соединены с шиной сдвигающих импульсов. С приходом каждого сдвигающего им пульса происходит сдвиг записанного в регистр кода- на один разряд 2 . Недостатком известных регистров является невозможность сдвига одноименных битов например логических 1) записанного кода, что необходимо в ряде устройств, основанных на подсчете числа логических 1 кода. Использование известного регистра в этих устройствах уменьшает быстродействие, так как число тактов сдвигающих импульсов, необходимых для сдвига всего записанного кода, больше числа логических 1, содержащихся в этом коде. Цель изобретения - расширение области применения. Поставленная цель достигается тем, что в регистр сдвига, содержащий ячейки памяти, каждая из которых из триггера, первый вход которого соединен с информационным входом регистра сдвига, шину сдвига и шину управления, в каждую его ячейку памяти введены элементы И, ИЛИ и элемент НЕ, вход которого соединен с шиной управления и с первым входом первого элемента И, второй вход первого элемента И подключен ко второму входу триггера данной ячейки памяти и к выходу первого элемента ИЛИ предыдущей ячейки памяти, третий вход первого элемента И каждой ячейки памяти соединен с первым выходом триггера данной

ячейки памяти, ,йторой выход триггера которой подключен к первьм входам первого и второго элементов ИЛИ данной ячейки памяти, второй вход первого элемента ИЛИ каждой ячейки памяти соединен с выходом первого элемента И данной ячейки памяти, выход элемента НЕ каждой ячейки памяти соединен со вторым входом второго элемента ИЛИ, выход которого соединен с первь1М входом второго элемента И, второй BxoJi второго элемента И подключен к шине сдвига, выход второго элемента И соединен с третьим входом триггера.

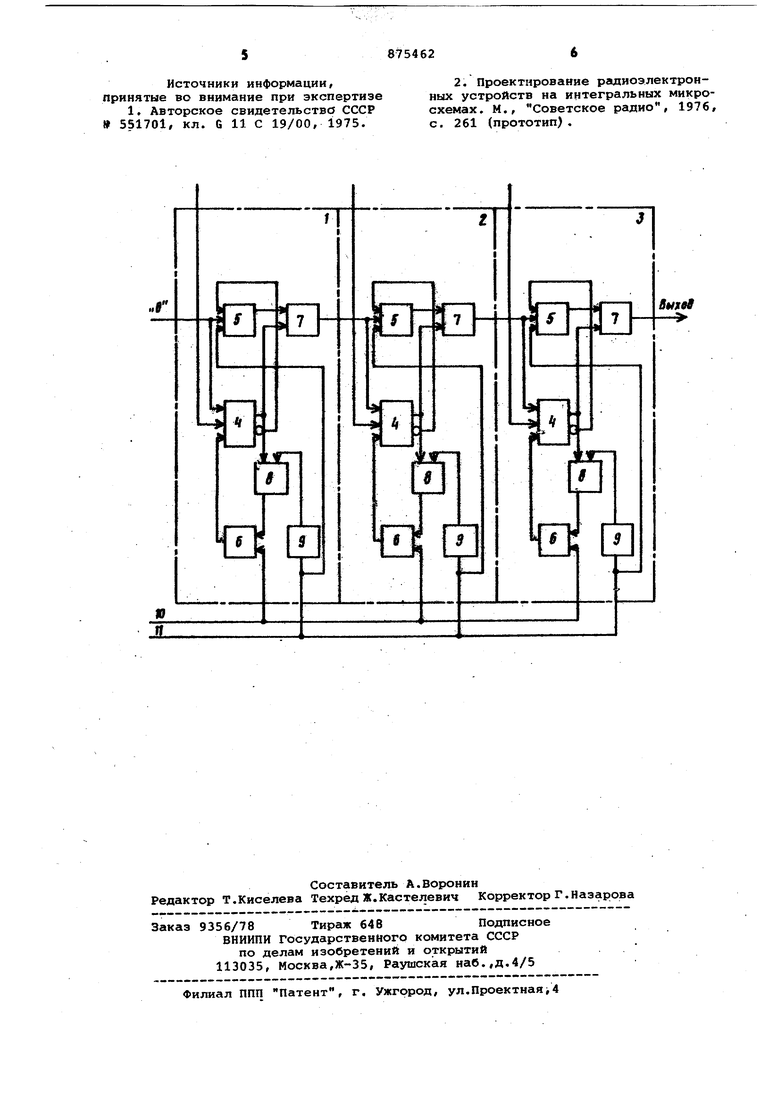

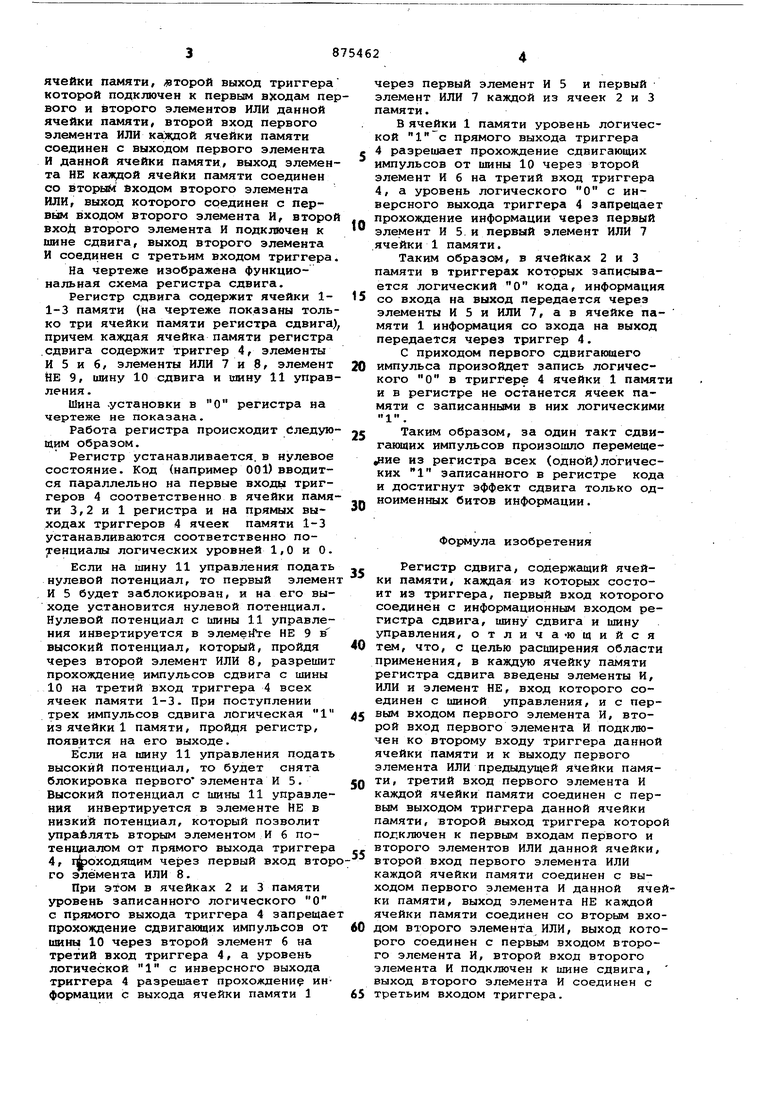

На чертеже изображена функциональная схема регистра сдвига.

Регистр сдвига содержит ячейки 11-3 памяти (на чертеже показаны только три ячейки памяти регистра сдвига) причем каждая ячейка памяти регистра .сдвига содержит триггер 4, элементы И 5 и б, элементы ИЛИ 7 и 8, элемент НЕ 9, шину 10 сдвига и шину 11 управления .

Шина -установки в О регистра на чертеже не показана.

Работа регистра происходит Следующим обраэом.

Регистр устанавливается, в нулевое состояние. Код (например 001) вводится параллельно на первые входы триггеров 4 соответственно в ячейки пзмяти 3,2 и 1 регистра и на прямых выходах триггеров 4 ячеек памяти 1-3 устанавливаются соответственно потенциалы логических уровней 1,0 и О.

Если на шину 11 управления подать нулевой потенциал, то первый элемен И 5 будет заблокирован, и на его выходе установится нулевой потенциал. Нулевой потенциал с шины 11 управления инвертируется в элеме1Й:е НЕ 9 в высокий потенциал, который, пройдя через второй элемент ИЛИ 8, разрешит Прохождение импульсов сдвига с шины 10 на третий вход триггера 4 всех ячеек памяти 1-3. При поступлении трех импульсов сдвига логическая 1 из ячейки 1 памяти, пройдя регистр, появится на его выходе.

Если на шину 11 управления подать высокий потенциал, то будет снята блокировка первого элемента И 5. Высокий потенциал с шины 11 управления инвертируется в элементе НЕ в низкий потенциал, который позволит упраблять вторым элементом И 6 потенцяалом от прямого выхода триггера 4, проходящим через первый вход вторго элемента ИЛИ В,

При этом в ячейках 2 и 3 памяти уровень записанного логического О с прямого выхода триггера 4 запрещае прохождение сдвигающих импульсов от шины 10 через второй элемент 6 на третий вход триггера 4, а уровень логической 1 с инверсного выхода триггера 4 разрешает прохождение информации с выхода ячейки памяти 1

через первый элемент И 5 и первый элемент ИЛИ 7 каждой из ячеек 2 и 3 памяти.

В ячейки 1 памяти уровень логической 1 с прямого выхода триггера 4 разрешает прохождение сдвигающих импульсов от шины 10 через второй элемент И 6 на третий вход триггера 4, а уровень логического О с инверсного выхода триггера 4 запрещает прохождение информации через первый элемент И 5 и первый элемент ИЛИ 7 ячейки 1 памяти.

Таким образом, в ячейках 2 и 3 памяти в триггерах которых записывается логический О кода, информация со входа на выход передается через элементы И 5 и ИЛИ 7, а в ячейке памяти 1 информация со входа на выход передается через триггер 4.

С приходом первого сдвигающего импульса произойдет запись логического О в триггере 4 ячейки 1 памят и в регистре не останется ячеек памяти с записанными в них логическими It It

Таким образом, за один такт сдвигающих импульсов произошло перемеще,ние из регистра всех (одной логических 1 записанного в регистре кода и достигнут эффект сдвига только одноименных битов информации.

Формула изобретения

Регистр сдвига, содержащий ячейки памяти, каждая из которых состоит из триггера, первый вход которого соединен с информационным входом регистра сдвига, шину сдвига и шину управления, отлича-ющийся тем, что, с целью расширения области применения, в каждую ячейку памяти регистра сдвига введены элементы И, ИЛИ и элемент НЕ, вход которого соединен с шиной управления, и с первым входом первого элемента И, второй вход первого элемента И подключен ко второму входу триггера данной ячейки памяти и к выходу первого элемента ИЛИ предыдущей ячейки памяти, третий вход первого элемента И каждой ячейки памяти соединен с первым выходом триггера данной ячейки памяти, второй выход триггера которо подключен к первым входам первого и второго элементов ИЛИ данной ячейки, второй вход первого элемента ИЛИ каждой ячейки памяти соединен с выходом первого элемента И данной ячеки памяти, выход элемента НЕ каждой ячейки памяти соединен со вторым входом второго элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй вход второго элемента И подключен к шине сдвига, выход второго элемента И соединен с третьим входом триггера.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-10-23—Публикация

1980-02-26—Подача