Изобретение относится к вычислительной технике и может.применяться для обнаружения сшибок при передаче и хранении информации в Двоичном коде.Известно устройство для контроля параллельного двоичного кода на четность, содержащее регистр сдвига, триггер, элементы И, группы элементов ИЛИ, двр группы элементов И, элемент задержки .

Быстродействие .этого устройства невелико, так как количество сдвигающих импульсов, необходимых для проверки на четность, определяется номером старшего регистра, в который записана логическая 1. v

Наиболее близким к предлагаемому является устройство Для контроля параллельного двоичного кода, содержащее триггер, элемент И и регистр сдвига, кахщый разряд, которого содержит триггер, единичный вход которого является информационным входом устройства, первый дополнительный элемент И и элемент ИЛИ, причем единичный выход триггера каждого разряда соединен с пёрвьми входами соответствукицего первого д эполнитель ного элемента И и элемента ИЛИ, вход ко- .

торого соединен с информационными входами триггера последующего разряда, информационный вход триггера . старшего разряда .соединен со вторьад входом элемента ИЛИ данного разряда ; и со входом сигнала логического нуля . устройства, выход элемента ИЛИ младшего разряда является выходом регистра и соединен с первым входом эле10мента И, второй вход которого соединен со вторыми входами дополнительных элементов И и с синхронизирующим входом устройства, выход элемента И соединен со счетным входом триг15гера, выход которого является выходом устройства, а выходы дополнительных элементов И соединены с синхронизирующими входами триггеров соответствующих разрядов .

20

Недостатком известного устройства является его низкое быстродействие. Хотя количество сдвигающих импульсов равно количеству логических единиц проверяемого кода, при большом числе

25 единиц для проверки кода на четность потребуется значительное время.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем,

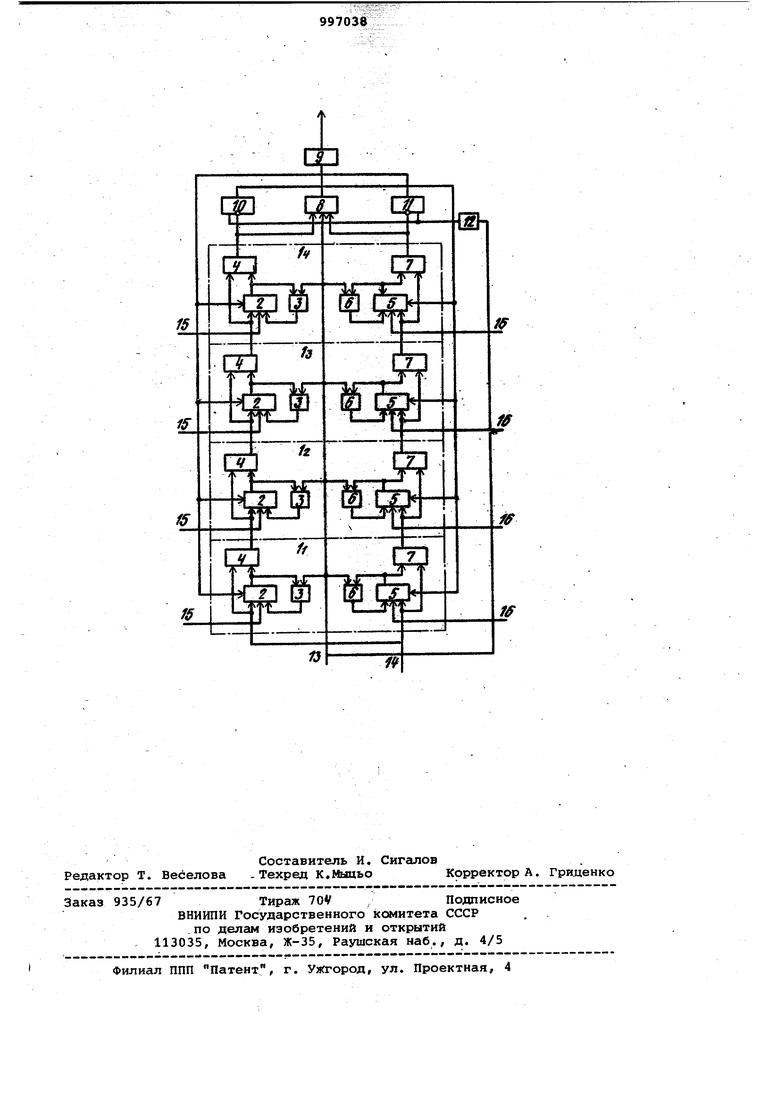

30 что в устройство для контроля параллельного двоичного кода на четч ность, содержащее первый элемент И, триггер четности, регистр сдвига, каждый разряд которого содержит триг гер, элемент И и элемент ИЛИ, Причем синхронизирующий вход устройства сое динен с первыми входами элементов И всех разрядов и с пер:вым входом перв го элемента И, выход которого соединен со счетным входом триггера четности, выход триггера четности явля тся выходом устройства, выход элеме та И каждого разряда регистра соеди нен со входом синхронизации триггера соответствующего разряда регистра сдвига, прямые информационные входы устройства соединены с единичными входами триггеров соответствующих разрядов регистра сдвига, установочный вход устройства соединен с 0входом триггера старшего разряда регистра сдвига и с первым входом элемента ИЛИ этого же разряда, выход триггера каждого разряда регистра сдвига соединен с вторым входом элемента И и первым входом элемента . ИЛИ этого же разряда, выход элеменга ИЛИ каждого разряда регистра,сдвига кроме младшего, роединен с D-входом триггера и вторым входом элемента ИЛИ последующего разряда регистра, сдвига, выход элемента ИЛИ младшего разряда регистра сдвига соединен с вторым входом -первого элемента И, Ьведены второй и третий элементы И и элемент задержки, .а в каждый разряд регистра сдвига введены дополнительный элемент И, дополнительный элемент ИЛИ и дополнительный триггер причем синхронизирующий вход устройства соединен с первыми входами дополнительных элементов И всех разрядов регистра сдвига и через элемент задержки с прямыми входами второго и третьего элементов И, выходы которьах соединены соответственно с нулевыми входами дополнительных триггеров разрядов регистра сдвига, инверсные информационные входы устройства соединены с единичными входами дополнительных триггеров соответствующих разрядов регистра сдвига, установочный вход устройства соединен с 0-входом дополнительного триггера стартиего разряда регистра сдвига и с первым входом дополнительного элемента ИЛИ этого же разряда, выход дополнительного триггера каждо го разярада регистра сдвига соединен со вторым входом дополнительного элемента И и с первым входом дополни тельного элемента ИЛИ этого .же разря да, выход дополнительного элемента ИЛИ каждого разряда регистра сдвига, кроме младшего, соединен с О-входом дополнительного триггера и вторымвходом дополнительного элемента ИЛИ последующего разряда регистра сдвига выходы элемента ИЛИ и дополнительнего элемента ИЛИ младшего разряда регистра сдвига соединены соответственно с инверсными входами второго и третьего элементов И, третий вход первого элемента И соединен с инверсным входом третьего элемента И, выход дополнительного элемента И каждого разряда регистра сдвига соединён с ВХОДОМ синхронизации дополнительного триггера соответствующего разряда. В предлагаемом устройстве производится раздельный одновременный сдвиг логических 1 и О проверяемого кода. Данное, изобретение может быть использовано для контроля кодов с четным числом разрядов. Если проверяемый код содержит четное число разрядов, то в этом -коде признак четности единиц совпадает с значением признака четности нулей: если число единиц четное, то и число нулей также четное и, нйоборот, если число единиц нечетное, то и число нулей нечетное. Так как в общем случае проверяемый код содержит разное количество единиц и нулей, то подсчет меньшего количества одноименных битов сок ращает время проверки - кода на четность, т.е. повышает быстродействие. На чертеже представлена схема устройства для проверки 4-х разрядного параллельного двоичного кода на четность. Устройство содержит регистр сдвига 1, состоящий из разрядов 1 ,... , l., каждый из которых содержит триггер 2, первый элемент И 3, элемент ИЛИ 4, д;ополнительный триггер 5, дополнительный элемент И 6, допсялнительный элемент ИЛИ 7, а также первый элемент И. 8, триггер четности 9, второй элемент И 10 и третий элемент И 11г элемент задержки 12, синхронизирующий вход 13, установочный вход 14, прямые информационные входы 15 и инверсные информационные входы 16. Установочные входы триггера 2 и дополнительного триггера 5 старшего разряда Ij регистра 1 соединены с установочным входом 14 устройства. В каждом разряде l,...,. регистра 1 единичные входы триггера 2 и дополнительного триггера 5 соединены с соответствующим прямым информационньом входом 15 регистра и инверсным информационным входом 16 регистра, установочные входы триггеров 2 и 5 соединены соответственно с первыми входами элементов ИЛИ 4 и 7, вторые входы которых соединены соответственно с прямым входом триггера 2 и инверсным выходом дополнительного триггера 5, указанные точки соединений подключены соответственно ко вторым входам элементов И 3 и 6, первые входы которых соединены с синхронизирующим входом 13 устройства, а выходы соответственно с синхнизирующими входами триггеров,2 и 5.

Установочный вход 14, имеющий потенциал логического О, соединен с установочными входами триггера 2 и дополнительного триггера 5 старшего разряда 1 регистра..

. Выход элемента ИЛИ 4 предыдущего разряда соединен с установочным входом триггера 2 последующего разряда. Выход злемента ИЛИ 4 младшего разряд 1д соединен со входом первого элемента И 8. Выход дополнительного .злву1ента ИЛИ 7 предыдущего разряда сединен с установочным входом дополнительного триггера 5 последующего разряда. Выход дополнительного элемента ИЛИ 7 младшегоразряда соединен с третьим входом, первого элемента И 8, первый вход которого соединен с синхронизирующим входом 13 .устройства, а выход - со входом триг гера 9 четности.

Выходы элементов или 4 и 7 младше го разряда 1. соединены соответственно с инверсными входами второго 10 и третьего 11 элементов И, прямыв входы которых соединены с выходом элемента 12 задержки, вход которого соединен с синхровходом 13. Выход второго элемента И 10 соединен со-входами сброса всех триггеров 5, а выход третьего элемента И 11 со входами сброса всех триггеров .

Установка всех триггеров в исходное нулевое состояние на чертеже ус ловно не показана.

В исходном состоянии все триггеры установлены в нулевое состояние. При этом на прямых выходах всех триггеров 2 и всех дополнительных триггерах 5 установлены логические О.

С выхода элементов ИЛИ 4 и 7 млад шего разряда 1л на второй и третий входы злемента И 8 поступают логические О и на счетный вход триггера 9 четности также поступает логический 0.

Рассмотрим проверку на четность кода 1110.

При подаче прямого и инверсного значений кода соответственно на прямые 15 и инверсные 16 информационные входы устройства происходит у.становка триггеров в следуюцие состояния: триггеры 2 разрядов 1 , l Ч и триггера 5 разряда 14-3 единичное состояние; триггер 2 разряда I, и триггеры 5 разрядов 1, l. 1-j, - в нулевое состояние.

Триггер 2 или 5, установленный в единичное состояние, разрешает элемент И 3 или б для прохождения через него синхроимпульса от вхо.да 13.

Триггер 2 или 5, установленный в нулевое состояние, запрещает элемент И 3 или б для прохождения через него синхроимпульса.

Единичные потенциалы с прямых зы ходов триггеров 2 разрядов 1 , 1, 1з и триггера 5 разряда 14 через соответствующие элементы ИЛИ 4 и 7 поступают соответственно на второй и третий входы элемента И 8, разрешая его для прохождения синхроимпульсов от входа 13.

Единичные потенциалы с выходов элементов ИЛИ 4 и 7 младшего разряда 1 .поступают соответственно на инверсные.входы второго и третьегоэлементов И 10 и 11, запрещая их для прохождения импульсов от элемента задержки 12.

Первый синхроимпульс производит следующие действия: пройдя через элемент И 8, изменяет состояние триггера 9 четности; записывает нулевой уровень в триггер 2 разряда 1, что блокирует элемент И 3 этого разряда, переписывает единичный уровень в триггерах 2 разрядов 1 и l,j, записывает нулевой уровень, в триггер 5 разряда 1, что блокирует дополнительный элемент И 6 данного разряда для прохождения через нег.о следукмцего синхроимпульса.

На инверсный вход третьего элемента И 11 с выхода элемента ИЛИ 7 младшего разряда Ц поступает нулевой уровень, который разрешает третий элемент И 11 для прохождения чэреэ него задержанного в элементе задержки 12 синхроимпульса.

Минимальное время задержки определяется временем переключения триггеров 2 и - 5. .

Через время задержки первый синхримпульс .проходит, через третий элемен И 11 и поступает на сброс триггеров 2 всех разрядов-, устанавливая их в нулевое состояние. Состояние ±риггер 9 четности указывает, что проверяемы код нечетен. Для проверки кода 1110 понадобилс-я один такт синхр-оимпульсо против трех тактов, необходимых для проверки по прототипу.

Положительный эффект от использования данного устройства заключается в повышении быстродействия определения четности параллельного дзоичного кода за счет того, что производится одновременно проверка на четность логических 1 и.о. Так как в общем слу чае количество разное, то проверка меньшего количества одноименных битов на четность, однозначная с про-варкой на четность проверяемого кода значительно повышает быстродействие.

Формула изобретения

Устройство для контроля параллельного двоичного кола на четность, со-. держацее первый элемент И, триггер четности, регистр сдвига, каждый раз- ряд которого содержит триггер, элемент И и элемент ИЛИ, причем синхро /низирующий вход устройства соединен с первыми входами элементов И всех разрядов и с первым входом первого элемента И, выход которого соединен со счетным входом триггера чётности выход триггера четности является выходом устройства, выход элемента И каждого регистра сдвига соединен с входом синхронизации триггера соответствующего разряда регистра сдви га, прямые информационные входы устройства соединены с единичными входaми триггеров соответствующих разрядов регистра сдвига, установочный вход устройства соединен с D-входом триггера старшего разряда регистра сдвига и с первым входом элемента ИЛ этого же ,выход триггера кажд го разряда регистра сдвига соединен с вторым входом элемента И и первым входом элемента ИЛИ этого же разряда выход элемента ИЛИ каждого разряда регистра сдвига, кроме млйдшего, соединен с D-входом триггера и вторымвходом элемента ИЛИ последующего раз ряда регистра сдвига, выход элемента ИЛИ младшего разряда регистра сдв га соединен с вюрым входом первого элемента И, отличающееся тем, что, с целью повышения быстродействия f в устройство введены второй и третий элементы И и элемент задержки, а в каждый разряд регистра сдвига введены дополнительный элемент И, дополнительный элемент ИЛИ и дополнительный триггер, причем синхронизирующий вход устройства соединен с первыми входами дополнительных элементов И всех разрядов ре гистра сдвига и через элемент задерж ки с прямыми входами второго и треть его элементов И, выходы которых соединены соответственно с нулевыми входами дополнительных триггеров всех разрядов регистра сдвига, инверсные и1|формационные входы устройства соединены с единичными входами дополнительных триггеров соответствующих разрядов регистра сдвига, уст тановочный вход устройства соединен с 0-вх6дом дополнительного триггера старшего разряда регистра сдвига и с первьм ВХОДСЛ1 дополнителыюро элемента ИЛИ этого же разряда, выэссщ дополнительного триггера каждого разряда регистра сдвига соединен с вторым входом дополнительного элемента И и первым входом дополнительного элемента ИЛИ этого же раэряда, выход дополнительного элемента ИЛИ каждого разряда регистра сдвига, кроме младшего, соединен с Dвходом дополнительного триггера и вторым входом дополнительного элемента ИЛИ последующего разряда ;регистра сдвига, выходы элемента ИЛИ и дополнительного элемента ИЛИ, младшего разряда регистра сдвига соединены соответственно с инверсныш входами второго и третьего злемейтооз И, тре- , тий вход первого элемента И соевдинен с инверсным входом третЬего элемента И, выход дополнительного элемента И каждого разряда регистра сдвига соединен с входом синхронизации дополнительного триггера соответствующего разряда. Источники иифо1 1ации,. ринятые во вйнмание при экспертизе 1.Авторское свидетельство СССР 746530, кл.. G Об F 11/10, 19вО. 2.Авторское свидетельство СССР о заявке № 2865062/18-24, кл. G Об F 11/10, 1980 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования контрольного кода по четности | 1980 |

|

SU934477A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1980 |

|

SU871166A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1023334A2 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| Преобразователь последовательного кода в параллельный | 1988 |

|

SU1674382A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1513526A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для контроля кода на четность | 1988 |

|

SU1529224A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

Авторы

Даты

1983-02-15—Публикация

1981-06-24—Подача