11287

Изобретение относится к автомати- ке и вычислительной технике и может быть использовано в качестве устройства допусковой оценки при реализации технических средств дискретной автоматики в устройствах программного управления о

Цель изобретения - расширение области применения устройства путем

обеспечения возможности сравнения чи- 10 производится аналогично сравнению

чисел со знаком .плюс. Числа со знаком минус инвертируются и сравниваются в обратном коде. Устройство принимает сигнал перегрузки (П)

сел со знаками и без знаков и учета информации о перегрузке.

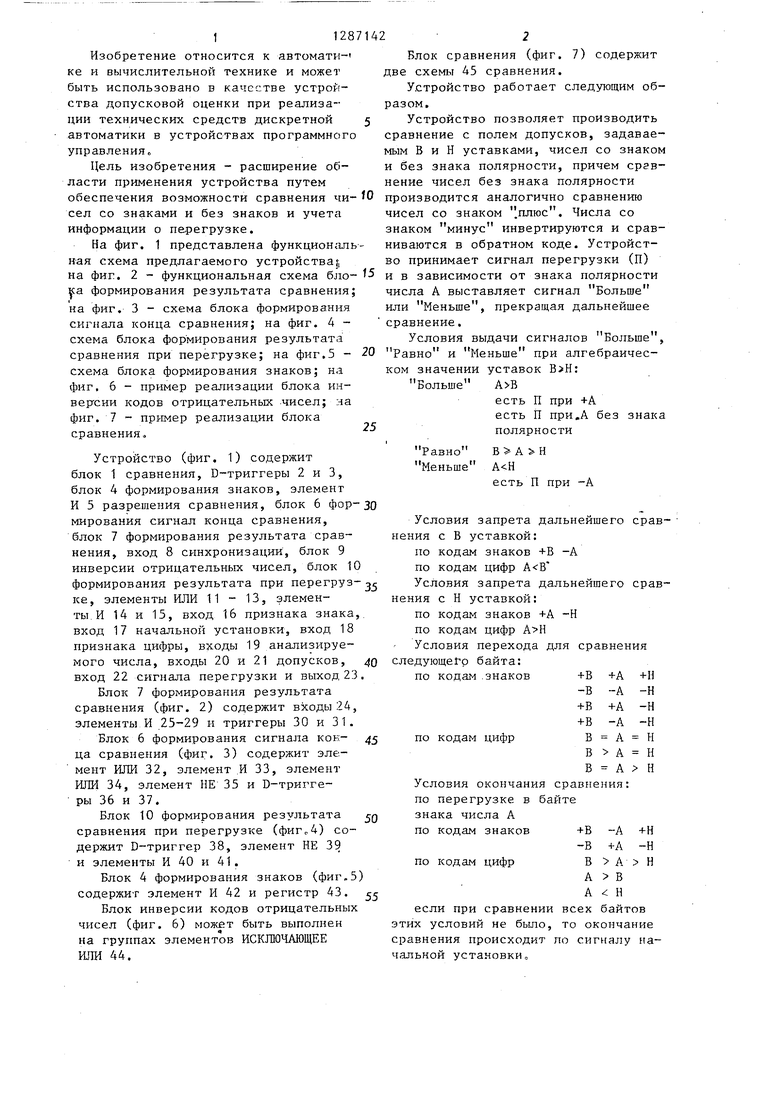

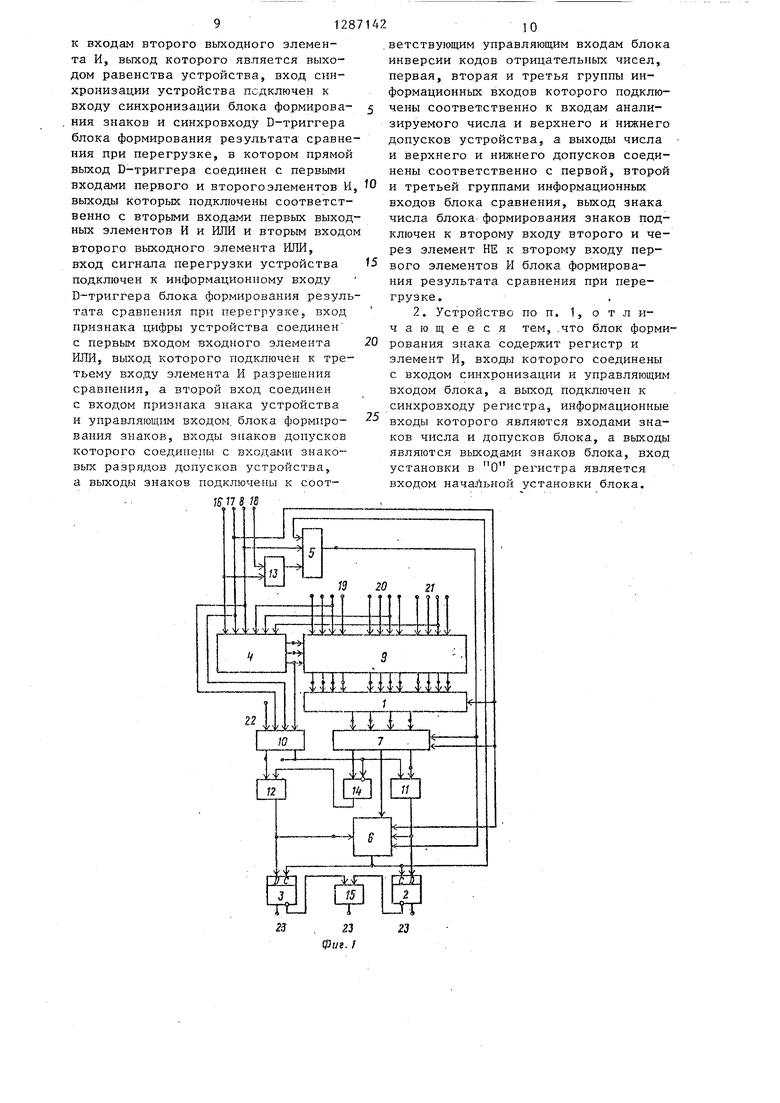

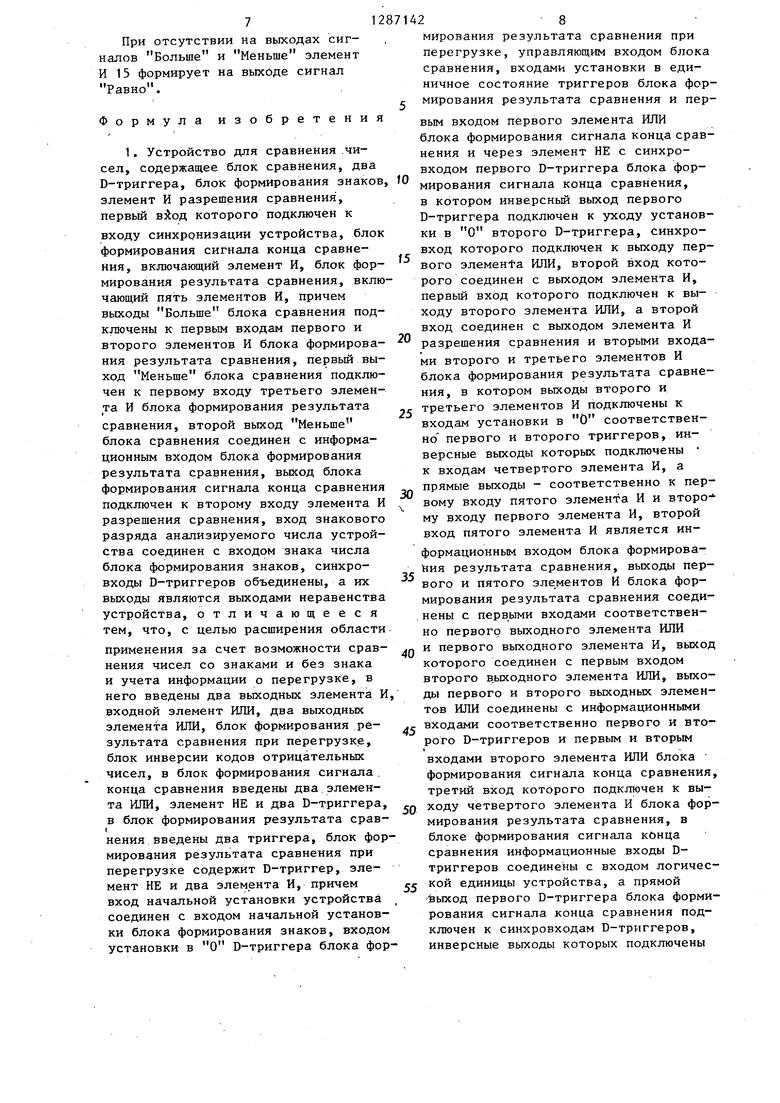

На фиг. 1 представлена функциональная схема предлагаемого устройства;,

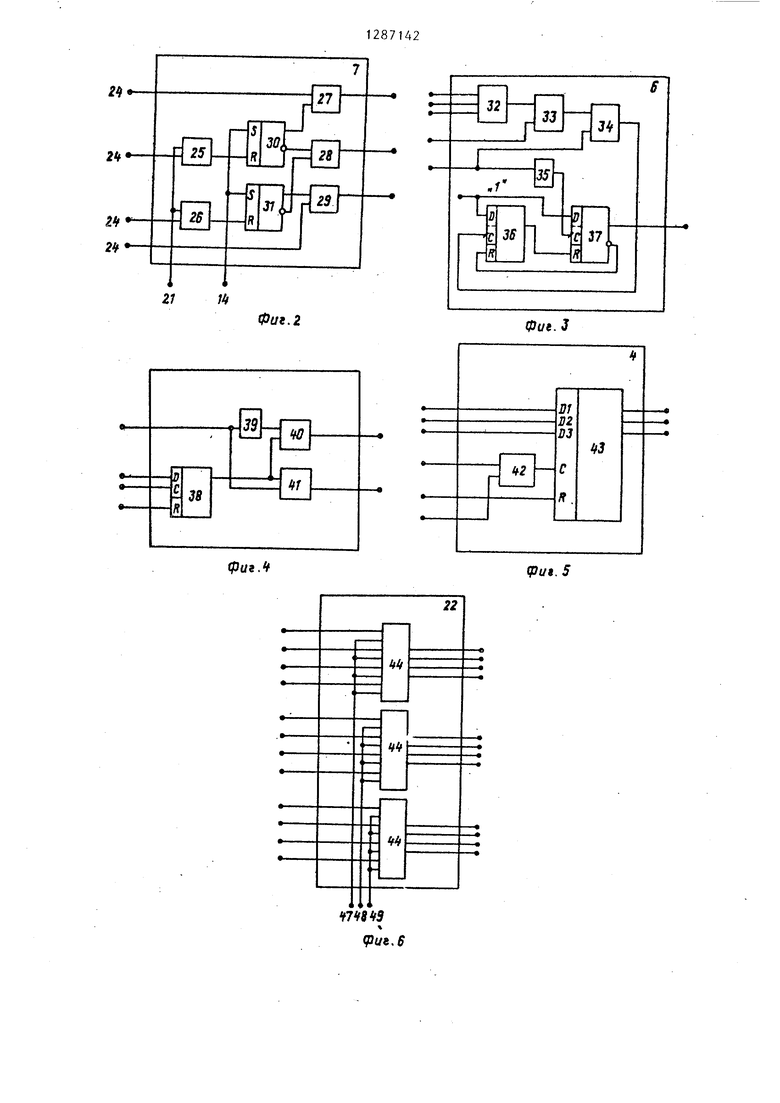

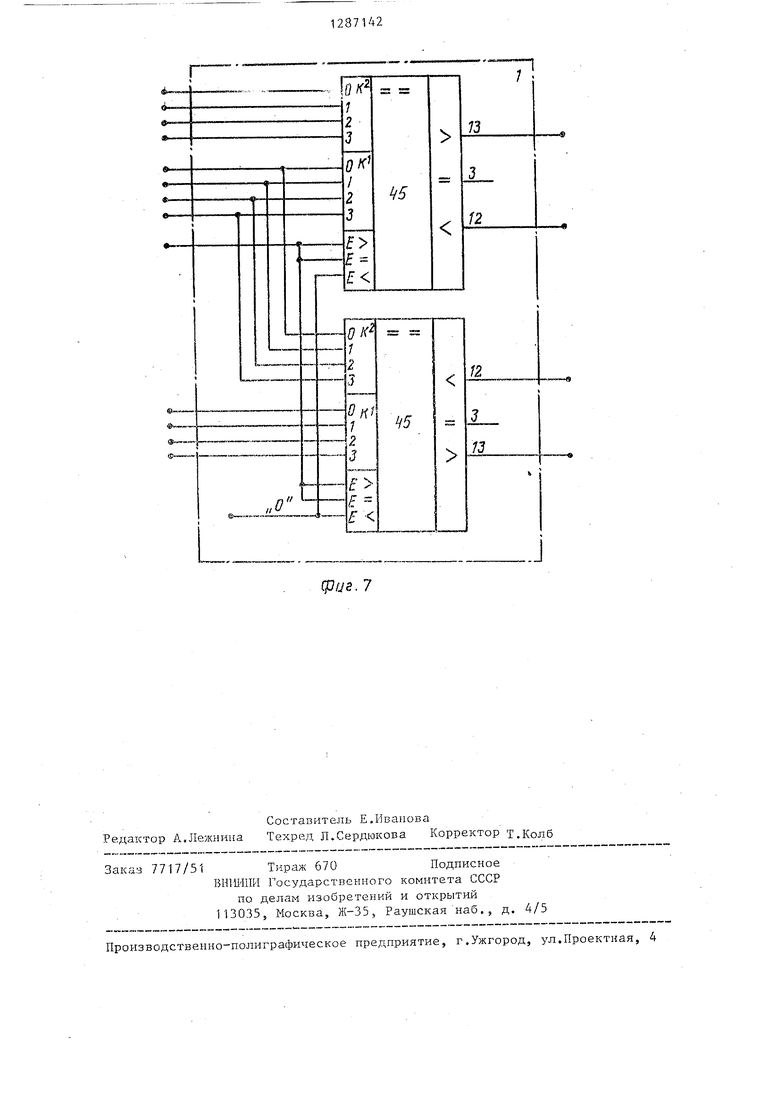

на фиг. 2 - функциональная схема бло- 5 и в зависимости от знака полярности уа формирования результата сравнения; на фиг. 3 - схема блока формирования сигнала конца сравнения; на фиг. 4 - схема блока формирования результата сравнения при перегрузке; на фиг.5 - 20 схема блока формирования знаков; на фиг, 6 - пример реализации блока ин- вергсии кодов отрицательных чисел; за фиг. 7 - пример реализации блока

числа А выставляет сигнал Больше или Меньше, прекращая дальнейшее сравнение.

Условия выдачи сигналов Больше Равно и Меньше при алгебраичессравнения.

Устройство (фиг. 1) содержит блок 1 сравнения, D-триггеры 2 и 3, блок 4 формирования знаков, элемент И 5 разрешения сравнения, блок 6 фор-30 мирования сигнал конца сравнения, блок 7 формирования результата сравнения, вход 8 синхронизации, блок 9 инверсии отрицательных чисел, блок 10 формирования результата при перегруз- з ке, элементы ИЛИ 11 - 13, элементы И 14 и 15, вход 16 признака знака, вход 17 начальной установки, вход 18 признака цифры, входы 19 анализируемого числа, входы 20 и 21 допусков, 40 вход 22 сигнала перегрузки и выход 23.

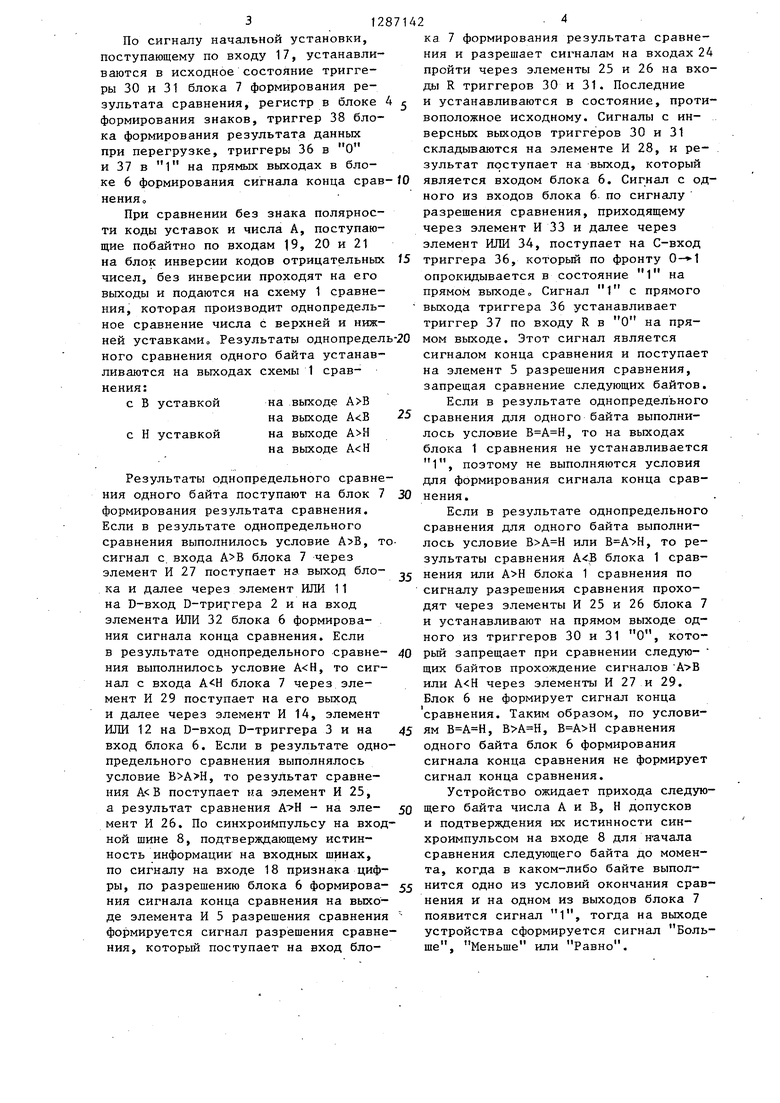

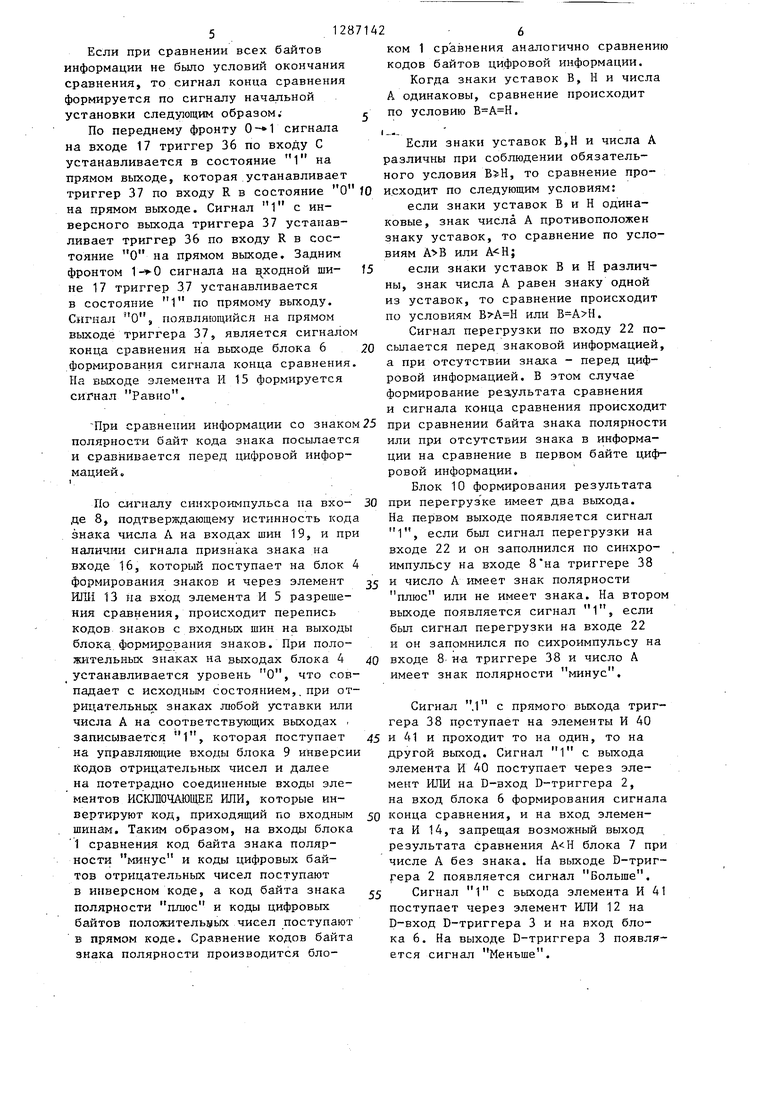

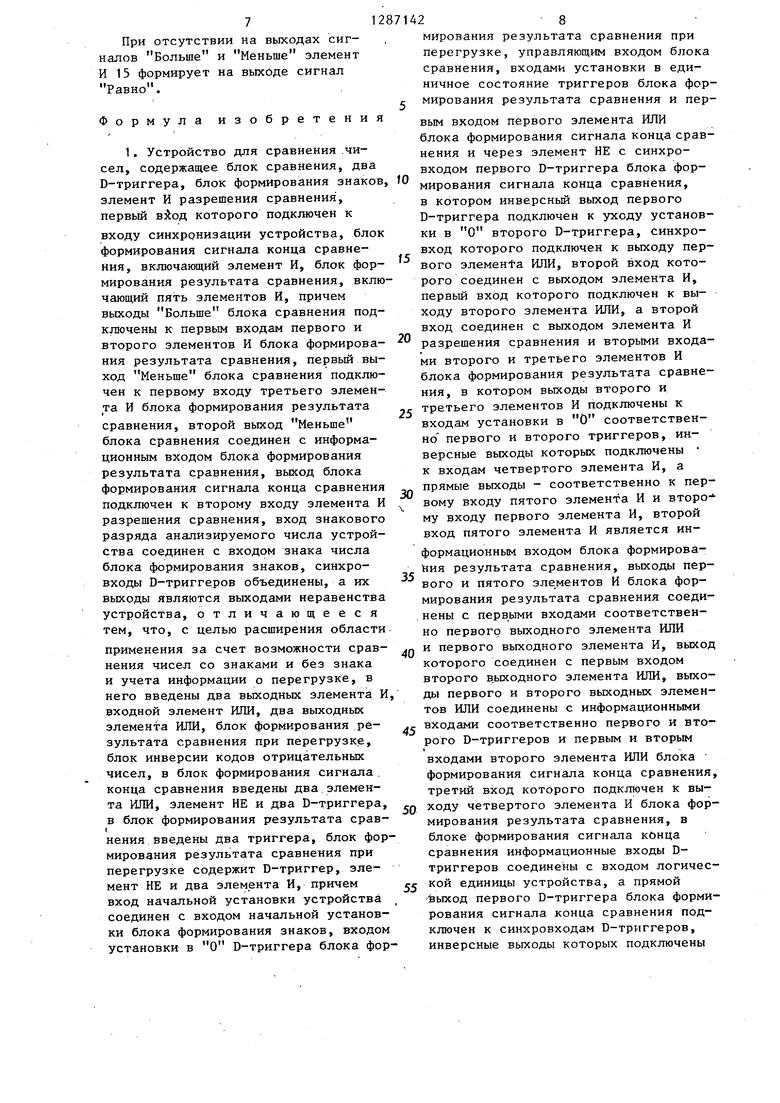

Блок 7 формирования результата сравнения (фиг. 2) содержит входы 24, элементы И 25-29 и триггеры 30 и 31.

Блок 6 формирования сигнала кок- 5 ца сравнения (фиг. 3) содержит элемент ИЛИ 32, элемент .И 33, элемент ИЛИ 34, элемент НЕ 35 и D-триггеры 3 6 и 3 7 .

Блок 10 формирования результата Q сравнения при перегрузке (фиГо4) содержит D-триггер 38, элемент НЕ 39 и элементы И 40 и 41.

Блок 4 формирования знаков (фиг.5) содержит элемент И 42 и регистр 43.

Блок инверсии кодов отрицательных чисел (фиг. 6) может быть выполнен на группах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 44.

ком значении уставок Больше

есть П при +А

есть П при.А без знака

полярности

Равно Меньше

есть П при -А

Условия запрета дальнейшего срав нения с В уставкой:

по кодам знаков +В -А

по кодам цифр

Условия запрета дальнейшего срав нения с Н уставкой:

по кодам знаков +А -Н

по кодам цифр

Условия перехода для сравнения следующего байта:

по кодам .знаков

по кодам цифр

+В

+А -А +А -А

А А В А

Условия окончания сравнения: по перегрузке в байте знака числа А по кодам знаков

+В

+В

В

В

+Н

-Н

-Н

-Н

Н

Н

Н

по кодам цифр

+В -В В А А

-А +А

А

В Н

+н

-Н Н

если при сравнении всех байтов этих условий не было, то окончание сравнения происходит по сигналу начальной установки.

Блок сравнения (фиг. 7) содержит две схемы 45 сравнения.

Устройство работает следующим образом.

Устройство позволяет производить сравнение с полем допусков, задаваемым В и Н уставками, чисел со знаком и без знака полярности, причем сравнение чисел без знака полярности

чисел со знаком .плюс. Числа со знаком минус инвертируются и сравниваются в обратном коде. Устройство принимает сигнал перегрузки (П)

и в зависимости от знака полярности

числа А выставляет сигнал Больше или Меньше, прекращая дальнейшее сравнение.

Условия выдачи сигналов Больше, Равно и Меньше при алгебраичеси в зависимости от знака полярности

ком значении уставок Больше

есть П при +А

есть П при.А без знака

полярности

Равно Меньше

есть П при -А

Условия запрета дальнейшего сравнения с В уставкой:

по кодам знаков +В -А

по кодам цифр

Условия запрета дальнейшего сравнения с Н уставкой:

по кодам знаков +А -Н

по кодам цифр

Условия перехода для сравнения следующего байта:

кодам .знаков

кодам цифр

+В

+А -А +А -А

А А В А

овия окончания сравнения: перегрузке в байте ка числа А кодам знаков

+В

+В

В

В

+Н

-Н

-Н

-Н

Н

Н

Н

кодам цифр

+В -В В А А

-А +А

А

В Н

+н

-Н Н

если при сравнении всех байтов этих условий не было, то окончание сравнения происходит по сигналу начальной установки.

По сигналу начальной установки, поступающему по входу 17, устанавливаются в исходное состояние триггеры 30 и 31 блока 7 формирования результата сравнения, регистр в блоке формирования знаков, триггер 38 блока формирования результата данных при перегрузке, триггеры 36 в О и 37 в 1 на прямых выходах в блоке 6 формирования сигнала конца срав ненияо

При сравнении без знака полярности коды уставок и числа А, поступающие побайтно по входам 19, 20 и 21 на блок инверсии кодов отрицательных чисел, без инверсии проходят на его выходы и подаются на схему 1 сравнения, которая производит однопредель- ное сравнение числа с верхней и нижней уставками о Результаты однопредел ного сравнения одного байта устанавливаются на выходах схемы 1 сравнения:

с В уставкой на выходе

на выходе

с Н уставкой на выходе

на выходе

Результаты однопредельного сравнения одного байта поступают на блок 7 формирования результата сравнения. Если в результате однопредельного сравнения выполнилось условие , т сигнал с. входа блока 7 через элемент И 27 поступает на выход бло-

ка и далее через элемент ИЛИ 11 на D-вход В-три1; гера 2 и на вход элемента ИЛИ 32 блока 6 формирования сигнала конца сравнения. Если в результате однопредельного сравне- ния выполнилось условие , то сигнал с входа блока 7 через элемент И 29 поступает на его выход и далее через элемент И 14, элемент ИЛИ 12 на D-вход D-триггера 3 и на вход блока 6. Если в результате одно предельного сравнения выполнялось условие , то результат сравнения поступает на элемент И 25, а результат сравнения - на эле- мент И 26. По синхроимпульсу на входной шине 8, подтверждающему истинность информации на входных шинах, по сигналу на входе 18 признака цифры, по разрешению блока 6 формирова- ния сигнала конца сравнения на выходе элемента И 5 разрешения сравнения формируется сигнал разрешения сравнения, который поступает на вход блока 7 формирования результата сравнения и разрешает сигналам на входах 24 пройти через элементы 25 и 26 на входы R триггеров 30 и 31. Последние и устанавливаются в состояние, противоположное исходному. Сигналы с инверсных выходов триггеров 30 н 31 складываются на элементе И 28, и результат поступает на выход, который является входом блока 6. Сигнал с одного из входов блока 6 по сигналу разрешения сравнения, приходящему через элемент И 33 и далее через элемент ИЛИ 34, поступает на С-вход триггера 36, который по фронту опрокидывается в состояние 1 на прямом выходе Сигнал 1 с прямого выхода триггера 36 устанавливает триггер 37 по входу R в О на прямом выходе. Этот сигнал является сигналом конца сравнения и поступает на элемент 5 разрешения сравнения, запрещая сравнение следующих байтов.

Если в результате однопредельного сравнения для одного байта выполнилось условие , то на выходах блока 1 сравнения не устанавливается 1, поэтому не выполняются условия для формирования сигнала конца сравнения.

Если в результате однопредельного сравнения для одного байта выполнилось условие или , то результаты сравнения А-сВ блока 1 сравнения или блока 1 сравнения по сигналу разрешения сравнения проходят через элементы И 25 и 26 блока 7 и устанавливают на прямом выходе одного из триггеров 30 и 31 О, который запрещает при сравнении следую- щих байтов прохождение сигналов или через элементы И 27 и 29. Блок 6 не формирует сигнал конца сравнения. Таким образом, по условиям , , сравнения одного байта блок 6 формирования сигнала конца сравнения не формирует сигнал конца сравнения.

Устройство ожидает прихода следующего байта числа А и В, Н допусков и подтверждения их истинности синхроимпульсом на входе 8 для начала сравнения следующего байта до момента, когда в каком-либо байте выполнится одно из условий окончания сравнения иг на одном из выходов блока 7 появится сигнал 1, тогда на выходе устройства сформируется сигнал Больше, Меньше или Равно.

Если при сравнении всех байтов информации не бьшо условий окончания сравнения, то сигнал конца сравнения формируется по сигналу начальной установки следующим образом;

По переднему фронту сигнала на входе 17 триггер 36 по входу С устанавливается в состояние 1 на прямом выходе, которая устанавливает триггер 37 по входу R в состояние на прямом выходе. Сигнал 1 с инверсного выхода триггера 37 устанавливает триггер 36 по входу R в состояние О на прямом выходе. Задним фронтом сигнал на ходной ши- 15 не 17 триггер 37 устанавливается в состояние 1 по прямому выходу. Сигнал О, появляющийся на прямом выходе триггера 37, является сигналом

ком 1 сравнения аналогично сравнению кодов байтов цифровой информации.

Когда знаки уставок В, Н и числа А одинаковы, сравнение происходит по условию .

I-..

Если знаки уставок В,Н и числа А

различны при соблюдении обязательного условия , то сравнение происходит по следующим условиям:

если знаки уставок Б и Н одинаковые, знак числа А противоположен знаку уставок, то сравнение по условиям или

если знаки уставок В и Н различны, знак числа А равен знаку одной

из уставок, то сравнение происходит по условиям или .

Сигнал перегрузки по входу 22 по- 20 сылается перед знаковой информацией, а при отсутствии знака - перед цифровой информацией. В этом случае формирование реаультата сравнения и сигнала конца сравнения происходит

При сравнении информации со знаком 25 при сравнении байта знака полярности

или при отсутствии знака в информации на сравнение в первом байте цифровой информации.

Блок 10 формирования результата По сигналу синхроимпульса на вхо- 30 де 8, подтверждающему истинность кода знака числа А на входах шин 19, и при наличии сигнала признака знака на входе 16, который поступает на блок 4

конца сравнения на выходе блока 6 формирования сигнала конца сравнения. На выходе элемента И 15 формируется сигнал Равно.

полярности байт кода знака посылается и сравнивается перед цифровой информацией.

при перегрузке имеет два выхода. На первом выходе появляется сигнал 1, если был сигнал перегрузки на входе 22 и он заполнился по синхроимпульсу на входе триггере 38

формирования знаков и через элемент ШБ1 13 иа вход элемента И 5 разрешения сравнения, происходит перепись кодов знаков с входных щин на выходы блока формирования знаков. При положительных знаках на выходах блока 4 устанавливается уровень О, что совпадает с исходным состоянием,, при от- рицательньк знаках любой уставки или числа А на соответствующих выходах , записывается 1, которая поступает

Сигнал ,1 с прямого выхода три гера 38 поступает на элементы И 40 45 и 41 и проходит то на один, то на

на управляющие входы блока 9 инверсии другой выход. Сигнал 1 с выхода

кодов отрицательных чисел и далее на потетрадно соединенные входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, которые инвертируют код, приходящий по входным шинам. Таким образом, на входы блока 1 сравнения код байта знака полярности минус и коды цифровых байтов отрицательных чисел поступают в инверсном коде, а код байта знака полярности imioc и коды цифровых байтов положительных чисел поступают в прямом коде. Сравнение кодов байта знака полярности производится блоком 1 сравнения аналогично сравнени кодов байтов цифровой информации.

Когда знаки уставок В, Н и числа А одинаковы, сравнение происходит по условию .

I-..

Если знаки уставок В,Н и числа А

различны при соблюдении обязательного условия , то сравнение происходит по следующим условиям:

если знаки уставок Б и Н одинаковые, знак числа А противоположен знаку уставок, то сравнение по условиям или

если знаки уставок В и Н различны, знак числа А равен знаку одной

Блок 10 формирования результата

при перегрузке имеет два выхода. На первом выходе появляется сигнал 1, если был сигнал перегрузки на входе 22 и он заполнился по синхроимпульсу на входе триггере 38

и число А имеет знак полярности

плюс или не имеет знака. На втором выходе появляется сигнал 1, если был сигнал перегрузки на входе 22 и он запомнился по сихроимпульсу на входе 8- н-а триггере 38 и число А

имеет знак полярности минус,

Сигнал ,1 с прямого выхода триггера 38 поступает на элементы И 40 45 и 41 и проходит то на один, то на

другой выход. Сигнал 1 с выхода

элемента И 40 поступает через элемент ИЛИ на D-вход D-триггера 2, на вход блока 6 формирования сигнала

30 конца сравнения, и на вход элемента И 14, запрещая возможный выход результата сравнения блока 7 при числе А без знака. На вьжоде D-триг- рера 2 появляется сигнал Больше.

55 Сигнал 1 с вьЕХода элемента И 41 поступает через элемент ИЛИ 12 на D-вход D-триггера 3 и на вход блока 6. На выходе D-триггера 3 появляется сигнал Меньше.

При отсутствии на выходах сигналов Больше и Меньше элемент И 15 формирует на выходе сигнал Равно.

Формула изобретения

1. Устройство для сравнения .чисел, содержащее блок сравнения, два D-триггера, блок формирования знаков элемент И разрешения сравнения , первый которого подключен к

входу синхронизации устройства, блок формирования сигнала конца сравнения, включающий элемент И, блок формирования результата сравнения, включающий пять элементов И, причем выходы Больше блока сравнения подключены к первьм входам первого и второго элементов И блока формирования результата сравнения, первый выход Меньше блока сравнения подключен к первому входу третьего элемента И блока формирования результата сравнения, второй выход Меньше блока сравнения соединен с информационным входом блока формирования результата сравнения, выход блока формирования сигнала конца сравнения подключен к второму входу элемента И разрешения сравнения, вход знакового разряда анализируемого числа устройства соединен с входом знака числа блока формирования знаков, синхро- входы D-триггеров объединены, а их выходы являются выходами неравенства устройства, отличающееся тем, что, с целью расширения области

применения за счет возможности сравнения чисел со знаками и без знака и учета информации о перегрузке, в него введены два выходных элемента И входной элемент ИЛИ, два выходных элемента ИЛИ, блок формирования результата сравнения при перегрузке, блок инверсии кодов отрицательных чисел, в блок формирования сигнала . конца сравнения введены два.элемента ИЛИ, Элемент НЕ и два D-триггера,

в блок формирования результата сравI

нения введены два триггера, блок формирования результата сравнения при перегрузке содержит D-триггер, элемент НЕ и два элемента И, причем вход начальной установки устройства соединен с входом начальной установки блока формирования знаков, входом установки в О D-триггера блока фор

.

,

10

15

20

25

871428

мирования результата сравнения при перегрузке, управляющим входом блока сравнения, входами установки в единичное состояние триггеров блока фор- мирования результата сравнения и первым входом первого элемента ИЛИ блока формирования сигнала конца сравнения и через элемент НЕ с синхро- входом первого D-триггера блока формирования сигнала конца сравнения, в котором инверсньй выход первого D-триггера подключен к уходу установки в О второго D-тригг.ера, синхро- вход которого подключен к выходу первого элемента ИЛИ, второй вход которого соединен с выходом элемента И, первый вход которого подключен к выходу второго элемента ИЛИ, а второй вход соединен с выходом элемента И разрешения сравнения и вторыми входами второго и третьего элементов И блока формирования результата сравнения, в котором выходы второго и третьего элементов И подключены к входам установки в О соответственно первого и второго триггеров, инверсные выходы которых подключены к входам четвертого элемента И, а прямые выходы - соответственно к первому входу пятого элемента И и второ- му входу первого элемента И, второй вход пятого элемента И является информационным входом блока формирования результата сравнения, выходы первого и пятого элементов И блока формирования результата сравнения соединены с первыми входами соответственно первого выходного элемента ИЛИ и первого выходного элемента И, выход которого соединен с первым входом второго в.ыходного элемента ИЛИ, выходы первого и второго выходных элементов ИЛИ соединены с информационными входами соответственно первого и второго Б-триггеров и первым и вторым входами второго элемента ИЛИ блока формирования сигнала конца сравнения, третий вход которого подключен к выходу четвертого элемента И блока формирования результата сравнения, в блоке формирования сигнала конца сравнения информационные входы D- триггеров соединены с входом логической единицы устройства, а прямой первого D-триггера блока формирования сигнала конца сравнения подключен к синхровходам D-триггеров, инверсные выходы которых подключены

30

35

40

45

50

55

9128

к входам второго выходного элемента И, выход которого является выходом равенства устройства, вход синхронизации устройства подключен к входу синхронизации блока формирования знаков и синхровходу D-триггера блока формирования результата сравнения при перегрузке, в котором прямой выход D-триггера соединен с первыми входами первого и второгоэлементов И, выходы которых подключены соответственно с вторыми входами первых выходных элементов И и ИЛИ и вторым входом второго выходного элемента ИЛИ, вход сигнала перегрузки устройства подключен к информационному входу D-триггера блока формирования результата срав}1ения при перегрузке., вход признака цифры устройства соединен с первым входом входного элемента ИЛИ, выход которого подключен к третьему входу элемента И разрешения сравнения, а второй вход соединен с входом признака знака устройства и управляющим входом, блока формирования знаков, входы знаков допусков которого соединены с BxoAaj ni знаковых разрядов допусков устройства, а выходы знаков подключены к соот П 8 IS

10

,ветствующим управляющим входам блока инверсии кодов отрицательных чисел, первая, вторая и третья группы информационных входов которого подключены соответственно к входам анализируемого числа и верхнего и нижнего допусков устройства, а выходы числа и верхнего и нижнего допусков соединены соответственно с первой, второй

и третьей группами информационных входов блока сравнения, выход знака числа блока формирования знаков подключен к второму входу второго и через элемент НЕ к второму входу первого элементов И блока формирования результата сравнения при перегрузке.

2. Устройство по п. 1, отличающее ся тем, .что блок форми

рования знака содержит регистр и элемент И, входы которого соединены с входом синхронизации и управляющим входом блока, а выход подключен к синхровходу регистра, информационные входы которого являются входами знаков числа и допусков блока, а выходы являются выходами знаков блока, вход установки в О регистра является входом начальной установки блока.

14

2 itiwrr

2; ;-

Фие.2

. J

| название | год | авторы | номер документа |

|---|---|---|---|

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| Делительное устройство | 1983 |

|

SU1176324A1 |

| Устройство для умножения в избыточной системе счисления | 1983 |

|

SU1124286A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Устройство для поиска информации | 1980 |

|

SU920703A1 |

| Устройство для допускового контроляпАРАМЕТРОВ | 1979 |

|

SU851341A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для сложения и вычитания | 1980 |

|

SU922730A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве устройства допусковой оценки при реализации технических средств дискретной автоматики в устройствах программного управления. Цель изобретения - расширение области применения за счет- возможности сравнения чисел со знаками и без знака и учета информации о перегрузке. Устройство содержит блок сравнения, D-триггеры, блоки формирования знаков, формирования сигнала конца сравнения, формирования результата сравнения, формирования результата сравнения при перегрузке, блок инверсии отрицательных чисел, элементы и; ИЛИ. Устройство разрешает формирование результата сравнения за счет формирования двух- предельного результата сравнения по результатам алгебраических однопре- дельньк результатов сравнения числа А с уставками В и Н, за счет введения управляемой схемы инверсии кодов отрицательных чисел по кодам знаков минус А, В, Н при однопредельном сравнении. Анализ пришедшей на сравнение информации осуществляется по кодам признаков блоками разрешения сравнения, формирования знаков, формирования результата сравнения при перегрузке. 1 з.п. ф-лы, 7 ил. а (Л КС 00 4 to

Л/ HZ 03

tfS

F

«риг.

(put. 5

%

ф(/е.5

CPU8.7

| Устройство для сравнения чисел | 1978 |

|

SU809164A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 758142, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-30—Публикация

1985-09-04—Подача