1

Изобретение относится к измерительной и вычислительной технике и может быть использовано, в частности, в преобразователях напряжения в код по- следовательного приближения.

Известен блок управления преобразователя напряжения в код последовательного приближения, содержащий генератор сигналов, распределитель сиг- .налов и два триггера в каждом разряде, выход генератора сигналов соединен со входом распределителя сигналов, во всех разрядах входы сброса в ноль, входы, синхронизации и первые входы установки в единицу триггеров сое- 15 динены с выходами распределителя сигНсшов, соответственно, вторые входы установки в единицу первого и второго триггеров соединены с шинами прямого и инверсного выходов бло-20 ка сравнения, прямой выход первого триггера соединен с третьим входом установки в единицу второго триггера, прямой выход второго триггера соединен с третьим входом установки, 2э в единицу первого триггера 13 .

Вследствие раздельного выполнения распределителя сигналов, который обеспечийает также распределение тактов работы устройства, и информацион-30

ных регистров на триггерах устройство сложно в изготовлении и требует, значительных затрат оборудования.

Известен блок управления преобразователя напряжения в код последовательного приближения, содержащий генератор сигналов, первый выход которого соединен со входом синхронизации первого и второго триггеров каждого разряда, второй выход - со входом синхронизации третьего триггера -каждого разряда, вход сброса триггеров соединен с шиной сброса , пёрвы« вход установки в единицу первого и второго триггеров соединен соответственно с шинами прямого и инверсного сигналов сравнения, второй вход установки в единицу - с выходом элемента И данного разряда, первый выход первого и второго триггеров подключен к шинам уп-; равления цифро-аналоговым преобразователем, второй выход первого триггера соединен с первым входом установки третьего триггера данного разряда, элементы И всех разрядов соединены последовательно 2 .

В этом устройстве на общих схемных элементах реализуются функции информационных регистров и распредеителя тактов работы, такое совмещеие функций дает уменьшение затрат оборудования по сравнению с затратаи оборудования в известных устройствах с выполнением функций информационных регистров и распределителя тактов работы на различных схемных элементах.

Однако устройство сложно в изготовлении, так как в нем применены двухтактные триггера, каждый из которых выполняется из двух однотактных триггеров. Общее число триггеров в п-разрядном устройстве составляет 4п. Кроме того, в устройстве используется п элементов И-НЕ и п элементов И. Из-за применения большого числа триггеров изготовление устройства сложно и требует значительных затрат оборудования.

Цель изобретения - сокращение ап- паратурных затрат.

Цель достигается тем, что в блок управления преобразователя напряжения в код последовательного приближения, содержащий генератор сигналов, первый выход которого соединен со входом синхронизации первого и второго триггеров.каждого разряда, второй выход -.со входом синхронизации третьего триггера каждого разряда, вход сброса триггеров соединен с шиной сброса, первый вход установки в единицу первого и второго триггеров соединен .соответственно с шинами прямого и инверсного сигналов сравнения, второй вход установки в единицу - с выходом элемента И данного разряда, первый выход первого и второго триггеров подключен к шинам управления цифро-аналоговым преобразователем, второй выход первого триггера соединен с первьзм входом установки третьего триггера данного разряда, элементы И всех разрядов соединены последовательно, в каждом разряде второй выход второго триггерасоединен со вторым входом установки третьего триггера данного разряда, прямой выход которого соединен с третьим входом установки в единицу первого и второго триггеров следующего разряда, инверсный выход третьего триггера соединен со вторым входом элемента И. данного разряда, прямой выход третьего триггера последнего разряда соединен со входом установки в ноль первого и второго триггеров всех разрядов.

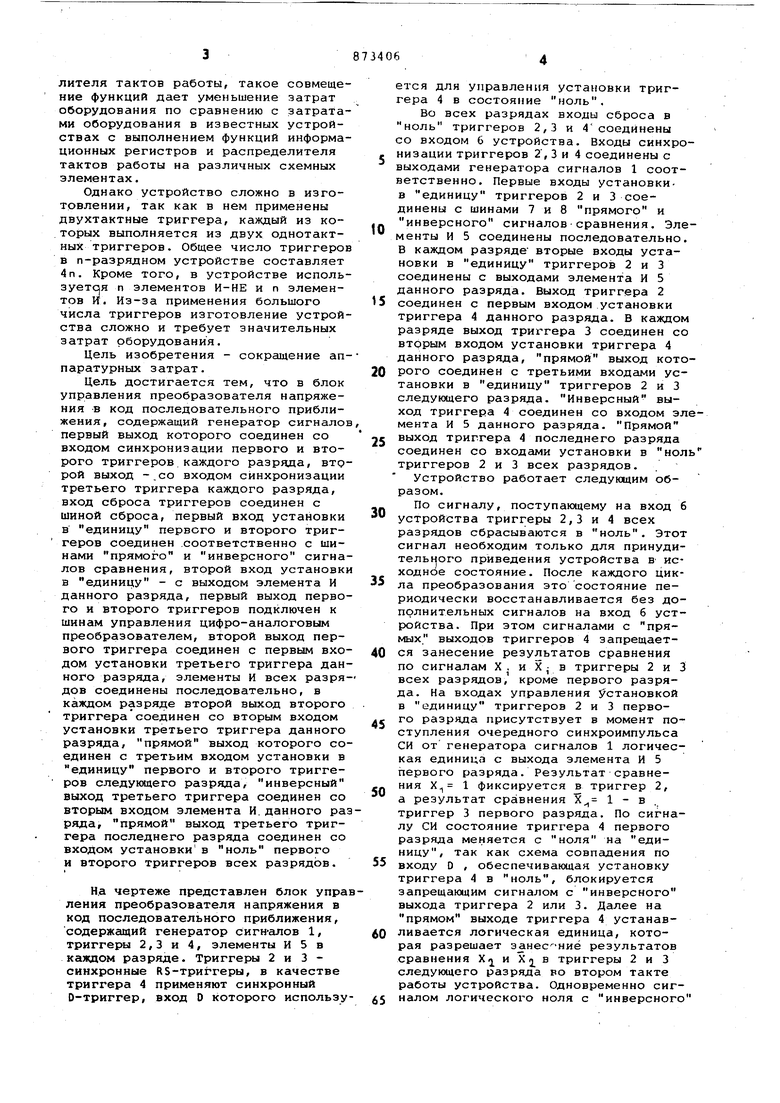

Н.а чертеже представлен блок управления преобразователя напряжения в код последовательного приближения, содержащий генератор сигн-алов 1, триггеры 2,3 и 4, элементы И 5 в каждом разряде. Триггеры 2 и 3 синхронные RS-триггеры, в качестве триггера 4 применяют синхронный D-триггер, вход D которого используется для управления установки триггера 4 в состояние ноль.

Во всех разрядах входы сброса в ноль триггеров 2,3 и 4соединены со входом 6 устройства. Входы синхронизации триггеров 2, 3 и 4 соединены с выходами генератора сигналов 1 соответственно. Первые входы установкив единицу триггеров 2 и 3 соединены с шинами 7 и 8 прямого и инверсного сигналов сравнения. Элементы И 5 соединены последовательно В каждом разряде вторые входы установки в единицу триггеров 2 и 3 соединены с выходами элемента И 5 данного разряда. Выход триггера 2 соединен с первым входом установки триггера 4 данного разряда. В каждом разряде выход трихтера 3 соединен со вторым входом установки триггера 4 данного разряда, прямой выход которого соединен с третьими входами установки в единицу триггеров 2 и 3 следующего разряда. Инверсный выход триггера 4 соединен со входом элмента И 5 данного разряда. Прямой выход триггера 4 последнего разряда соединен со входами установки в нол триггеров 2 и 3 всех разрядов.

Устройство работает следующим образом.

По сигналу, поступающему на вход б устройства триггеры 2,3 и 4 всех разрядов сбрасываются в ноль. Этот сигнал необходим только для принудительного приведения устройства В исходное состояние. После каждого цикла преобразования это состояние периодически восстанавливается без дополнительных сигналов на вход 6 устройства. При этом сигналами с прямых выходов триггеров 4 запрещается занесение результатов сравнения по сигналам X , и X в триггеры 2 и 3 всех разрядов, кроме первого разряда. На входах управления 5 становкой в единицу триггеров 2 и 3 первого разряда присутствует в момент поступления очередного синхроимпульса СИ от генератора сигналов 1 логическая единица с выхода элемента И 5 первого разряда. Результат сравнения Х 1 фиксируется в триггер 2, а результат сравнения Х 1 - в . триггер 3 первого разряда. По сигналу СИ состояние триггера 4 первого разряда меняется с ноля на единицу, так как схема совпадения по входу D , обеспечивающая установку триггера 4 в ноль, блокируется запрещающим сигналом с инверсного выхода триггера 2 или 3. Далее на прямом выходе триггера 4 устанавливается логическая единица, которая разрешает занес -ниё результатов сравнения Х и К/ в триггеры 2 и 3 следующего разряда во втором такте работы устройства. Одновременно сигналом логического ноля с инверсного выхода триггера 4 первого разряда через элемент И 5 первого разряда з прещается повторное изменение состо яния триггеров 2 и 3 первого разряд Аналогичным образом происходит разрешение занесения результатов сравн ния Х и X(ie2,n) в триггеры 2 и 3 следующих разрядов и запрещение повторного изменения состояния триг геров 2 и 3 предшествующих разрядов После занесения результатов сравнения Х„ и Х„ в триггеры 2 и 3 послед него р азряда п сигнал логической еди ницы с , прямого выхода триггера 4 последнего разряда поступает на зходы установки в .ноль триггеров 2 и 3 всех разрядов. В момент прихода очередного сигнала СИ триггеры 2 и 3 всех разрядов переводятся в состояние ноль. По сигналу СИ это состояние фиксируется триггерами 4 всех разрядов. Устройство вновь переходит в исходное состояние. Ему , соответствует такт определения старшего разряда кода преобразуемого напряжения. При необходимости управления состоянием триггера 4 может быть выполнено по сигналам с прямых выходов триггеров 2 и 3. В этом случае по входу О реализуется схема собирания, вход D используется для управления установкой триггера 4 в состояние ноль. При использовании в качестве триггера 4 синхронного ftSтриггера управление по входам установки R и S осуществляется по соотношениям ((1-J+ Q-j 5; -5j-CH /5о Qa сигналы с пря мых и инверсных выходов триггеров 2 и 3. . : в устройстве используется Зп одно тактных триггеров и п элементоб И. Применение в каждом разряде устройства трех однотактных триггеров в «есто двух двухтактных триггеров сокращает затраты оборудования на25%. Уменьшение числа схемных элементов упрощает схему устройства и повышает ее надежность. В преобразователе напряжения в код с предлагаемым блоком управления повышается быстродействие, так как в данном устройстве сигналы на входы ЦАП поступают с выходов 2 и 3, меняющих свое сос: ояние по переднему фронту сигнала СИ. В известном устройстве сигналы на входы ДАП поступают с выходов второй ступени двухтактных триггеров 2 и 3, которые меняют свое состояние по сигнёшам СИ. Последнее обстоятельство увеличивает каждый такт преобразования и звестного устройства на длительность синхимпульса СИ - 2-4f, где f - среднее время задержки элементов второй ступени двухтактных триггеров. Формула изобретения Блок управления преобразователя напряжения в код последовательного приближения, содержащий генератор сигналов, первый выход которого соединен со входом синхронизации первого и второго триггеров каждого разряда, второй выход - со входом синхронизации третьего триггера каждого разряда, вход сброса триггеров соединен с шиной сброса, первый вход установки в единицу первого и второго триггеров соединен соответственно с шинами прямого и инверсионного сигналов сравнения, второй вход установки в единицу - с выходом элемента И данного разряда, первый выход первого и второго триггеров подключен к шинам управления ци фро-ангшоговым преобразователем, второй выход первого триггера соединен с первым входом установки третьего триггера данного разряда, элементы И всех разрядов соединены последовательно, отличающийся тем, что, с целью сокращения аппаратурных затрат, в каждом разряде второй выход второго триггера соединен со вторым входом установки третьего триггера данного разряда, прямой выход которого соединен с третьим входом установки в единицу первого и второго триггеров следующего разряда, инверсный вклход третьего триггера соединен со вторым входом элемента И данного разряда, прямой выход третьего триггера последнего разряда соединен со входом установки в ноль первого и второго триггеров всех разрядов. Источники информации, принятые во внимание при экспертизе li Патент ФРГ 1129716, кл.О 06 F 13/00, 1962. 2. Авторское свидетельство СССР по заявке 2697549/21, кл. Н 03 К 13/17, 1978.(прототип ).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения в код последовательного приближения | 1978 |

|

SU790290A1 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| МИКРОПРОГРАММНЫЙ ПРОЦЕССОР | 1988 |

|

SU1618169A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1720160A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| СПОСОБ ПЕРЕДАЧИ ДВОИЧНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2453906C2 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

Авторы

Даты

1981-10-15—Публикация

1979-12-03—Подача