(5) КОММУТИРУЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный резервированный коммутатор | 1989 |

|

SU1737723A1 |

| Устройство для отображения информации | 1986 |

|

SU1410097A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Микропрограммное устройство управления | 1981 |

|

SU959078A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ГАЗОРАЗРЯДНОЙ ИНДИКАТОРНОЙ ПАНЕЛИ | 1992 |

|

RU2042216C1 |

| Устройство для анализа частоты использования блоков информации в вычислительных комплексах | 1990 |

|

SU1793442A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ И ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 1992 |

|

RU2101781C1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

Изобретение относится к автоматик и коммутационной технике. Известны коммутирующие устройства, содержащие матричный коммутатор, счетчик, дешифратор, блоки памяти, регистры Недостаток известного устройства низкая надежность функционирования. Наиболее близким к предлагаемому по технической сущности является ком мутирующее устройство, содержащее матричный коммутатор, выходы которого соединены с выходными шинами, а. каждая группа управляющих входов под ключена к выходам соответствующего дешифратора адресов выходных шин, входы которого соединены с информационными входами одноименного блока памяти и выходами одноименного регис ра, первая и вторая группы.информационных входов которого подключены соответственно к первой группе адрес ных шин и выходам соответствующего блока памяти, а управляющий вход соединен с одноименной основной управляющей шиной, при этом вторая группа адресных шин подключена к разрядным входам основного счетчика, счетный вход которого соединен с дополнительной управляющей шиной, а выходы через дешифратор адресов блоков памяти - с адресными входами блоков памяти 2. К недостатку известного устройства относится низкая надежность функционирования. Цель изобретения - повышение надежности коммутирующего устройства. Указанная цель достигается тем, что вкоммутирующее устройство, со держащее матричный коммутатор, выходы которого соединены с выходными шинами, а каждая группа управляющих входов подключена к выходам соответствующего дешифратора адресов выходных шин, входы которого соединены с информационными входами одноименного блока памяти и выходами одноимен393261

ного регистра, первая и вторая группы информационных входов которого подключены соответственно к первой группе адресных шин и выходам соответствующего блока памяти, а управ- $ ляющий вход соединен с одноименной основной управляющей шиной, при этом вторая группй адресных шин подключена к разрядным входам основного счетчика, счетный вход которого соединен ю с дополнительной управляющей шиной, а выходы через дешифратор адресов блоков памяти - с адресными входа)ми блоков памяти, введены дополнительные счетчики, дешифраторы адре- 15 сов входных шин и линейные коммутаторы, информационные входы которых соединены с информационными входными шинами , выходы - с информационными входами матричного коммутатора,а управляющие 20 входы каждого из них подключены к выходам COOTветствущего дешифратора адресов информационных входных шин, входы каждого из которых подключены к выходам одноименного дополнительного 2$ счетчика, счетный вход которого соединен с выходом дополнительного разряда одноименного регистра, разрядные входы - с третьей группой адресных шин, а управляющий вход подключен к соответствующей шине дополнительной группы.

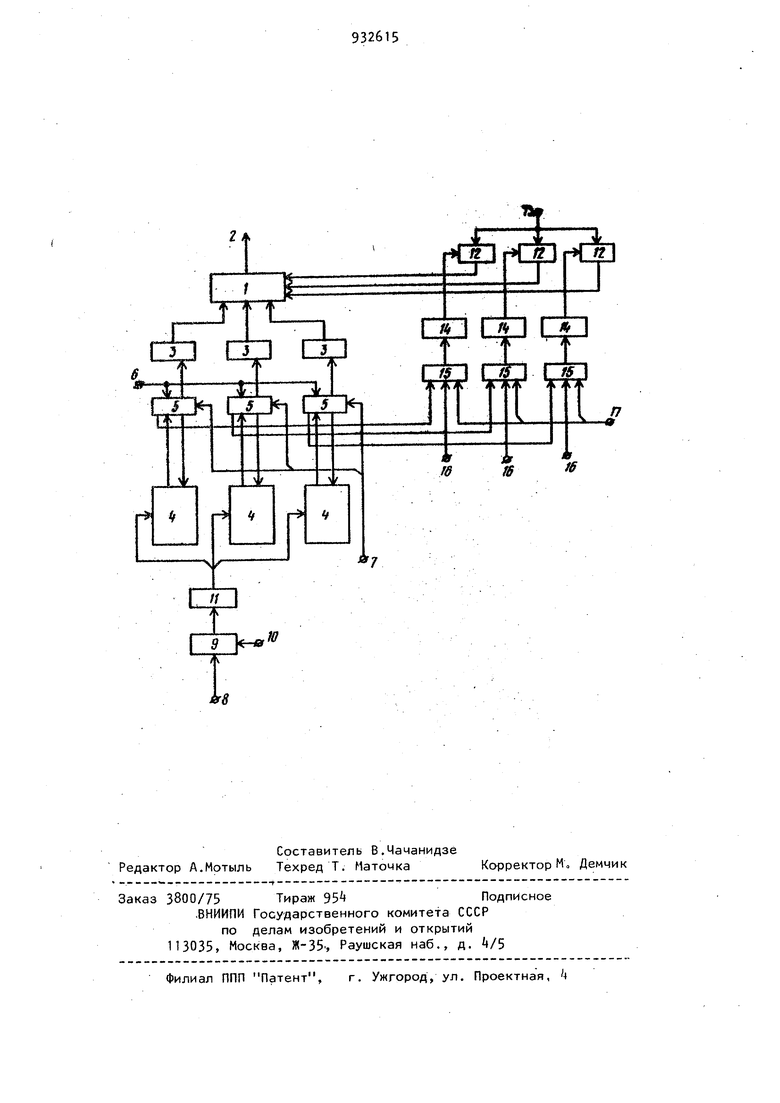

На чертеже приведена блок-схема коммутирующего устройства.

Устройство содержит матричный ком-35 мутатор 1, выходы которого соединены с выходными шинами 2, а каждая группа управляющих входов подключена к выходам соответствующего дешифратора 3 адресов выходных шин 2, входы которого соединены с информационными входами одноименного блока i памяти и выходами одноименного регистра 5, первая и вторая группы информационных входов которого подключены соответ- ственно к группе адресных шин 6 и выходам соответствующего блока k памяти, а управляющий вход соединен с одноимённой управляющей шиной 7; группа адресных шин 8 подключена к 50 разрядным входам счетчика 9, сметный вход которого соединен с управляющей шиной 10, а выходы через дешифратор 11 адресов блоков k памяти с адресными входами блоков k памяти; 55 линейные коммутаторы 12, информационные входы которых соединены с информационными входными шинами 13,вы54

ходы - с информационными входами матричного коммутатора 1, а управляющие входы каждого из них подключены к выходам соответствующего дешифратора 1А адресов информационных входных шин 13, входы каждого из которых подключены к выходам одноименного счетчика 15, счетный вход которого соединен с выходом дополнительного разряда одноименного регистра 5, разрядные входы - с группой адресных шин 16, а управляющий вход подключен к соответствующей управляющей шине 17 дополнительной группы.

Коммутирующее устройство функционирует следующим образом.

Перед началом работы в блоках 4 памяти через адресные шины 6 и регистры, 5 осуществляется ввод программы коммутации, состоящей из адресов выходных шин 2. Каждая ячейка блока |памяти содержит в коде адреса выходн ;шин 2 дополнительный разряд.Адресация ячеек блоков памяти производится с помощью дешифратора 11 и счетчика 9, в который или предварительно вводится адрес через адресные шины 8, или увеличивается значение счетчика 9 на единицу сигналом, подаваемым по управляющей шине 10. В счетчики 15 вводятся через адресные шины 16 начальные коды адресов информационных входных шин 13, а в счетчик 9 засылается начальный код адреса ячеек блоков k памяти.

Затем по сигналу управления производится одновременное считывание адресов выходных шин 2 из ячеек блоков памяти, соответствующих адресу счетчика 9, и осуществляется подключение тех информационных входных шин 13 через линейные коммутаторы 12 к матричному коммутатору 1, адреса которых хранятся в счетчиках 15. Считанные коды адресов выходных шин 2 поступают в регистры 5 и через дешифраторы 3 управляют подключением выходов линейных коммутаторов 12 с помощью матричного коммутатора 1 к требуемым выходным шинам 2. Если дополнительный разряд кода адреса выходных шин 2, хранящийся в регистре 5, равен нулю, то код адреса в счетчике 15 не изменяется; если дополнительный разряд равен единице, то к началу считывания адресов выходных шин 2 следующих ячеек блоков А памяти код адреса в счетчике 15 увеличивается на единицу. Таким образом, введение дополнительных счетчиков, дешифраторов и линейных коммутаторов позволяет повысить надежность предлагаемого коммутирующего устройства по сравнению с известным. Формула изобретения Коммутирующее устройство, содержащее матричный коммутатор, выходы кото рого соединены с выходными шинами, а каждая группа управляющих входов подключена к выходам соответствующего дешифратора адресов выходных шин,входы которого соединены с информационными входами одноименного блока памяти и выходами одноименного регистра, первая и вторая группы информационных входов которого подключены соответственно к первой группе адресных шин и выходам соответствующего блока памя,|ги, а управляющий вход соединен с одноименной основной управляющей шиной при этом вторая группа адресных шин подключена к разрядным входам основного счетчика, счетный вход которого соединен с дополнительной уп1равляющеи шиной, а выходы через дешифратор адресов блоков памяти - с адресными в(одами блоков памяти, отличающееся тем, что, с целью повышения надежности, в него введены дополнительные счетчики, дешифраторы адресов входных шин и линейные коммутаторы, информационные входы которых соединены с информационными входными шинами, выходы - с информационными входами матричного коммут трра, а управляющие входы каждого из них подключены к выходам соответствующего дешифратора адресов информационных входных шин, входы каждого из которых подключены к выходам одноименного дополнительного счетчика, счетный вход которого соединен с выходом дополнительного разряда одноименного регистра, разрядные входы с третьей группой адресных шин, а управляющий вход подключен к соответствующей управляющей шине дополнительной группы. Источники информации, принятые во внимание при экспертизе 1.Патент Великобритании If 1392176, кл. G А, 1975. 2.Авторское свидетельство СССР по заявке № 2822786,кл.Н 03 К 17/0, 1380 (прототип).

Авторы

Даты

1982-05-30—Публикация

1980-10-01—Подача