1

Изобретение относится к запоминающим устройствам и может быть использовано в Ka4edTBe основной и вспомогательной памяти в вычислительных системах.

Известно запоминающее устройство, содержащее накопитель, блок управления, кодовые регистры, блок декодирования, схему равенства кодов и позволяет работать с теми ячейками накопителя, которые дают отказ в одном и более разрядах 1.

Недостатком этого устройства является невысокое быстродействие.

Наиболее близким техническим решением к данному изобретению является згшоминающее устройство,с самоконтролем, содержащее накопитель, выход; которого через блок декодирования)с0единен со входом блока управления, с первым и вторым регистрами чио1а, схему равенства кодов, у которой выход соединен со входом блока управления, а входы - с выходами первого и второго регистров числа, причем выходы этих регистров через группу элементов ИЛИ подключены к выходной шине, к блоку декодирования, группу элементов И входы которой соединены с выходом блока упрайт

ления и выходом второго регистра числа, блок управления,.выход кото , рого подключен ко входгий накопителя, первого и второго регистров числа 2 .

Недостатками этого устройства являются небольшое быстродействие и мсшая обнаруживающая и ко зректирующая способность, что снижает на10дежность устройства.

Цель изобретения - повышение feicTродействия и надежности устройства.

Поставленная цель достигается тем, что в запоминающее устройство

15 с самоконтролем, содержащее накопитель, регистры числа, первую схему сравнения, блок коррекции, элементы ИЛИ и блок управления, причем вход накопителя подключен к первому вы20ходу первого регистра числа, первым входам элементов ИЛИ и входу блока коррекции в выход - к первому входу первого регистра числа и входу второго регистра числа, выходы бло25ка коррекции соединены соответственно с первым входом первой схемы сравнения и вторыми входами элементов ИЛИ, управляющие входы Элементов ИЛИ и регистров числа подключены к одним из выходов блока управ30

ения, один из входов которого соеинек . с ныходом-первой схемы сравнения, введены дешифратор и вторая схема сравнения, входы которой подключены соответственно к первому выходу первого регистра числа и вы- ходу второго регистра числа, а выход соединен со вторым входом первой схекод сравнения, вход и выход дешифратора подключены соответственно ко второму выходу и второму входу пер- .вого регистра числа, управляющий вход дешифратора и управляю111ие выходы второй схемы сравнения и дешифратора соединены соответственно с другими выходом и входами блока управления.

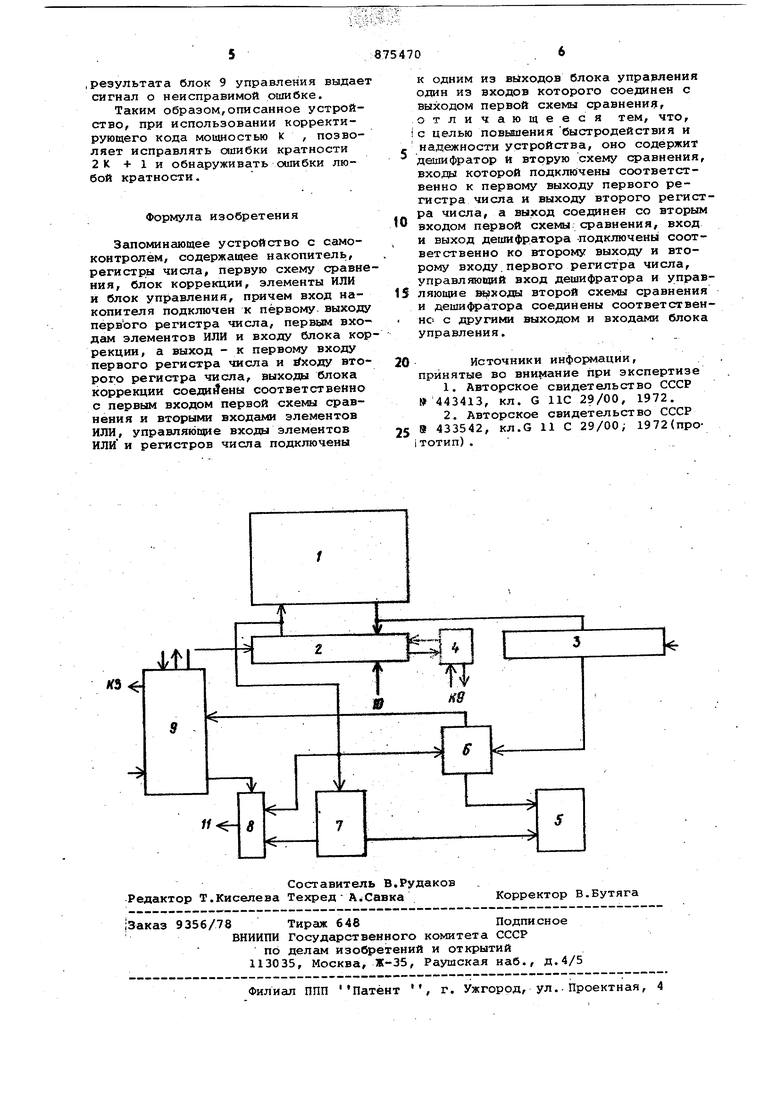

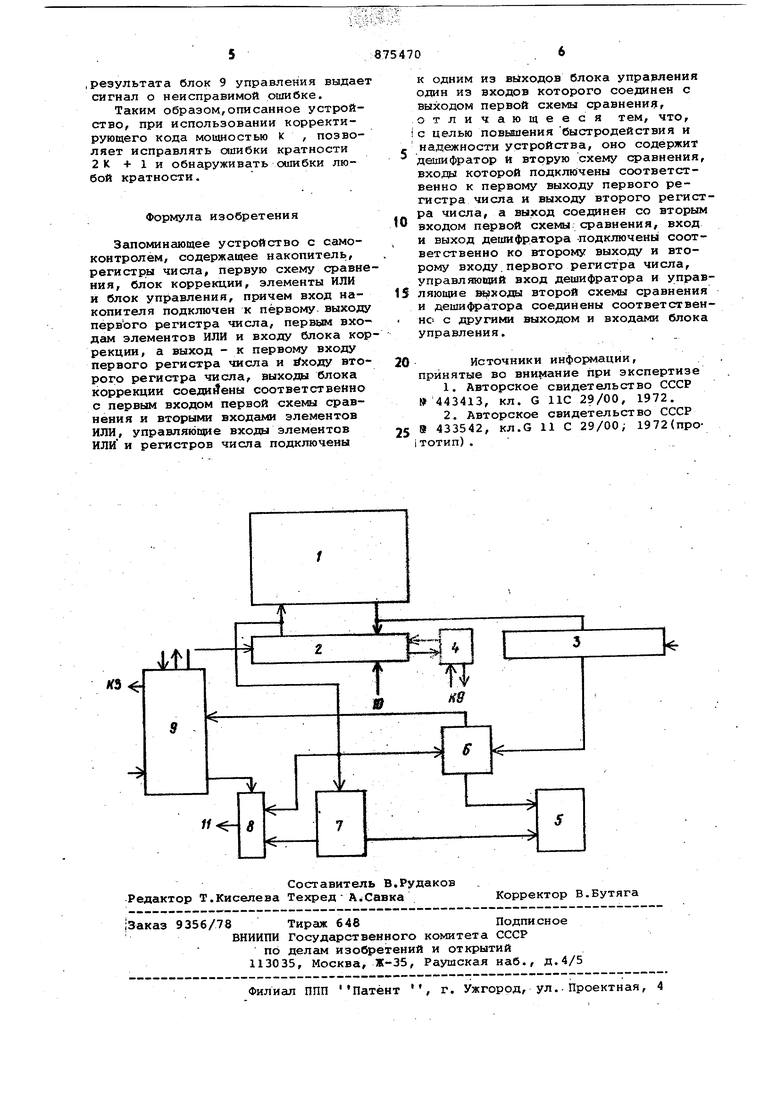

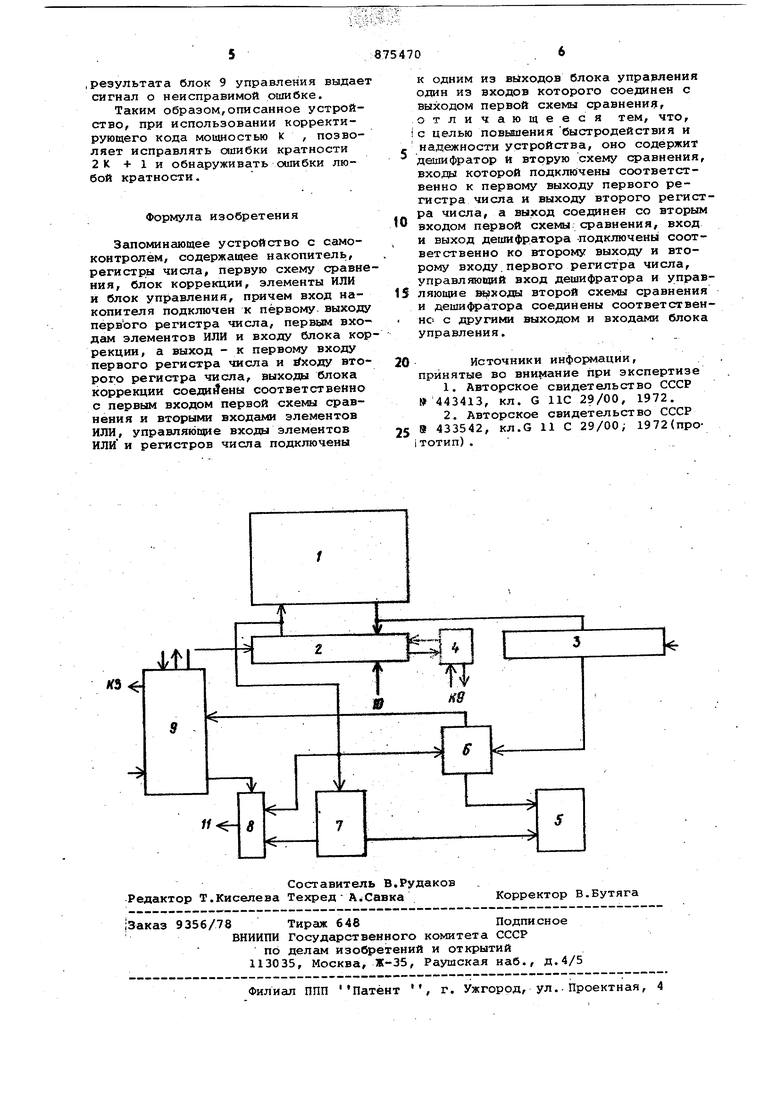

На чертеже изображена функциональ- 5 ная схема запоминающего устройства с самоконтролем.

Устройство содержит накопитель 1, первый 2 и второй 3 регистры числа, дешифратор 4, первую 5 и вторую б20

схемы сравнения, осуществляющие соответственно функции определения равенства кодов и поразрядного сравнения кодов, блок 7 коррекции,группу элементов ИЛИ 8, блок 9 управления. 25 Входы 10 регистра 2 и выходы 11 элементов ИЛИ 8 является соответственно входами и выходами устройств. Два разряда в регистре 2 и в накопителе 1 являются маркерными. Вход накопи- ... теля 1 подключен к первому выходу регистра 2, первым входам элементов ИЛИ 8 и вхйду блока 7, а выход - к первому входу регистра 2 и входу регистра 3. Выходы блока 7 соедине- кы соответственно с первым входом

cxeNsi 5 сравнения и вторыми входами элементов ИЛИ в. Управляющие входы элементов ИЛИ 8 и регистров 2 и 3 подключены к одним из выходов блока 9, одаи из входов которого соединен 40 с выходом схекк 5 сравнения. Входы cxeivfiii 6 сравнения подключены соответственно к первому выходу регистра 2 и выходу регистра 3, а выход соединен со вторым входом схемы 5

сравнения. Вход и выход яешкфратора 4 подключены .соответственно ко второму выхода и второму входу регистра 2. Управляющий вход дешифратора 4 и управляющие выходы схегал сп 6 (равнения и дешифратора 4 соедивены соответственно с другими -выходом и входами блока 9.

Устройство работает следующим образом.

(lycTb используется корректируюи|ий код мощности к , под которой подразумевается способность корректирующего кода исправлять оиибки от 1 до К .

Число, подлежащее записи в нако- 40 питель 1 и предварительно закодированное, поступает на первый регистр числа 2. В режиме контрольной записи код с первого регистра исла 2 записывается в накопитель 1 и счи- 5

тывается во второй регистр числа 3. Содержимое второго 3 и первого 2 регистров исла сравнивается в 6 сравнения. Если коды равны, в маркерные разряды первого регистра числа 2 дешифратор 4 записывает 00 и 01 - в случае, если кратность ошибки не превышает К . Если же кратность ошибки больше К то в маркерные разряды запишется код 10 . В первых двух случаях в накопитель 1 будет записан прямой код подлежащего записи числа, а в третьем случае - обратный код, причем маркерные разряды всегда записываются в прямом коде. На этом процесс записи завершается.

При считывании информации из ячейки накопителя 1, к которой происходит обращение, число поступает в первый регистр числа 2. Дешифратор 4 анализирует состояние маркерных разрядов и если в них код 00 , содержимое первого регистра числа 2 через элементы ИЛИ 8 передается на выходы 11 (это означает, что число не содержит ошибок

Если в маркерных разрядах - код 01, содержимое первого регистра числа 2 передается в блок 7, где производится декодирование числа, в результате которого определяются потери подлежащих коррекции разрядов, значения этих разрядов корректируются и -блок 9 управления разрешает выдачу числа через элементы ИЛИ 8 на выходы 11 (это соответствует случаю,когда кратность ошибки не превышает К . Если в маркерных разрядах-код 10 , содержимое первого регистра числа с его инверсного выхода поступает в блок 7, где производится декодирование и коррекция кода, кроме того, содержимое первого регистра 2 числа с его инверсного выхода записывается в ту же ячейку накопителя 1, к которой происходит обращение, и считывается на второй регистр 3 числа. Содержимое первого регистра 2 числа и обратный код содержимого второго регистра 3 числа поступают в схему 6 сравнения, которая поразрядно сравнивает эти коды. Номера разрядов, значение которых не совпадает, являются отказавшими. Таким -образом схема б сравнения определяет множество отказавших разрядов, которое поступает в схему 5 сравнения, куда поступаиот и номера сяиибочных разрядов, определенные при декодировании в блоке 7. Если номера являются подмножеством множества номеров отказавших разрядов, исправление произведено верно и бло 9 управления разрешит выдачу откорртированного кода с блока 7 на выходы 11, а в - случае отрицательного

.результата блок 9 управления выдает сигнал о неисправимой ошибке.

Таким образом,описанное устройство, при использовании корректирующего кода мощностью К , позволяет исправлять ошибки кратности 2 К + 1 и обнаруживать ошибки любой кратности.

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее накопитель, регистры числа, первую схему сравнения, блок коррекции, элементы ИЛИ и блок управления, причем вход накопителя подключен к первому, выходу первого регистра числа, первым вхо дам элементов ИЛИ и входу блока коррекция, а выход - к первому входу первого регистра числа и ходу второго регистра числа, выходы блока коррекции соеди1}ены соответственно с первым входом первой схемы сравнения и вторыми входами элементов ИЛИ, управляющие входы элементов ИЛИ и регистров числа подключены

к одним из вйходов блока управления один из входов которого соединен с выходом первой схемы сравнение, отличающееся тем, что, с целью повышения быстродействия и надежности устройства, оно содержит дешифратор и вторую схему сравнения, входы которой подключены соответственно к первому выходу первого регистра числа и выходу второго регистра числа, а выход соединен со вторым входом первой схемы сравнения, вход и выход дешифратора подключены соответственно ко второму выходу и второму входу, первого регист ра числа, управляющий вход дешифратора и управляющие второй схемы сравнения н дешифратора соединены соответственно с другими выходом и входами блока управления.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР 443413, кл. G НС 29/00, 1972.

2.Авторское свидетельство СССР 8 433542, кл.С 11 С 29/00; 1972(прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1149318A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1381605A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1152042A1 |

| Запоминающее устройство с исправлением ошибок | 1983 |

|

SU1133624A1 |

| Запоминающее устройство с обнаружением и коррекцией ошибок | 1983 |

|

SU1138836A1 |

| Запоминающее устройство с самоконтролем | 1977 |

|

SU736177A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1374286A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

iti

««

т

п

Н8

Авторы

Даты

1981-10-23—Публикация

1980-02-14—Подача