Изобретение относится к вычислительной технике, в частности к запоминающим устройствам (ЗУ), выпол - ненныг-1 на полупроводниковых динамических элементах..

Цель изобретения - повышение бы- стродействия устройства за счет совмещения такта записи скорректированной информации с тактом регенерации- считывания,-

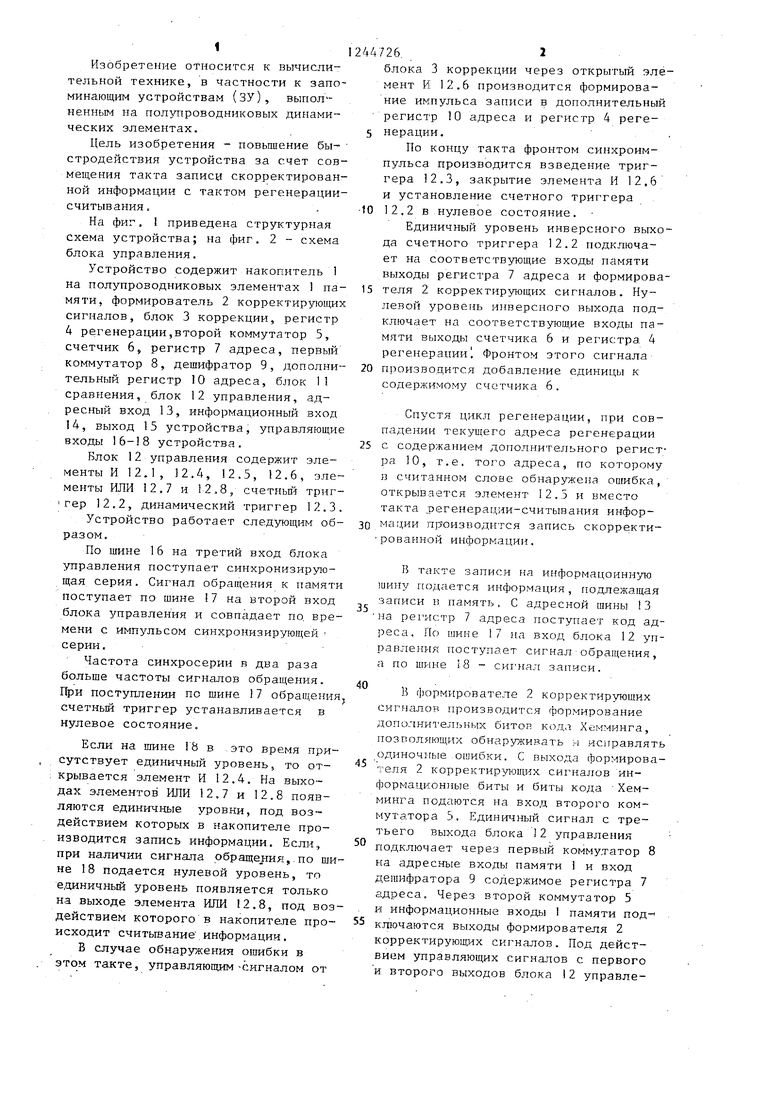

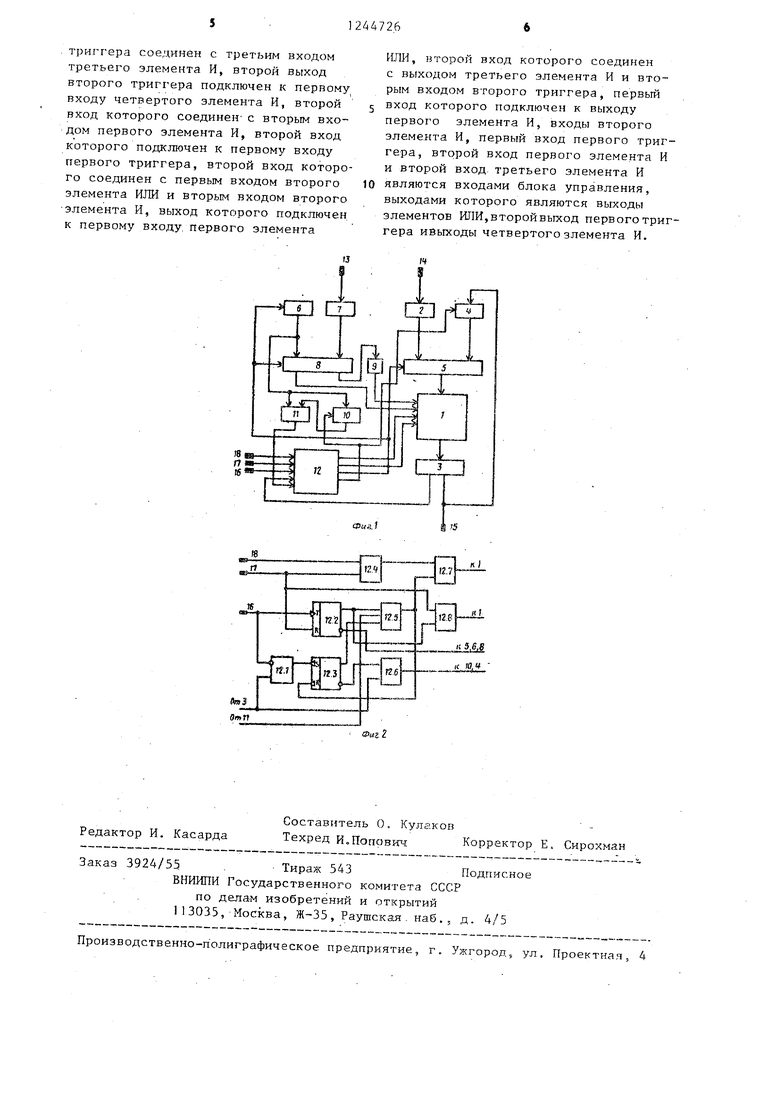

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - схема блока управления.

Устройство содержит накопитель 1 на полупроводниковых элементах 1 па- мяти. формирователь 2 корректирующих сигналов, блок 3 коррекции, регистр 4 регенерации,второй коммутатор 5, счетчик 6, регистр 7 адреса, первый коммутатор 8, дешифратор 9, дополни- тельный регистр 10 адреса, блок П сравнения, блок 12 управления, адресный вход 13, информационный вход 4, выход 15 устройства, управляющие входы 16-18 устройства.

Блок 12 управления содержит элементы И 12.1, 12.4, 2.5, 12.6, элементы ИЛИ 12.7 и 12,8, счетньй триг- гер 12.2, динамический триггер 12.3

Устройство работает следующим об- разом.

По шине 16 на третий вход блока управления поступает синхронизирующая серия. Сигнал обращения к памяти поступает по шине 7 на второй вход блока управления и совпадает по. вре мени с импульсом синхронизирующей серии.

Частота синхросерии в два раза больше частоты сигналов обращения. При поступлении по шине 17 обращения сч.етньш триггер устанаазливается в нулевое состояние.

Если на шине 8 в это время присутствует единичный уровень, то от- крывается элемент И 12.4. На выходах элементов ИЛИ 12.7 и 12.8 появляются единичные уровни, под воз-действием которых в накопителе производится запись информации. Если, при наличии сигнала обращения,, по шине 18 подается нулевой уровень, то е.оиничный уровень появляется только на выходе элемента ИЛИ 12.8, под воздействием которого в накопителе про- исходит считьгоание информации.

В случае обнаружения ошибки в этом такте, управляющим-сигналом от

j

0

5 0 5

о

о

0 5

5

726.2

блока 3 коррекции через открытый элемент И 12.6 производится формирование им:пульса записи в дополнительный регистр 10 адреса и регистр 4 регенерации.

По концу такта фронтом синхроимпульса производится взведение триггера 12.3, закрытие элемента И 12.6 и установление счетного триггера 12,2 в нулевое состояние.

Единичный уровень инверсного выхода счетного триггера 12.2 подключает на соответствующие входы памяти выходы регистра 7 адреса и формирователя 2 корректирующих сигналов. Нулевой уровень инверсного выхода подключает на соответствующие входы памяти выходы счетчика 6 и регистра 4 регенерапии Фронтом этого сигнала производится добавление единицы к содержимому счетчика 6.

Спустя цикл регенерации, при совпадении текуишго адреса регенерации с содержанием дополнительного регистра 10, т.е. того адреса, по которому в считанном слоне обнаружена ошибка, открывается элемент 12.5 и вместо такта .регенерации-считывания информации производрЕТСя запись скорректи- ровар ной информации.

В такте записи на информацоинную шину подается информация, подлежащая записи н память „ С адресной шины 13 на регистр 7 адреса поступает код адреса, шине 17 на вход блока 12 уп- paвлeн я поступает сигнал обращения , а по шине 18 - сигнал записи,

В формирователе 2 корректирующих сигналов производится формирование дополни1 ельнь Х битов кода Хемминга, позроляющих обнаруживать и исправлять одиночзгые ошибки. С выхода формирователя 2 корректирующих сигналов ин- форма.цконцые биты и биты кода Хем- минга подаются на вход второго коммутатора 5. Единичный сигнал с третьего выхода блока i 2 управления подключает через первый коммутатор 8 на адресные входы памяти и вход дешифратора 9 содержимое регистра 7 адреса. Через второй коммутатор 5 и информационные входы 1 памяти под- ключаются выходы формирователя 2 корректирую1дих сигналов. Под действием управляющих сигналов с первого и второго выходов блока 12 управления в накопителе 1 производится запись информационных битов и дополнительных битов кода Хемминга.

В такте считывания с адресной шины 13 поступает код адреса, с шины 17 - сигнал обращения, с шины 18 - сигнал считывания. Работа адресной .части аналогична циклу записи. Под воздействием управляющего сигнала с второго выхода блока 12 управления в накопителе 1 происходит считывание информации по адресу, принятому на регистр 7 адреса. Считанные биты информации и биты кода Хемминга поступают в блок 3 коррекции информации, где, в случае обнаружения одиночной ошибки, происходит ее исправление и выдача на выходную информационную шину 13. Одновременно эта информация заносится на регистр 4 регенерации, если последний в это время не занят.

Занесение скорректированной информации и адреса,по которому эта информация хранится в памяти, производится под воздействием сигнала, поступающего по четвертому управляющему выходу блока 12 управления.

В следующем такте блок 12 управения нулевым уровнем на третьем ыходе подключает через первый коммуатор 8 на адресные входы накопитея I и входы дешифратора 9 содержиое счетчика 6. Под воздействием сигнала с второго выхода блока 12 управления происходит считывание из накопителя 1 информационных и контрольных битов в блок 3 коррекции. Если ранее в такте регенерации или в такте считывания по обращению была обнаружена ошибка, то при совпадении текущего адреса регенерации с адресом, записанным в дополнительном регистре 10, блок 11 сравнения выдает сигнал,по которому в этом такте происходит запись-регенерация скорректированной информации.

Если в процессе регенерации возникает несколько одиночных ошибок, то устройство фиксирует первую опшб- ку, исправляет ее через цикл регёне- . рации, а затем фиксирует следующую т.д.

ормула изобретения

1. Запоминающее устройство с самоконтролем, содержащее накопитель.

447264

регистр адреса, счетчик, дешифратор, первый коммутатор, формирователь корректирующих сигналов, второй коммутатор, блок коррекции, блок управле- 5 ния, причем один выход первого коммутатора соединен с первым входом накопителя , другой выход - с входом да-, шифратора, выход которого подключен к второму входу накопителя, первый 10 вход первого коммутатора соединен с выходом регистра адреса, вход которого является адресным входом устройства , выход счетчика соединен с вторым входом первого коммутатора, itep- 15 вый вход второго коммутатора соединен с выходом формирователя корректирующих сигналов, вход которого является информационным входом устройства, выход регистра регенерации 20 соединен с вторым входом второго коммутатора, выход которого подключен к третьему входу накопителя, выход которого соединен с входом блока коррекции, один выход которого подклю- 25 чен к первому входу регистра регенерации и является информационным выходом устройства, первьш, второй и третий входы блока управления являются управляющими вхоДами устройст- JQ ва, четвертый вход блока управления соединен с другим выходом блока коррекции, первый и второй выходы блока управления подключены к третьему и четвертому входг1м накопителя, третий выход блока управления подключен к третьим входам коммутаторов и входу счетчика, отличающееся тем, что, с целью повьппения быстродействия устройства, в него введены дополнительный регистр адреса и блок сравнения, причем выход счетчика подключен к первым входам блока сравнения и дополнительного регистра адреса, выход которого соединен с вторым входом блока сравнения, j которого подключен к пятому входу блока управления, четвертый выход которого соединен с вторым входом дополнительного регистра адреса и вторым входом регистра регенерации.

2. Устройство по п. 1j о т л и- чающееся тем, что блок управления содержит первый и второй триггеры, элементы И, элементы ИЛИ, при- 55 чем первьш выход первого Триггера соединен с первым входом третьего элемента с вторым входом второго элемента ИЛИ, первый выход второго

35

40

45

триг гера соединен с третьим входом третьего элемента И, второй выход второго триггера подключен к первому входу четвертого элемента И, второй вход которого соединен- с вторым входом первого элемента И, второй вход которого подключен к первому входу первого триггера, второй вход которого соединен с первым входом второго элемента ИЛИ и вторым входом второго -элемента И, выход которого подключен к первому входу первого элемента

ИПИ, второй вход которого соединен с выходом третьего элемента И и вторым входом второго триггера, первый

вход которого подключен к выходу первог о элемента И, входы второго элемента И, первый вход первого триггера, второй вход первого элемента И и второй вход третьего элемента И

являются входами блока управления, выходами которого являются выходы элементов ИПИ,второйвыход первого триггера ивыходы четвертого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1587600A2 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1325569A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Устройство для коррекции ошибок | 1987 |

|

SU1541677A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам на полупроводниковых динамических элементах. Целью изобретения является повьше- ние быстродействия за счет совмещения такта записи скорректированной информации с тактом регенерации - считывания. Устройство содержит накопитель, формирователь корректирующих сигналов, блок коррекции, регистр регенерации, коммутаторы, счетчик, регистр адреса, дешифратор, блок сравнения, блок управления, дополнительный регистр адреса.1 з.п. ф-лы, 2 ил. 4ib Ч N) Од

Редактор И. Касарда

Составитель О. Кулаков

Техред И.Попович Корректор Е. Сирохман

Заказ 3924/55 , Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, , Раушская. наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Авторское свидетельство СССР № 760194, кл | |||

| Солесос | 1922 |

|

SU29A1 |

| Интегратор расхода | 1960 |

|

SU133625A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-07-15—Публикация

1984-08-21—Подача