(54) УСТРОЙСТВО УПРАВЛЕНИЯ ОБРАЩЕНИЕМ К ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство сопряжения с памятью | 1980 |

|

SU983697A1 |

| Устройство приоритета | 1982 |

|

SU1020828A1 |

| Устройство приоритета | 1986 |

|

SU1319032A1 |

| Устройство управления обращением к памяти | 1984 |

|

SU1171801A1 |

| Устройство для опроса источников дискретных сообщений | 1986 |

|

SU1381524A1 |

| Многоканальное приоритетное устройство для динамической памяти | 1981 |

|

SU1003087A1 |

| Устройство для формирования сигнала прерывания | 1984 |

|

SU1241242A1 |

| Устройство циклического приоритета | 1990 |

|

SU1805468A1 |

| Устройство сопряжения | 1981 |

|

SU1121667A1 |

| Устройство для сопряжения двух ЦВМ с общей памятью | 1989 |

|

SU1661778A1 |

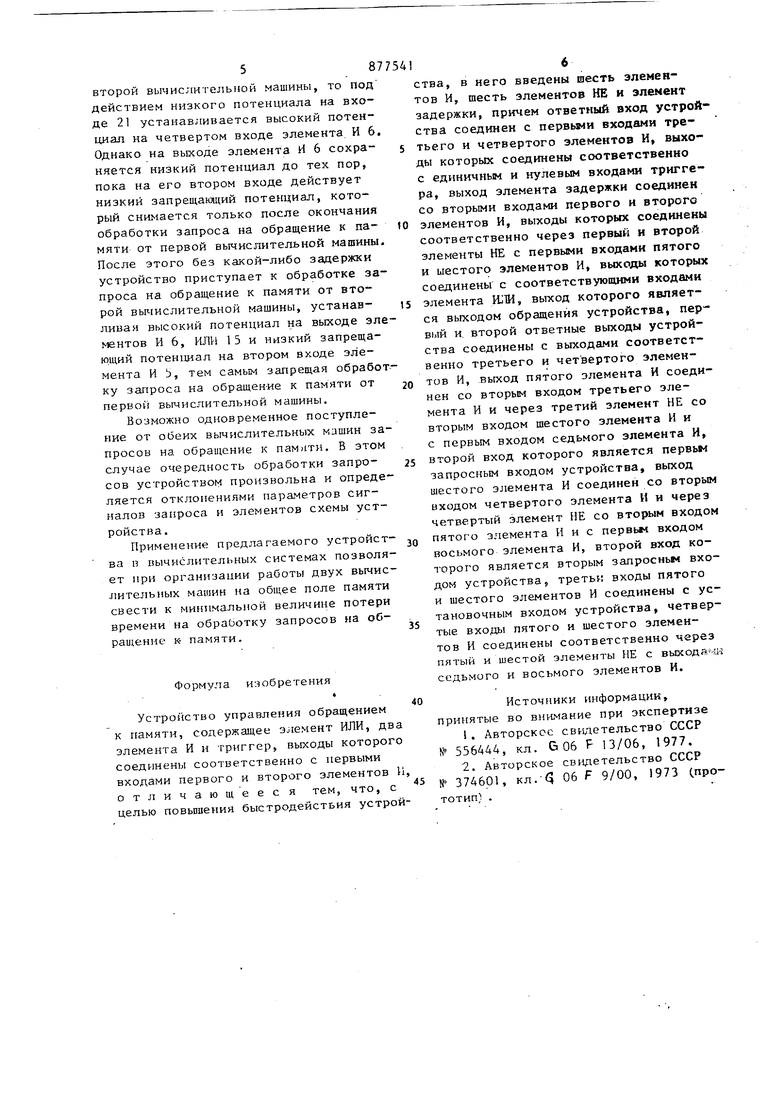

Изобретение относится к вычислител ной технике и может быть использовано в вычислительных системах для организации работы двух вычислительных машин на общее поле памяти. Известно устройство управления обр щением к памяти, содержащее блок управления, распределитель, генератор, узел индикации свободной зоны памяти, узел управления пуском распределителя Q Однако указанное устройство управления обращением к памяти отличается сложностью и большим объемом оборудования, Наиболее близким по технической сущности и достигаемому результату к предлагаемому является устройство, со стоящее из трех триггеров, двух злементов ИЛИ и двух элементов И ,2 Недостатком устройства является низкое быстродействие. Цель изобретения - повышение быстродействия устройства. Указанная цель достигается тем, что в устройство управления обращением к памяти, содержащее элемент R)H, два элемента И и триггер, выходы которого соединены соответственно с. первыми входами первого и второго элементов И, введены шесть элементов И, шесть элементов НЕ и элемент задержки, причем ответный вход устройства соединен с первыми входами третьего четвертого элементов И, выхо- ды которых соединены соответственно с единичньм и нулевьм входами триггера, выход элемента задержки соединен со вторыми входами первого и второго элементов И, выхсды которых соединены соответственно через первый и второй элементы НЕ с первыми входами пятого и шестого элементов И, выходы которых соединены с соответствующими входами элемента ИЛИ, выход которого является выходом обращения устройства, первый и второй ответные выходы устройства соединены с выходами cootветственно третьего и четвертого эле ментов И, выход пятого элемента И соединен со вторым входом третьего элемента И.и через третий злемент НЕ со вторым входом шестого элемента И и с первым входом седьмого элемента И, второй вход которого является первь1М запросным входом устройства, выход шестого элемента И соединен со вторым входом четвертого элемента И и через четвертый элемент НЕ со вторым входом пятого элемента И и с первым входом восьмого элемента И, второй вход которого является вторым запросным входом устройства, третьи вхо ды пятого и шестого элементов И соеди нены с уста.новочньм входом устройства, четвертые входы пятого и шестого элементов И соединены соответственно через пятый и шестой элементы НЕ с выходами седьмого и восьмого элементов И. -На чертеже представлена блок-схема устройства управления обращением к па мяти. Устройство содержит элементы И 1-8 элементы НЕ 9-14, элемент 1-ШИ 5, выход 16 обращения устройства, элемент 17 задержки, ответный вход 18 устройства, триггер. 19, запросные вхо ды 20 и 2 устройства, установочный вход 22 устройства, ответные выхо- . ды 23 и 24 устройства„ Устройство работает следующим образом, В исходном состоянии на вход 18 по ступает низкий потенциал, на входы 20 22 - высокий потенциал. Под действием этих потенциалов и импульса отрицательной полярности, поступающего на вход 22 и являющегося сигналом установки устройства в исходное состояьше в устройстве в исходном состоянии высокий потенциал устанавливается на вы ходах элементов И 7 и 8, элементов НЕ 9, 10, 12 и 13 и на одном (безразлично каксм вьЬсоде триггера 19, а низкий потенциал - на выходе элементов И 1-6, элементов НЕ 1 и 14, элемента ИЛИ 15, элемента 17 задержки, на одном из выходов триггера 19 и на выходах 16, 23 и 24 устройства. При появлении запроса на обращени к памяти от первой вычислительной ма шины низкий потенциал устанавливаетс на входе 2Q, а при появлении запроса на обращение- к памяти от второй вычислительной машины низкий потенциал устанавливается на выходе 21. Пусть первым поступает запрос на обращение к памяти от первой вычислительной машины. Под действием низкого потенциала, установленного на входе 20, на выходе элементов И 7, НЕ 12 устанавливается низкий потенциал, а на выходе эле1- 1ентов И 5, НЕ 11 и ИЛИ 15 высокий потенциал, тем самым на выходе устройства 16 фop -Iиpyeтcя высокий потенодал, который является сигналом обращения к памяти, а на втором входе элемента И 6 устанавливается низкий потенциал, запрещающий обработку запроса на обращение к памяти от второй вычислительной машины. В таком состоянии устройство находится до момента появления на его входе 18 ответного сигнала из памяти в виде импульса положительной полярности, который свидетельствует о том, что. сигнал обращения к памяти принят и вычислительная машина может снять запрос на обраш,ение к памяти. При появлении ответного сигнала на входе 18 на выходе элемента И 3 формируется импульс положительной полярности, который поступает на выход 23 и на вход триггера 19, при этом устанавливается или подтверзкдается высокий потенциал на первом входе элемента И 1. После поступления на второй вход элемента И 1 импул.ьса положительной полярности с выхода элемента 17 задержки на выходе элемента НЕ 9 формируется импульс отрицательной полярности, который поступает на первый вход элемента И 5 и устанавливает на выходах элементов И 5 и 7, НЕ 1 и 12 потенциалы, соответствующие исходному состоян1-ао устройства. Величина задержки ответ-ного сигнала в элементе 17 задержки выбрана такой, что к моменту окончания действия импульса отрицательной полярности на первом входе элемента И 5 первая вычислительная машина снимает запрос на обращение к памяти. С приходом на первый вход элемента И 5 отрицательного импульса в устройстве заканчивается цикл обработки запроса на обращение от первой вычислительной машины и оно готово без задержки приступить к обработке последующих запросов, поступающих от первой или второй вычислительной машины . Если во время обработки устройством запроса на обращение к памяти от первой вычислительной машины поступает запрос на обращение к памяти от 58 второй вычислительной машины, то под действием низкого потенциала на входе 21 устанавливается высокий потенциал на четвертом входе элемента И 6 Однако на выходе элемента И 6 сохраняется низкий потенциал до тех пор, пока на его втором входе действует низкий запрещающий потенциал, который снимается только после окончания обработки запроса на обращение к памяти от первой вьиислительной машины После этого без какой-либо задержки устройство приступает к обработке запроса на обращение к памяти от второй вычислительной машины, устанавливая высокий потенциал на выходе эле ментов И 6, ИЛИ 15 и низкий запрещающий потенциал на втором входе элемента И Ь, тем самым запрещая обработ ку запроса на обращен-ие к памяти от nepaovi вычислительной машины. Возможно одновременное поступление от обеих вычислительных машин запросов на обращение к пам)1ти. В этом случае очередность обработки запросов устройством произвольна и определяется отклонениями параметров сиг- налов запроса и элементов схемы устройства. Применение предлагаемого устройства в вычислительных системах позволяет при организации работы двух вычислительных машин на общее поле памяти свести к минимальной величине потери времени на обработку запросов на обращение к- памяти. Формула изобретения Устройство управления обращением к памяти, содержащее элемент ИЛИ, два элемента И и триггер, выходы которого соединены соответственно с первыми входами первого и второго элементов И отличающеес я тем, что, с целью повьпиения быстродействия устрой ства, в него введены шесть элементов И, шесть элементов НЕ и элемент задержки, причем ответный вход устройства соединен с первьми входами третьего и четвертого элементов И, выходы которых соединены соответственно с единичным и кулевым входами трнггера, выход элемента задержкн соединен со вторыми входами первого и второго элементов И, выходы которых соединены соответственно через первый н второй элементы НЕ с первьми входами пятого и шестого элементов И, выходы которых соединены с соответствующими входами элемента ИЛИ, выход которого является выходом обращения устройства, первый и второй ответные выходы устройства соединены с выходами соответственно третьего и четвертого элементов И, выход пятого элемента И соединен со вторьм входом третьего элемента И и через третий элемент НЕ со вторым входом шестого элемента И и с первым входом седьмого элемента И, второй вход которого является первьм запросным входом устройства, выход шестого элемента И соединен со вторым входом четвертого элемента И и через четвертый элемент НЕ со вторым входом пятого элемента И и с первые входом восьмого элемента И, второй вход которого является вторым запросньи входом устройства, треть1: входы пятого и шестого элементов И соединены с установочным входом устройства, четвертые входы пятого и шестого элементов И соединены соответственно через пятый и шестой элементы НЕ с выходя.чн седьмого и восьмого элементов И. Источники информации, принятые во внимание при экспертизе . Авторское с в tine те лье тв о СССР № 556444, кл. G 06 F 13/06, 1977. 2, Авторское свидетельство СССР № 374601, кл. 06 F 9/00, 1973 {.прототип .

Авторы

Даты

1981-10-30—Публикация

1980-02-26—Подача