мл обрлп((, содержит элемент И-МЕ, формиропатель одиночного импульса и седьмой элемертт НЕ, причем первый- вход запроса обращения устройства нерез формирователь одиночного импульса подключен к первому

пходу элемента , выход которого подключен к второму входу четвертого эле мента И, второй вход запроса обращения устройства через седьмой элемент fiE подключен к второму входу элемента И--НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления обращением к памяти | 1980 |

|

SU877541A1 |

| Многоканальное устройство сопряжения с памятью | 1980 |

|

SU983697A1 |

| Устройство приоритета | 1982 |

|

SU1020828A1 |

| Устройство для сопряжения вычислительной машины с внешним устройством | 1985 |

|

SU1278868A1 |

| Устройство для записи информации в оперативную память | 1990 |

|

SU1751811A1 |

| Устройство адресации для канала прямого доступа к памяти | 1985 |

|

SU1283763A1 |

| Устройство для управления дуплексной системой | 1980 |

|

SU900278A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1310832A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1661837A1 |

| Диспетчер памяти ЭВМ | 1986 |

|

SU1363223A1 |

УСТРОЙСТВО УПРАВЛЕНИЯ ОБРАЩЕНИЕМ К ПА11ЯТИ, содержащее восемь элементов И, шесть элементов НЕ, триггер и элемент ИЛИ, причем первый вход запроса обращения устройства подключен к первому входу первого элемента И, второй вход которого подключен к выходу первого элемента НЕ, а выход через второй элемент НЕ подключен к первому входу второго элемента И, входы с второго по четвертый которого подключены соответственно к выходу третьего элемента НЕ, к установочному входу устройства и к выходу четвертого элемента НЕ, выход второго элемента И подключен к входу первого элемента НЕ и соединен с первым входом элемента ИЛИ, второй вход которого подключен к входу четвертого элемента НЕ и соединен с выходом третьего элемента И, входы с первого по четвертый которого подключены соответственно к выходу пер- . вого элемента НЕ, установочному входу устройства, вьрсоду пятого элемента НЕ и выходу шестого элемента НЕ, вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с вьгходом четвертого элемента НЕ, первый выход управления коммутацией источников запроса устройства подключен к первому входу элемента ИЛИ и соединен с первым входом пятого элемента И, второй вход которого соединен с первым входом шестого элемента И, второй вход которого соединен с вторым входом элемента ИЛИ и подключен к второму выходу управления коммутацией источников запроса устройства, выходы пятого и шестого элементов И подключены соответственно к первому и второму выходам подi тверждения приема запроса устройства, входы установки в 1 и установ Л ки в О триггера соединены соответственно с выходами пятого и шестого элементов И, прямой и инверсный выходы триггера подключены соответственно к первым входам седьмого и восьмого элементов И, вторые входы которых соединены с входом конца цикла ч1 обращения устройства, вход подтвержЗо дения приема запроса, которого соединен с первым входом шестого элемента И, выход седьмого элемента И подключен к входу третьего элемента НЕ и соединен с первым выходом конца цикла обращения устройства, второй выход конца цикла обращения которого соединен с выходом восьмого элемента И и подключен к входу пятого элемента НЕ, выход элемента ИЛИ подключен к выходу запроса обращения устройства, отличающееся тем, чтЪ, с целью повышения надежности путем обеспечения работоспособности при одновременном поступлении запросов

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для организации работы двух вычислительных машин на общее поле памяти.

Цель изобретения - повышение надежности путем обеспечения работоспособности при одновременном поступлении запросов на обращение к памяти.

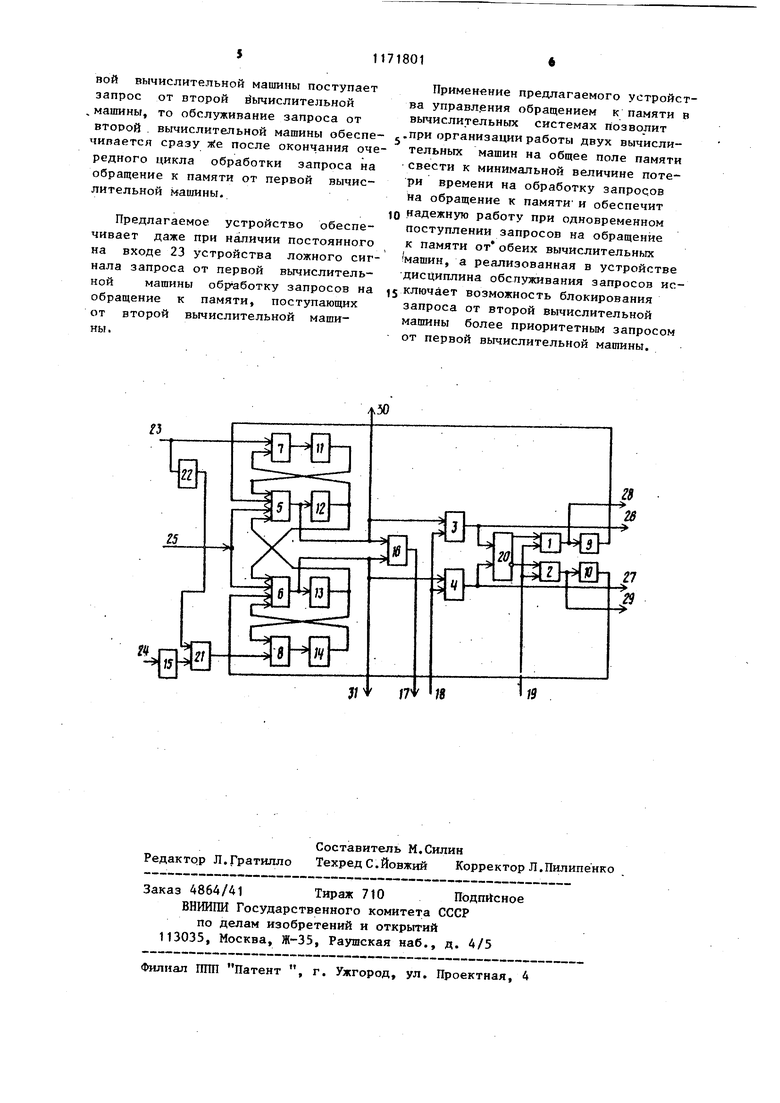

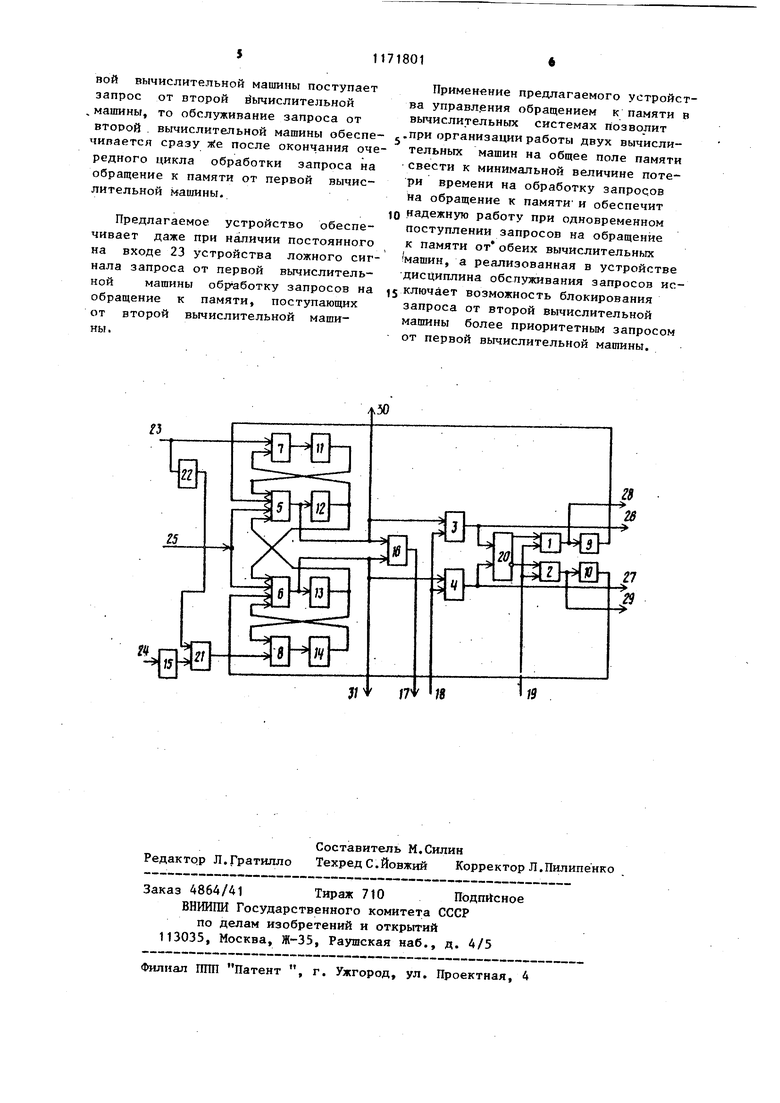

На чертеже изображена блок-схема устройства.

Устройство содержит восемь злементов И 1-8, семь элементов НЕ 9-15, элемент И.ПИ 16, выход 17 запроса обращения, вход 18 подтверждения прима запроса, .вход 19 конца цикла обращения, триггер 20, элемент И-НЕ 21, формирователь 22 оди1 очного импульса, первый и второй входы 23 и 2k запроса обращения, установочный вход 25, первый и второй выходы 26 и 27 подтверждения приема запроса, первьш и второй выходы 28 и 29 конца цикла обращения, первый и второй выходы 30 и 31 управления коммутацией источников запроса.

Устройство управления обращением к ггамяти рабо-тает следующим образом.

В исходном состоянии на входы 18 и 19 устройства поступает низкий потенциал, а на входы 23-25 - высокий потенциал. Под действием этих потенциалов и импульса отрицательной полярности, поступающего на установочный вход 25 устройства и являющегося сигналом установки устройства в исходное состояние, в последнем в исходном состоянии высокий потенциал устанавливается на выходе элементов И 7 и 8, формирователя 22 одиночного импульса, элемента И-НЕ 21, элементов НЕ 9,

10, 12 и 13 и на одном (безразлично каком) выходе триггера 20, а низкий потенциал - на выходе элементов И 1-6, элементов НЕ 11, 14 и 15, элемента ИЛИ 16, на одном из выходов триггера 20 и на выходах 17,26, 27, 2,8, 29, 30 и 31 устройства.

Пр,и появлении запроса на обращение к памяти от первой вычислительной машины низкий потенциал устанавливается на входе 23 устройства, а при появлении запроса на обращение к памяти от второй вычислительной машины - на входе 24 устройства. Пусть первым поступает запрос от первой вычислительной машины. Под действием низкого потенциала, установленного на входе 23, на выходе элементов И 7 и НЕ 12 устанавливается низкий потенциал, а на выходе элементов И 5, НЕ 11 и ИЛИ 16 - высокий потенциал, тем самым на выходе 17 устройства формируется высокий потенциал, который является сигналом обращения к памяти, а на ятором входе элемента И 6 устанавливается низкий потенциал, запрещающий обработку запроса на обращение к памяти от второй вычислительной маишны. На выходе 30 устройства также устанавливается высокий потенциал, который используется для управления коммутатором, обеспечивающим подключение к памяти адресных и числовых шин от первой вычислительной машцны.

В таком состоянии устройство находится до момента появления на входе 18 сигнала сопровождения из памяти в виде импульса положительной полярности, который свидетельствует о том что сигнал обращения к памяти приня и вычислительная машина может снять запрос на обращение к памяти. При появлении сигнала сопровождения на вхо3де 18 устройства на выходе элемента И 1 формируется импульс положител ной полярности, который поступает н выход 26 устройства в виде сигнала сопровождения, разрешающего первой выгшслительной машине снять запрос н обращение к памяти, и. на-единичный вход триггера 20, при этом устанавливается иди подтверждается высокий потенциал на первом входе элемента И 1. Такое состояние устрор)ства Сохраняется до момента прихода на вход 19 сигнала Конец цикла в виде Импульса положительной полярности. При этом на выходе элемента И 1 формируется импульс поло жительной полярности, который посту пает на выход 28 устройства в виде сигнала Конец цикла, а через элемент НЕ 9 в виде импульса отрицатель ной полярности поступает на первый вход элемента И 5 и устанавливает на выходе элементов И 5 и 7, НЕ 11 и 12 и ИЛИ 15 потенциалы, соответствующие исходному состоянию устройства. Тем самым снимается с второго входа элемента И 6 запрет на обработку запросов на обращение к памяти от второй вычислительной машины Величина задержки сигнала Конец цикла относительно сигнала сопровождения такова, что к моменту окончания действия на входе 19 устройства сигнала Конец цикла . первая вычислительная машина снимает запрос на обращение к памяти. С приходом на вход 19 устройства сигнала Конец цикла в устройстве заканчивается цикл обработки запроса на обращение к памяти от первой вычислительной машины и оно готово без задержки приступить к обработке последующих запросов, поступающих от первой или второй вычислительной машины. Если во время обработки устройством запроса на обращение к памяти от первой вычислительной машины поступает запрос на обращение к памяти от второй вычислительной машины, то под действием низкого потенциала на входе 24 устройства устанавливается высокий потенциал на четвертом входе элемента И 6. Однако на выходе элемента И 6 сохраняется низкий потенциал до тех пор, пока на его втором входе действует низкий запрещающий потенциал 014 который снимается только после окончания обработки запроса на обращение к памяти от первой вычислительной машины. После этого без какой-либо задержки устройство приступает к обработке запроса на обращение к памяти от второй вычислительной машины, устанавливая высокий потенциал на выходе элементов И 6 и ИЛИ 16 и низкий запрещающий потенциал на втором входе элемента И 5, тем самьм запрещая обработку запроса на обращение к памяти от первой вычислитель ной машины. При одновременном поступлении от обеих вычислительных машин запросов на обращение к памяти очередность обработки строго определена: первым обрабатывается запрос, на обращение к памяти, поступающий от первой вычислительной машины на вход 23 устройства. Такой режим обслуживания запросов обеспечен благодаря тому, что в момент поступления низкого потенциала на вход 23 устройства на выходе формирователя 22 одиночного импульса вырабатывается импульс отрицательной полярности с длительностью, превышающей время переходных процессов в элементах И 5 и 7, НЕ 11 и 12. Этот импульс поступает на первый вход элемента И-НЕ 21 и блокирует прохождение на вход элемента И 8 сигнала запроса на обращение к памяти от втором вычислительной машины, поступающего в виде низкого потенциала на вход 24 устройства. Запрос от первой вычислительной машины может- поступать и во время обработки устройством запроса на обращение к памяти от второй вычислительной машины, в этом случае вырабатываемый формирователем 22 импульс отрицательной полярности не оказывает никакого влияния на работу устройства. В предложенном устройстве управления обращением к памяти реализованы следующие дисциплины обслуживания: ервый выставил вопрос - первым обслуен; если запросы поступают одновреенно, то первым обслуживается запос от первой вычислительной машины, затем от второй; при постоянно уществующих запросах от обеих вычисительных машин обеспечивается поочеедное обслуживание их 5 если при посоянно существующем запросе от первой вычислительной машины поступает запрос от второй вычислительной

машины, то обслуживание запроса от ВТОРОЙ - вычислительной машины обеспеипается сразу Же после окончания очередного цикла обработки запроса на обращение к памяти от первой вычислительной машины.

Предлагаемое устройство обеспечивает даже при наличии постоянного на входе 23 устройства ложного сигнала запроса от первой вычислительной машины обр аботку запросов на обращение к памяти, поступающих от второй вычислительной машины.

Применение предлагаемого устройства управл.ения обращением к памяти в вычислительных системах позволит .при организации работы двух вычислительных машин на общее поле памяти свести к минимальной величине потери времени на обработку запросов на обращение к памяти и обеспечит

Q надежную работу при одновременном поступлении запросов на обращение к памяти от обеих вычислительных машин, а реализованная в устройстве дисциплина обслуживания запросов ключает возможность блокирования запроса от второй вычислительной машины более приоритетным запросом от первой вычислительной машины.

| СИНХРОНИЗАТОР ДВУХ КОМАНДТ'2СВСОЮЗНД"; iU:.-;::rT.^ri,,.Tr|-K::-'r;.!v^: | 0 |

|

SU374601A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство управления обращением к памяти | 1980 |

|

SU877541A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-08-07—Публикация

1984-02-20—Подача