Изобретение относится.к вычислительной технике и может быть использовано в многомашинных вычислительных комплексах, работающих в реальном масштабе времени.

Целью изобретения является повыше- ние быстродействия.

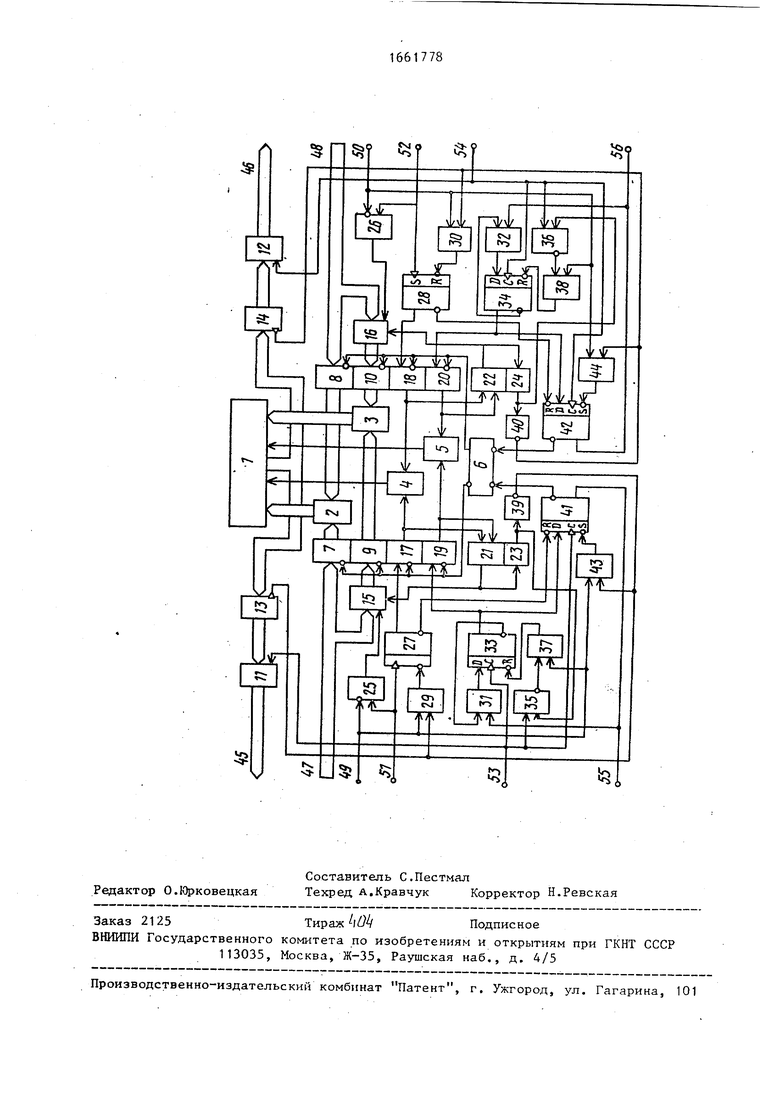

На чертеже представлена структурная схема устройства.

Устройство содержит блок 1 памяти, группы элементов ИЛИ 2 и 3, элементы ИЛИ 4 и 5, триггер 6, группы элементов И 7-12, регистры 13 и 14, счетчики 16, элементы И 17 - 20, эле- менты ИЛИ 21 и 22, элементы 23 и 24 задержки, элементы И 25 и 26, триггеры 27 и 28, элементы И 29 - 32, триггеры 33 и 34, элементы И-НЕ 35 и 36, элементы И 37 и 38, элементы НЕ 39 и 40, триггеры 41 и 42, элементы И 43 и 44, выходы 45 и 46, входы 47 - 54 и выходы 55 и 56.

Устройство работает следу оим образом.

В исходном состоянии триггеры 41 и 42 находятся в единичном состоянии, триггеры 27, 28, 33 и 34 - в нулевом состоянии, триггер 6 - в неопределенном состоянии (на единичном и нулевом выходах - сигнал логической 1).

Рассмотрим режим обращения одной ЦВМ.

Для выполнения операции обращения к блоку 1 памяти необходимо выполнить два такта. Любая операция обращения поступает в адресной части (первый такт). На вход 47 поступает адрес ячейки блока 1 памяти, к которой необходимо обратиться, после чего на входе 51 устанавливается сигнал Зп. На входе 49 сигнал отсутствует, вследствие чего на выходе элемента И 25 присутствует сигнал логической 1, по которому проводится .запись адреса ячейки блока 1 памяти, к которой необходимо обратиться, в счетчик 15.

(Л

О5 05

1 v

оо

Во втором такте на входе 49 присутствует сигнал Зпр, который запрещает запись данных в счетчик 15.

В случае операции Запись сигнал на входе 51 передним фронтом устанавливает триггер 27 в единичное состояние, сигнал логического О с нулево- tfo выхода триггера 27 сбрасывает tpnrrep 41 в нулевое состояние, триггер 6 устанавливается в единичное сос- (ояние и разрешает прохождение сигналов через группы элементов И 7 и 9, Элементы И 17 и 19. На блок 1 памяти поступает сигнал записи через элементы И 17 и ИЛИ 4, адрес ячейки через группы элементов И 9 и ИЛИ 3, данные через группы элементов И 7 и ИЛИ 2, Сигнал с выхода элемента И 17 подается на вход элемента , с выхода которого подается на вход элемента 23 задержки, время задержки которого равно времени срабатывания блока 1 памяти. Сигнал с выхода элемента 23 задержки поступает на вход элемента НЕ 39, по выходному сигналу которого записываются данные с блока 1 памяти в регистр 13, но отсутствие сигнала Чт на входе 53 запрещает передачу данных через группу элементов на входе 53 запрещает передачу данных через группу элементов И 11 на выход 45, триггер 27 устанавливается в О, а триггер 41 - в 1, что приводит к установке на выходе 55 ответного сигнала, информирующего ЦВМ о завершении цикла обмена, а также к установке триггера 6 в исходное неопределенное состояние, что сни мает сигналы с выхода групп элементов- И 7 и элемента И 17. Далее ЦВМ снимает сигнал с входа 51 и после этого сигнал с входа 49.

Перед началом операции Чтение все триггеры находятся в исходном состоянии. ЦВМ выдает на вход 53 сиг- нал высокого уровня. Этим сигналом триггер 33 устанавливается в 1, триггер 41 - в О, что приводит к установке триггера 6 в 1 и разрешает прохождение сигналов через группу элементов И 9 и элемент И 19. Далее ЦВМ производит обращение к ячейке блока 1 памяти по адресу, записанному в счетчике 15. Сигнал с выхода элемента И 19 подается через элементы ИЛИ 21 и элемент 23 задержки на вход элемента НЕ 39, по выходному сигналу которого переписываются дан

0

5

0

5

0

5

0

5

ные с блока 1 памяти в регистр 13 и через группу элементов И 11 передаются в ЦВМ. Триггер 41 устанавливается в единичное состояние, что приводит в установке триггера 6 в исходное состояние, на выходе 55 появляется ответный сигнал, информирующий ЦВМ о завершении обращения. Далее ЦВМ снимает сигнал с входа 53 и после этого с входа 49.

Режим последовательного обращения двух ЦВМ.

Этот режим характеризуется последовательным обращением к устройству двух ЦВМ на отрезке, равном времени выполнения операции ввода-вывода процессора, если одна ЦВМ производит операцию ввода-вывода с устройством, а другая ЦВМ также обратилась к устройству .

Рассмотрим работу устройства при обращении к нему второй (правой) ЦВМ. Первый адресный такт происходит аналогично описанному. При этом в счетчик 16 записывается адрес, по которому требуется обращение к блоку 1 памяти. Во втором такте сигнал с входа 52 или 54 устанавливает триггер 42 в О, что приводит к установке триггера 6 в нулевое состояние. Нулевой сигнал с единичного выхода триггера 6 разрешает прохождение данных, адреса и управляющих сигналов на блок 1 памяти. По завершении обмена с устройством второй ЦВМ триггер 6 устанавливается в исходное состояние, устройство готово для обращения первой ЦВМ.

В данном случае возможно снятие сигналов с входа 51 или 53 от первой ЦВМ до момента окончания обращения к блоку памяти. Рассмотрим работу устройства в данной ситуации. В случае если (со стороны первой ЦВМ) на вход 51 выставлен сигнал Зп, то после его снятия до получения сигнала Отв триггер 27 остается в единичном состоянии, а триггер 41 - в нулевом. Сигнал на выходе 55 Отв остается в пассивном (нулевом) состоянии. По окончании обращения к блоку 1 памяти второй ЦВМ происходит запись в блок 1 памяти со стороны первой ЦВМ аналогично с циклом записи при обращении одной ЦВМ (предполагается, что на входе 47 присутствуют записываемые данные), По окончании операции триггеры 27 и 41 устанавливаются в начальное состояние.

516

В случае операции Чтение со стороны первой ЦВМ, если сигнал на входе 53 снимается до получения сигнала Отв, то триггер 33 остается в единичном, а триггер 41 в нулевом состоянии, сигнал Отв не выставляется. После окончания обращения к блоку 1 памяти второй ЦВМ происходит чтение ячейки памяти по адресу, находящемуся в счетчике 15, данные записываются в регистр 13, на входе 55 появляется сигнал Отв, сообщающий первой ЦВМ наличие считанных данных в регистре 13. ЦВМ выставляет на вход 53 сигнал Чт. После его прихода данные с регистра 13 через открытую группу элементов И 11 поступают на вход ЦВМ. Триггер 33 сбрасывается в О, после этого снимается сигнал Зпр с входа 49, что является признаком завершения операции обмена с устройством. Это позволяет, в случае если данные не были считаны за одно обращение, не снимая запросного сигнала, производить чтение, обращаясь лишь к регистру 13 независимо от обращения втог рой ЦВМ.

В случае одновременного обращения к устройству двух ЦВМ первые такты обращения - занесение адресов в счетчики происходят одновременно и независимо. Во вторых тактах каждая ЦВМ выставляет сигнал Зпр и сигналы Зп или Чт на входах устройства одновременно. При этом триггер 6 устанавливается в одно из двух состояний - нулевое или единичное, что разрешает работу с устройством первой ил второй ЦВМ соответственно. Работа с другой ЦВМ будет разрешена после выставления ответного сигнала первой. Задержка на обслуживание обращения другой ЦВМ определяется временем срабатывания памяти.

Снятие сигнала с выхода элемента ИЛИ 21 или 22 приводит к увеличению числа, хранимого в счетчике 15 и 16, на единицу, что позволяет при занесении или считывания массивов информации заносить в счетчик начальный адрес массива и в дальнейшем, не снимая запросного сигнала, производить запись или считывание, не повторяяя первого адресного такта. Формула изобретения

Устройство для сопряжения двух ЦВМ с общей памятью, содержащее блок па86

мяти, шесть групп элементов И, две группы элементов ИЛИ, два счетчика, три триггера, два регистра, четыре элемента ИЛИ, восемь элементов И, два элемента задержки, причем первые входы элементов И первой группы соединены с группой информационных вхог дов первого счетчика и образует группу входов устройства для подключения к группе информационных выходов первой ЦВМ, первые входы элементов И второй группы соединены с группой информационных входов второго счетчика

и образуют группу входов устройства для подключения к группе информационных выходов второй ЦВМ, выходы эле-, ментов И третьей и четвертой групп образуют группы выходов устройства

для подключения к группам информационных входов первой и второй ЦВМ соответственно, при этом первые входы элементов И третьей и четвертой групп соединены с группами информационных выходов первого и второго регистров соответственно, группы информационных входов которых соединены с группой информационных выходов блока памяти, группа адресных входов которого соединена с выходами элементов ИЛИ первой группы, первые и вторые входы которых соединены с. выходами элементов И пятой и шестой групп соответственно, первые входы которых

соединены с группами выходов первого

и второго счетчиков соответственно, выходы элементов И первой и второй групп соединены с первыми и вторыми входами элементов ИЛИ -второй группы,

выходы которых соединены с группой информационных входов блока памяти, отличающееся тем, что, с целью повышения быстродействия, в устройство введены шесть элементов И,

четыре триггера, два элемента И-НЕ9 два элемента НЕ, причем первый вход первого элемента И соединен, с первыми входами второго, третьего, четвертого элементов И и является входом устройства для подключения к выходу запроса первой ЦВМ, второй вход первого элемента И соединен с входом установки первого триггера и является входом устройства для подключения к выходу

записи первой ЦВМ, синхровход второго триггера соединен с вторыми входами элементов И третьей группы, с первым входом первого элемента И-НЕ, с синхровходом третьего триггера и яв

ляется входом устройства для подключения к выходу чтения первой ЦВМ, единичный выход третьего триггера соединен с первым входом пятого эле« мента И и является выходом устройст- ва для подключения к входу ответа первой ЦВМ, первый вход шестого элемента И соединен с первыми входами седьмого, восьмого, девятого элементов И и является входом устройства для подключения к выходу запроса второй ЦВМ, второй вход шестого элемента И.соединен с входом установки четвертого триггера и является входом , устройства для подключения к выходу Записи второй ЦВМ, синхровход пятого Триггера соединен с вторыми входами Элементов И четвертой группы, с первым входом второго элемента И-НЕ, с синхровходом шестого триггера и является входом устройства для подключе- .. ния к выходу чтения второй ЦВМ, едиг ничный выход шестого триггера соединен с первым входом десятого элемен- та И и является выходом устройства для подключения к входу ответа второй ЦВМ, при этом вход сброса третьего триггера соединен с нулевым выходом первого триггера, вход сброса кото- рого соединен с выходом второго элемента И, второй вход которого соединен с входом записи первого регистра, с выходом первого элемента НЕ и с вторым входом четвертого элемента И, выход которого соединен с входом уста- новки третьего триггера, нулевой вы-, ход которого соединен с входом установки седьмого триггера, нулевой выг-.

ход которого соединен с вторыми входа

„

ми элементов И первой, пятой групп и

с первыми входами одиннадцатого и двенадцатого элементов И, единичный выход первого триггера соединен с вторым входом одиннадцатого элемента И, выход .которого соединен с первым входом первого элемента ИЛИ и с первым входом второго элемента ИЛИ, выход которого соединен с входом записи блока памяти, вход чтения которого соединен с выходом третьего элемента ИЛИ, первый вход которого соединен с выходом двенадцатого элемента II и с вторым входом первого элемента ИЛИ, выход которого соединен со счетным входом первого счетчика и с входом первого элемента задержки, выход ко0

5

5 5 ,0 45

0

5

торого соединен с входом первого элемента НЕ и с вторым входом первого элемента И-НЕ, выход которого соеди нен с вторым входом третьего элемента И, выход которого соединен с входом сброса второго триггера, информационный вход которого соединен с выходом пятого элемента И, второй вход которого соединен с нулевым выходом второго триггера, единичный выход которого соединен с вторым входом двенадцатого элемента И и с информационным входом третьего триггера, вход записи второго регистра соединен с вто-. рыми входами восьмого, девятого элементов И и с выходом второго элемента НЕ, вход которого соединен с выходом второго элемента задержки и с вторым входом второго элемента И-НЕ, выход которого соединен с вторым входом седьмого элемента И, выход которого соединен с входом сбр.оса пятого триггера, нулевой выход которого соединен с вторым входом десятого элемента И, выход которого соединен с информационным входбм пятого триггера, единичный выход которого соединен с информационным входом шестого триггера и с первым входом тринадцатого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ и с первым входом четвертого элемента ИЛИ, второй вход которого соединен с вторым входом второго элемента ИЛИ и с выходом четырнадцатого элемента И, первый вход которого соединен с единичным выходом четвертого триггера, вход сброса и нулевой выход которого соединены соответственно с выходом восьмого элемента И и с входом сброса шестого триггера, вход установки и нулевой выход которого соединены соответственно с выходом девятого элемента И и с входом сброса седьмого триггера, единичный выход которого соединен с вторыми входами элементов И второй, шестой групп и с вторыми входами тринадцатого и четырнадцатого элементов И, выход четвертого . элемента ИЛИ соединен с входом второго элемента задержки и со счетным входом второго счетчика, входы записи первого и второго счетчиков соединены с выходами первого и шестого элементов И соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух ЦВМ с общей памятью | 1986 |

|

SU1399750A1 |

| Устройство для ввода информации | 1987 |

|

SU1432544A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| Устройство для вывода информации | 1984 |

|

SU1180876A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1221666A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для коррекции программ | 1989 |

|

SU1647574A1 |

Изобретение относится к вычислительной технике и может быть использовано в многомашинных вычислительных комплексах в реальном масштабе времени. Целью изобретения является повышение быстродействия. Устройство содержит блок памяти, два регистра, два счетчика, семь триггеров, шесть групп элементов И, две группы элементов ИЛИ, четырнадцать элементов И, четыре элемента ИЛИ, два элемента И - НЕ, два элемента НЕ, два элемента задержки. 1 ил. е,

| Двухпортовое устройство сопряжения в вычислительной системе | 1982 |

|

SU1156080A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения двух ЦВМ с общей памятью | 1986 |

|

SU1399750A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-07—Публикация

1989-07-18—Подача